Abstract

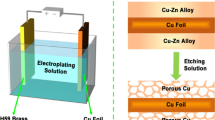

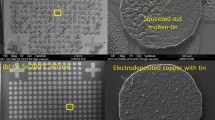

Electrodeposited copper (Cu)-tin (Sn) based solid–liquid interdiffusion (SLID) bonding is becoming popular in wafer-scale packaging of inertial Micro-Electro-Mechanical-Systems (MEMS) sensors due to its inherent advantages of lower cost, low processing temperatures and less stringent surface uniformity requirements. However, eliminating micron-size voids within intermetallic compounds (IMCs) and bond interfaces has remained a challenging task. The present study focuses upon IMC growth and void formation at varying temperatures and times. Stacks of varying thickness of Cu and Sn were fabricated by electrodeposition, and the samples were annealed at temperature ranging up to 300°C. Scalloped shaped Cu6Sn5 (η-phase) and comparatively uniform Cu3Sn (ε-phase) intermetallics were observed. Experimental results show that the growth of metastable Cu6Sn5 dominates IMC formation at lower temperatures but as temperature increases, Cu3Sn dominates over the Cu6Sn5 growth. This IMC growth transition from Cu6Sn5 dominant growth to Cu3Sn dominant growth depends on the annealing temperature and has a critical time duration. The IMC thicknesses are compared with those obtained by numerical simulation models. For given annealing temperatures, intermittent voids formed in the IMC layers show increasing size and decreasing void fraction trends with increasing annealing times. The results suggest that Cu-Sn SLID bonding performed at 275°C yields reliable bonding since the void growth is minimal. Based on these results, a test vehicle containing a kelvin structure and daisy chains (having large number of Cu-Sn bonded structure), was fabricated, resulting in electrical resistances lower than 30 m-ohms and 6 ohms, respectively.

Article PDF

Similar content being viewed by others

Avoid common mistakes on your manuscript.

References

M. Esashi, J. Micromech. Microeng. 18, 073001 (2008).

C. Ko and K. Chen, Microelectron. Reliab. 50, 481 (2010).

J.F. Li, P.A. Agyakwa, and C.M. Johnson, Acta Mater. 59, 1198 (2011).

S. Marauska, M. Claus, T. Lisec, and B. Wagner, Microsyst. Technol. 19, 1119 (2013).

A. Munding, H. Hubner, A. Kaiser, S. Penka, P. Benkart, and E. Kohn, Wafer Level 3-D ICs Process Technology, ed. C.S. Tan, R.J. Gutmann, and L.R. Reif (New York: Springer, 2008), p. 131.

C. Yuhan and L. Le, J. Semicond. 30, 086001-1 (2009).

H. Liu, G. Salomonsen, K. Wang, K.E. Aasmundtveit, and N. Hoivik, IEEE Trans. Pack. Manuf. 1, 1350 (2011).

H. Xu, A. Rautiainen, V. Vuorinen, E. Österlund, T. Suni, H. Heikkinen, P. Monnoyer, and M. Paulasto-KrÖckel, in ESTC Conference Proceedings (2014), pp. 1–5.

B. Lee and J. Yoon, J. Electron. Mater. 47, 430 (2018).

T. Laurila, V. Vuorinen, and J.K. Kivilahti, Mater. Sci. Eng. R 49, 1 (2005).

H. Liu, K. Wang, K.E. Aasmundtveit, and N. Hoivik, J. Electron. Mater. 41, 2453 (2012).

H. Huebner, S. Penka, B. Barchmann, M. Eigner, W. Gruber, M. Nobis, S. Janka, G. Kristen, and M. Schneegans, Microelectron. Eng. 83, 2155 (2006).

T.T. Luu, A.N.I. Duan, K.E. Aasmundtveit, and N. Hoivik, J. Electron. Mater. 42, 3582 (2013).

B. Balakrisnan, C.C. Chum, M. Li, Z. Chen, and T. Cahyadi, J. Electron. Mater. 32, 166 (2003).

N.S. Bosco and F.W. Zok, Acta Mater. 52, 2965 (2004).

A. Paul, C. Ghosh, and W.J. Boettinger, Metall. Mater. Trans. A 42, 952 (2011).

W. Kern, J. Electrochem. Soc. 137, 1887 (1990).

J. Yu and J.Y. Kim, Acta Mater. 56, 5514 (2008).

G. Ross, V. Vuorinen, and M. Paulasto-Kröckel, J. Alloys Compd. 677, 127 (2016).

L. Yin and P. Borgesen, J. Mater. Res. 26, 455 (2011).

A. Paul, J. Mater. Sci. Mater. Electron. 22, 833 (2011).

W. Yang and R.W. Messler, J. Electron. Mater. 23, 765 (1994).

G. Ross, H. Xu, V. Vuorinen, and M. Paulasto-kröckel, in 5th Electronics System-Integration Technology Conference (ESTC) Proceedings (2014), pp. 1–3.

S. Kumar, J. Smetana, D. Love, J. Watkowski, R. Parker, and C.A. Handwerker, J. Electron. Mater. 40, 2415 (2011).

Acknowledgments

Authors would like to acknowledge the financial support from Industrial Research and Consultancy Centre (IRCC), IIT-Bombay, under the research Grant 15IRCCSG002. Authors would also like to thank Mr. Ronak Gupta for support in MATLAB based graphic user interface (GUI) development.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kannojia, H.K., Sharma, S.K. & Dixit, P. Void Formation and Intermetallic Growth in Pulse Electrodeposited Cu-Sn Layers for MEMS Packaging. J. Electron. Mater. 47, 7386–7400 (2018). https://doi.org/10.1007/s11664-018-6679-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-018-6679-6