Abstract

An electrostatically doped (ED) tunnel carbon nanotube field-effect transistor (CNTFET)-based six-transistor (6T) static random-access memory (SRAM) cell is designed and simulated in HSPICE. The performance of the ED tunnel CNTFET 6T SRAM cell is analyzed based on various figures of merit (FOMs), viz. the read/write noise margin, power dissipation, and read/write delay. Simulation results for the ED tunnel CNTFET-based 6T SRAM are compared with those for a conventional CNTFET-based 6T SRAM cell, revealing that the former shows improved FOMs without losing stability. The read noise margin is improved by 9.2% and 7.5% at VDD of 0.9 V and 0.5 V, while the write noise margin is improved by 16% and 14% at VDD of 0.9 V and 0.5 V, respectively. The power dissipation is reduced by 9 pW at VDD of 0.9 V and by 4 pW at VDD of 0.5 V. The results demonstrate the stability of the proposed ED tunnel CNTFET SRAM for low-power applications.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Power consumption due to leakage in memory is a major issue in nanometer-scale technologies. As most of the area of a processor chip is occupied by SRAM, its dissipation is significant. Thus, extensive research has been performed to develop low-power on-chip memory to reduce the total power dissipation. The dynamic power has a quadratic dependence on the supply voltage. Hence, to reduce the dynamic power dissipation, the supply voltage must be scaled down. However, according to the International Technology Roadmap for Semiconductors (ITRS) standard, along with the supply voltage, the threshold voltage must also be scaled down. To reduce the threshold voltage, thinner gate oxide can be employed, but this also increases the gate oxide tunneling and subthreshold leakage currents [1,2,3,4,5,6]. To address this issue, several materials and new devices have been explored to provide steep subthreshold slope (SS) and lower leakage current. A steep subthreshold slope increases the switching speed of the transistor and enables low-voltage operation. The tunnel CNTFET offers a steep subthreshold slope and thus can work efficiently at low voltages [7, 8]. The structure of the tunnel CNTFET is similar to that of an Si-based tunnel FET, with the only difference being the channel material [9, 10]. The best feature of CNTs is their variable bandgap, which makes them suitable for use in various applications [11]. Conventional doping is not possible in tunnel CNTFETs, because if any carbon atom is replaced with a dopant, the overall properties of the CNT change. Therefore, fabrication of tunnel CNTFETs is a difficult task with considerably higher costs [12]. To reduce this difficulty in fabrication, a dopingless approach was introduced in 2005 [13, 14]. This technique offers the supplementary advantage of dynamic configuration [15, 16], allowing the same device to be used as both n-type and p-type by reversing the bias applied at the polarity gates (PGs). An overview of work done on such electrostatically doped devices is presented in Ref. [17].

In the literature, SRAM circuits have been designed using both complementary metal–oxide–semiconductor (CMOS) and conventional CNTFET technologies [14, 18,19,20,21]. Herein, an electrostatically doped tunnel CNTFET-based SRAM cell is subjected to exhaustive analysis to determine the impact on its performance parameter, viz. read/write noise margin, power dissipation, and read/write delay. The I–V transfer characteristics of the ED tunnel CNTFET are compared with those of a conventionally doped CNTFET to confirm its suitability for use in circuit applications. The 6T SRAM cell is designed and simulated in HSPICE using both conventionally doped and ED tunnel CNTFETs. The conventional CNTFET 6T SRAM cell is designed using the model file from Stanford University [22], whereas the proposed ED tunnel CNTFET-based SRAM cell is designed using the model in Ref. [23], revealing improvements compared with the conventional CNTFET-based SRAM in terms of the power dissipation, read/write delay, and static noise margins (SNMs) without losing stability.

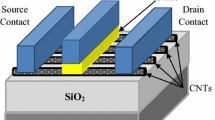

2 ED tunnel CNTFET

A schematic of the ED tunnel CNTFET is shown in Fig. 1, with two polarity gates (PG-1 at the source region, PG-2 at the drain region) and primary gates at the top and bottom. The doping is controlled electrostatically by varying the voltages applied at the polarity gates PG-1 and PG-2. The polarity gates help to create a p-region at the drain when applying a polarity voltage of −0.75 V and an n-region at the source side when applying a polarity voltage of 0.75 V. The purpose of the primary gates is to control the flow of current. The device configuration can thus be changed from p-type to n-type by reversing the voltages applied at the polarity gates. Figure 2 shows the IDS–VGS characteristics of the n-type (Fig. 2a) and p-type (Fig. 2b) ED tunnel and conventionally doped CNTFETs [8, 23]. The simulation results for both models show that the ED tunnel CNTFET exhibits improved IDS–VGS performance compared with the conventionally doped CNTFET in terms of low OFF-current, steep SS, and high ON/OFF-current as compared with the conventional CNTFET (Table 1).

The IDS–VGS characteristics of the ED tunnel CNTFET [23]

3 CNTFET and ED tunnel CNTFET 6T SRAM cells

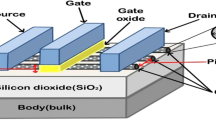

The basic 6T SRAM cell consists of two cross-coupled inverter pairs in which the output node of one inverter pair is connected to the input node of the second inverter pair. The inverter pairs M1, M2 and M3, M4 are further connected to two access transistors, M5 and M6. The read or write operation is performed by applying appropriate voltages to the word lines (WL) and bit lines (BL) of the access transistors. The gate terminals of these access transistors are connected to the WL, while the drain terminals are connected to the bit lines (BL and BLB). The original and complementary data values are stored at the nodes Q and QB. A schematic diagram of the 6T SRAM cell using conventional CNTFETs is shown in Fig. 3.

Figure 4 shows a schematic diagram of the 6T SRAM cell using ED tunnel CNTFETs, adopted from Ref. [24] by replacing all the Si-based TFETs with ED tunnel CNTFETs. It includes both inward and outward access transistors. The inward access configuration is adopted to obtain an acceptable read noise margin for the device, whereas the outward access configuration is used to increase the write noise margin of the device. The inward access transistor couples the internal node Q to BL, while the outward access transistor couples the internal node Q to BLB. The write enable signal (WRA) is used to provide virtual grounding to an inverter pair in order to obtain an acceptable write noise margin. The conventional CNTFET-based 6T SRAM cell is designed and simulated as reported in Ref. [18], then to further reduce fabrication issues, the novel dopingless tunnel CNTFET is used to design the model for the 6T SRAM design. The cell design of the 6T SRAM using ED tunnel CNTFETs is the same as that of the conventional SRAM cell but with additional polarity gate biases (BL and BLB), both of which are connected to node Q through M5 and M6. The voltage applied at the polarity gates is VPG_p (for p-type) = −0.75 V and VPG_p (for n-type) = 0.75 V.

4 The read operation in SRAM

For the read operation, both bit lines (BL and BLB) are precharged to the supply voltage, i.e., VDD, while the word line is activated. If the value stored at Q is 1, then it will remain at 1 because a discharge path is absent. If the storage node (Q) is storing a value of 0, then it will immediately switch to an intermediate voltage because a current path now exists between the bit line and ground. The value of this intermediate voltage is determined by the voltage dividers, which are constructed by using one access transistor and one pull-down transistor. The intermediate voltage should not cross the threshold voltage of the inverter, otherwise the voltage at the internal node will flip, which is undesired. So, for a successful read operation, the pull-down transistor must be stronger than the access transistor. In other words, the cell ratio (β) should be high, as expressed in Eq. (1). The difference between the bit line (BL) and Q is sensed by the sense amplifier and will indicate that the read 0 operation has been performed. The read operation of the 6T SRAM cell using ED tunnel CNTFETs is similar to that for the 6T CNTFET SRAM cell. During the read operation, WRA is driven to ground and the read current path is the same as illustrated in Fig. 5.

5 The write operation in SRAM

The write operation in the ED tunnel CNTFET SRAM cell is shown in Fig. 6. The write operation is performed through the access transistors M1 and M5. The voltage levels are applied to the bit lines according to the data that is to be written.

To write a value of 1 onto the internal node Q, BL and BLB are raised to VDD, then the word line is activated. To weaken the first inverter, WRA is raised simultaneously as well. The WRA signal is sent in the form of a short pulse whose magnitude is less than the supply voltage but greater than the ground voltage. When Q settles to 1 and QB settles to 0, WRA is linked to the ground line, which enables cross-coupling between the two signals. Figure 6a shows the write 1 operation.

To write a value of 0 onto Q, both bit lines are pulled to the ground voltage and the access transistors are activated. WRA is raised to break the cross-coupling of the inverters. Q is discharged to 0 by the access transistor M6. Figure 6b shows the write 0 operation.

6 SRAM performance parameters

The performance of SRAM is generally compared on the basis of the read and write margins, power dissipation, and read and write delays.

6.1 Read SNM

The read noise margin is calculated using the read voltage transfer characteristic (VTC), which is measured by sweeping the direct-current (DC) voltage at node Q while monitoring the voltage at node QB. It is then calculated based on the largest square that fits within the lobes of the read butterfly curve. The read margin of the conventional CNTFET SRAM cell and the proposed ED tunnel CNTFET SRAM cell at VDD of 0.9 V is illustrated in Fig. 7a, b, and at VDD of 0.5 V in Fig. 8a, b. Note that the VTC of the proposed structure is very sharp compared with that of the conventional CNTFET SRAM, leading to an enhancement of the read margin. A 9.2% improvement in the read margin is seen at 0.9 V, and 7.5% at 0.5 V.

6.2 Write SNM

The write noise margin is measured based on the smallest square that fits within the lower part of the VTC between Q and QB under the condition of WL = VDD, BL = 0, and BLB = VDD [25]. The write margin of the conventional CNTFET 6T SRAM and ED tunnel CNTFET 6T SRAM at VDD of 0.9 V is shown in Fig. 9a, b, and at VDD of 0.5 V in Fig. 10a, b. The ED tunnel CNTFET 6T SRAM exhibits a sharp transition in the VTC, which improves the write margin of the cell by 16% at VDD = 0.9 V and by 14% at VDD = 0.5 V.

Tables 2 and 3 show a comparison of the performance parameters of the proposed ED tunnel CNTFET versus the conventional CNTFET SRAM at VDD of 0.9 V and 0.5 V. The calculated values of the read noise margin, write noise margin, and static power dissipation are improved in the ED tunnel CNTFET SRAM cell. The power reduction for a single SRAM cell is 9 pW at 0.9 V and 4 pW at 0.5 V. Such power reductions are significant for large memory applications, showing that the ED tunnel CNTFET SRAM is suitable for use in low-power applications.

Figure 11a shows the read noise margin for various VDD values; on increasing the value of VDD, the proposed structure shows an improvement in the read margin. Figure 11b shows the write noise margin at various VDD values, revealing an increase with higher VDD. The proposed ED tunnel CNTFET SRAM cell shows a lesser improvement of the read noise margin compared with the write noise margin, for the reason that only one access transistor is used to conduct the read operation whereas the other access transistor does not conduct due to its unidirectionality.

6.3 Delay

A comparison of the read and write delays of the proposed ED tunnel CNTFET SRAM cell with the conventional CNTFET SRAM cells at VDD = 0.5 V is presented in Table 4. It is observed that both the read and write delays are reduced in the proposed ED tunnel CNTFET 6T SRAM as compared with the conventional CNTFET 6T SRAM, when using the same feature size. Meanwhile, the write delay of the proposed ED tunnel CNTFET 6T SRAM is 31% and 25% shorter compared with the conventional CNTFET 6T SRAM when writing 0 and 1, respectively. The read delay is also reduced by 16% compared with the conventional CNTFET 6T SRAM cell.

7 Conclusions

A 6T SRAM cell using ED tunnel CNTFETs is designed and investigated. The results show that the ED tunnel CNTFET 6T SRAM cell exhibits lower power consumption, shorter delays, and higher read and write noise margins compared with the CNTFET 6T SRAM. The ED tunnel CNTFET-based 6T SRAM shows a read delay of 0.35 ps and a write delay of 2.43 ps, being 16% and 25% shorter than those of the CNTFET 6T SRAM, and moreover consumes 20% less power. This study finds a major power reduction over the whole voltage range, making the ED tunnel CNTFET an appropriate candidate for use in the design of low-power SRAM.

References

Subramanyam, J.B.V., Syed Basha, S.: Design of low leakage power SRAM using multithreshold technique. In: Intelligent Systems and Control (ISCO), 2016 10th International Conference on. IEEE (2016)

Chen, X., Peh, L.-S.: Leakage power modeling and optimization in interconnection networks. In: Low Power Electronics and Design, 2003. ISLPED’03. Proceedings of the 2003 International Symposium on. IEEE (2003)

Flautner, K., Kim, N.S., Martin, S., Blaauw, D., Mudge, T.: Drowsy caches: simple techniques for reducing leakage power. In: Computer Architecture, 2002. Proceedings. 29th Annual International Symposium on. IEEE (2002)

Kanda, K., Sadaaki, H., Sakurai, T.: 90% write powersaving SRAM using sense-amplifying memory cell. IEEE J. Solid-State Circuits 39(6), 927–933 (2004)

Yamaoka, M., Maeda, N., Shinozaki, Y., Shimazaki, Y., Nii, K., Shimada, S., Yanagisawa, K., Kawahara, T.: Low-power embedded SRAM modules with expanded margins for writing. In: Solid-State Circuits Conference, 2005. Digest of Technical Papers. ISSCC. 2005 IEEE International. IEEE (2005)

Li, H., Huang, P., Gao, B., Chen, B., Liu, X., Kang, J.: A SPICE model of resistive random access memory for large-scale memory array simulation. IEEE Electron Device Lett. 35(2), 211–213 (2014)

Frégonèse, S., Maneux, C., Zimmer, T.: Implementation of tunneling phenomena in a CNTFET compact model. IEEE Trans. Electron Devices 56(10), 2224–2231 (2009)

Bala, S., Khosla, M.: Design and analysis of electrostatic doped tunnel CNTFET for various process parameters variation. J. Superlattices Microstruct. 124, 160–167 (2018)

Bandaru, P.R.: Electrical properties and applications of carbon nanotube structures. J. Nanosci. Nanotechnol. 7(4–5), 1239–1267 (2007)

Kumar, S., Raj, B.: Compact channel potential analytical modeling of DG-TFET based on evanescent-mode approach. J. Comput. Electron. 14(3), 820–827 (2015)

Lukić, B., Seo, J.W., Bacsa, R.R., Delpeux, S., Béguin, F., Bister, G., Fonseca, A., Nagy, J.B., Kis, A., Jeney, S., Kulik, A.J.: Catalytically grown carbon nanotubes of small diameter have a high Young’s modulus. Nano Lett. 5(10), 2074–2077 (2005)

Appenzeller, J., Lin, Y.M., Knoch, J., Chen, Z., Avouris, P.: Comparing carbon nanotube transistors the ideal choice: a novel tunneling device design. IEEE Trans. Electron Devices 52, 2568–2576 (2005)

Lin, Y.M., Appenzeller, J., Knoch, J., Avouris, Ph: High performance carbon nanotube field-effect transistor with tunable polarities. IEEE Trans. Nanotechnol. 4(5), 481–489 (2005)

Upadhyay, P., Kar, R., Mandal, D., Ghoshal, S.P., Yalla, N.: A design of highly stable and low-power SRAM cell. In: Advances in Computer Communication and Computational Sciences, pp. 281-289. Springer, Singapore (2019)

Raad, B.R., Sharma, D., Kondekar, P., Nigam, K., Yadav, D.S.: Drain work function engineered doping-less charge plasma TFET for ambipolar suppression and RF performance improvement: a proposal, design, and investigation. IEEE Trans. Electron Devices 63(10), 3950–3957 (2016)

Singh, S., Kondekar, P.N.: A novel dynamically configurable electrostatically doped silicon nanowire impact ionization MOS. Superlattices Microstruct. 88(12), 695–703 (2015)

Gupta, G., Rajasekharan, B., Hueting, R.J.: Electrostatic doping in semiconductor devices. IEEE Trans. Electron Devices 64(8), 3044–3055 (2017)

Pushkarna, A., Raghavan, S., Mahmoodi, H.: Comparison of performance parameters of SRAM designs in 16 nm CMOS and CNTFET technologies. In: Proceedings of 23rd IEEE International SOC Conference, pp. 339–342 (2010)

Lin, S., Kim, Y., Lombardi, F.: A new SRAM cell design using CNTFETs. In: Proceedings of the International SoC Design Conference, pp 168–171 (2008)

Kumar, G.S., Singh, A., Raj, B.: Design and analysis of a gate-all-around CNTFET-based SRAM cell. J. Comput. Electron. 17(1), 138–145 (2018)

Kitagata, D., Sugahara, S.: Design and energy-efficient architectures for nonvolatile static random access memory using magnetic tunnel junctions. Jpn. J. Appl. Phys. 58(SB), SBBB1–SBBB12 (2019)

Stanford University Nanoelectronics Group. Stanford University CNFET model. http://nano.stanford.edu/model.php?id=23. 11 Oct 2018

Bala, S., Khosla, M.: Electrostatically doped tunnel CNTFET model for low-power VLSI circuit design. J. Comput. Electron. 17(4), 1528–1535 (2018)

Singh, J., Ramakrishnan, K., Mookerjea, S., Datta, S., Vijaykrishnan, N., Pradhan, D.: A novel Si-tunnel FET based SRAM design for ultra low-power 0.3 V VDD applications. In: Proceedings of the 2010 Asia and South Pacific Design Automation Conference, pp. 181–186. IEEE Press (2010)

Raj, B., Saxena, A.K., Dasgupta, S.: Nanoscale FinFET based SRAM cell design: analysis of performance metric, process variation, underlapped FinFET, and temperature effect. IEEE Circuits Syst. Mag. 11(3), 38–50 (2011)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Bala, S., Khosla, M. Design and performance analysis of low-power SRAM based on electrostatically doped tunnel CNTFETs. J Comput Electron 18, 856–863 (2019). https://doi.org/10.1007/s10825-019-01345-z

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-019-01345-z