Abstract

We propose a reliable high-yield nine-carbon-nanotube field-effect transistor (9-CNTFET) static random-access memory (SRAM) cell using shared bit line and half-select-free techniques. The proposed SRAM cell operates near the threshold voltage of 325 mV. The proposed cell was also tested and verified under process variation, exhibiting stable write and read operations. Due to the reduced leakage current of the proposed cell, the power consumption is significantly decreased by 4.98-fold compared with the conventional six-transistor (6T) cell. Although the use of a CNT array increases the probability of functionality of the CNTFET, it occupies 1 % more area. Due to its high \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) ratio, shortest node, shared bit line, and high-efficiency read and write ports, the read and write access time of the proposed nine-transistor (9T) SRAM cell is improved by 43 and 98 %, respectively, compared with the conventional 6T device. When using the low-feature-size CNTFET device in a new 9T SRAM cell, the area overhead is reduced to 32.9 % compared with previously published 9T SRAM cells. The proposed cell operates with minimum supply voltage near the threshold voltage region, reducing the read and write power consumption per bit by 1.2- and 1.8-fold, respectively, compared with existing 9T SRAM cells.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

As aggressive scaling of complementary metal–oxide–semiconductor (CMOS) technology approaches atomic level, the reliability of its operation becomes more challenging and requires replacement of conventional devices using new innovations such as FinFETs and CNTFETs [1,2,3]. The FinFET offers the significant advantage of excellent control over the threshold voltage, which reduces power dissipation [4]. However, reduction of the gate channel length of FinFETs is constrained by the gate insulator thickness [5]. In addition, scaling of the supply voltage requires a reduction in the threshold voltage to obtain stable performance. Meanwhile, CNTFET devices offer outstanding performance under ultralow-voltage operation near the threshold voltage region [6].

Variations in process, voltage, and temperature (PVT) are serious issues in memory circuits, greatly affecting their performance [7, 8]. The advantage of CNTFET-based memory cells is their lower sensitive to temperature variation compared with conventional Si-based MOSFET memory cells [9]. The impact of such variations on CNTFET-based SRAM cells can be controlled using shared bit line (BL) and half-select-free techniques. The parameters of different SRAM cells have been evaluated under the effects of process variations for device operation at ultralow voltage near the threshold voltage region [10].

The threshold voltage \(V_\mathrm{t}\) of a CNTFET varies inversely proportionally with the CNT diameter and can thus be controlled by diameter or chirality selection [10]. In this work, the same chirality vector is used for both p and n-type CNTFETs to design a CNTFET-based transistor, offering simplicity and a similar effect on the threshold voltage of both types of transistor.

Design of such memory cells for operation at ultralow voltage near the threshold voltage region is more challenging [11,12,13,14,15]. However, Si-MOSFET models are available for FinFETs with channel length below 32 nm, showing degraded performance due to various leakage currents, while low ON-current results in data instability [16]. CNTFET devices can be scaled down to below channel length of 10 mm, offering significantly improved power consumption and substantial performance enhancements [10]. A conventional 6T SRAM cell can be implemented using CNTFET-based transistors, offering reduced leakage current, improved read and write stability for data retention, and enhanced high-speed data transfer compared with the Si-MOSFET SRAM model. Furthermore, such 6T SRAM cells can operate at ultralow supply voltage, while aggressively scaled devices are needed to design memory cells using this new approach. This leads to the requirement for 9T SRAM cells that offer high yield and more reliable operation as well as improved read and write stability. Researchers have proposed various read and write ports to improve the parameters of such SRAM cells, including improved write and read delay, reduced leakage current, and enhanced write and read stability [17,18,19]. However, the use of an extra transistor increases the area overhead, which can compensate for the improvements in leakage current, read and write delay, data stability, and power consumption. We present herein a new approach to improve the performance of SRAM cells using shared bit line and half-select-free techniques under process, voltage, and temperature (PVT) variations.

The rest of this manuscript is organized as follows: A model of the CNTFET device is presented in Sect. 2. Comparisons between the conventional 6T, previous 9T, and proposed 9T SRAM cell are presented in Sect. 3. The performance and results for the conventional 6T, previous 9T, and proposed 9T SRAM cell are analyzed in Sect. 4, while final conclusions are presented in Sect. 5.

2 Model of CNTFET device

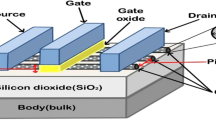

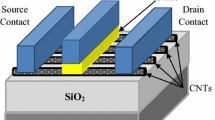

The CNTFET device can be implemented using single-walled carbon nanotubes (SWCNTs) or multiwalled carbon nanotubes (MWCNTs), placed between the drain and source, as shown in Fig. 1a, b. Many researchers have investigated whether the CNTFET is a suitable and feasible alternative to conventional CMOS devices, because of its similar characteristics and simple manufacturing process. Figure 1a and b shows a model of the CNTFET device; a complete set of parameters for the 16-nm device is described in [20]. Figure 1a shows a top view of the ideal CNTFET model, while a cross-sectional view is presented in Fig. 1b. The notations \(D_{\mathrm{cnt}} \) and \(S_{\mathrm{cnt}}\) in Fig. 1b represent the CNT diameter and the array of the pitch, respectively.

2.1 Dual chirality selection

The nature of a CNT, i.e., conducting or semiconducting, can be defined using a chirality vector. The chirality selection can be represented using an integer pair \(\left( {x,y} \right) \). If \(x-y=3i\), where i is an integer, or \(x=y\), the CNT behaves as a conductor, while otherwise it is a semiconductor. The CNT diameter can also be obtained from the indexes x and y. Herein, a triplet index \(\left( {16,19,0} \right) \) is used to describe the CNTFET structure, with \(\left( {16,0} \right) \) and \(\left( {19,0} \right) \) for the p-CNTFET and n-CNTFET, respectively. Researchers have designed and simulated CNTFET devices with various combinations of chirality vector, e.g., \(\left( {10,19,0} \right) \), \(\left( {13,19,0} \right) \), \(\left( {16,19,0} \right) \), and \(\left( {22,19,0} \right) \), for suitable adjustment of the threshold voltage [10, 21]. The V–I characteristic of the CNTFET device with different channel lengths is shown in Fig. 2.

2.2 Multithreshold technology

Variation of the CNT diameter has a significant impact on the performance parameters of the transistor, e.g., the \(I_{\mathrm{ON}} \) current and threshold voltage [22]. Although process variation results show that large diameter results in significantly improved delay, this occupies greater width [23]. The channel gate width can be determined in terms of the CNT diameter as [24]

where \(D_{\mathrm{cnt}}\) is the CNT diameter, S is the pitch of the uniform array, n is the number of tubes used in the CNTFET, and \(W_\mathrm{ol} \) is the overlap width of the gate. The conductivity of the CNTFET can be adjusted by changing the number of tubes used. In the proposed architecture, the pitch of the array and the CNT diameter were taken to be 5.3 and 0.84 nm, respectively. For a structure with symmetrical read and asymmetrical write port, the number of CNTs in the array is supposed to be optimized at 4 and (3 and 6) in p and n-type CNTFETs respectively, to achieve high yield.

The CNT diameter can be correlated with the threshold voltage as [25]

where e is the electronic charge, \(D_{\mathrm{cnt}} \) represents the CNT diameter, \(a=0.243\) nm is the interatomic distance between carbons, and \(V_\pi \) is the \(\pi \)-bond energy between carbons. In Eq. (1), the threshold voltage is approximately half the energy bandgap. Also, the threshold voltage of a CNTFET transistor varies inversely proportionally with the CNT diameter. The advantage of multithreshold techniques is that CNTFET devices can operate with different threshold voltages. To design power-efficient SRAM cells with dual threshold voltages, low voltage threshold (LVT) and high voltage threshold (HVT) can be used to perform read and write operations, respectively. From Eq. (1), the energy band can be obtained as 0.49–0.64 eV for CNT diameter of 1.4 nm [26].

2.3 Reliability and yield

For SRAM cells operating at ultralow voltage near the threshold voltage region, reliability is a major challenge due to process variations in such nanoscale technology [26,27,28]. Writing data to a memory cell with ultralow supply voltage is the major constraint on conventional 6T SRAM cells. Therefore, conventional cells much be replaced by novel devices such as CNTFETs. SRAM cells based on CNTFETs offer enhanced performance and enhanced read and write stability compared with conventional 6T SRAM cells [10]. The performance and yield of CNTFET-based SRAM cells are affected by shorts or opens between the drain and source of a CNT. The probability of functionality, i.e., high yield, of SRAM cells can be increased by using an array of CNTs [29]. However, use of parallel CNTFETs with correlated CNTs increases the ON-current, while use of series CNTFETs increases the probability of semiconducting CNTs. The probability of functionality of a transistor can be defined as [30]

where \(P_{\mathrm{semi}}\) is the probability of a semiconducting CNT, n is the number of CNTs per CNTFET, and j is the number of series elements. From Eq. (3), note that the probability of functionality can be improved by increasing the number of tubes in the CNTFET device. The yield of the SRAM cell as a quality metric can be obtained as

where the yield of the cell can be evaluated as \(\mathrm{Array}\_\mathrm{yield}\), data stability is defined as \(\mathrm{Read}\_SNM\), WVM is the write voltage margin to write new data, \(\mathrm{Cell}\_P_l \) is the leakage current, \(\mathrm{Cell}\_\mathrm{Delay}_{\mathrm{max}}\) is the maximum delay to read and write data, and \(\mathrm{Cell}\_\mathrm{Area}\) is the area of the SRAM cell. From Eq. (4), the yield can be evaluated, and should exceed 95 % to achieve highly reliable SRAM cells [44].

3 The 6T and proposed 9T SRAM cell

The CNTFET-based conventional 6T SRAM cell can be implemented with reduced leakage current, high performance, and improved stability for data retention in a node compared with the Si-MOSFET model. However, an aggressively scaled 6T SRAM cell cannot operate at ultralow supply voltage without use of write and read assist circuits.

3.1 Conventional 6T SRAM cell and limitations

The CNTFET-based 6T SRAM cell can be implemented with significantly improved power dissipation as well as enhanced read and write reliability. A conflict appears between read and write when they are applied simultaneously [31], and hence can be removed by using write and read assist circuits when implementing the SRAM memory cell. A physically connected word line (WL) performs the pseudo read operation needed to isolate data [32]. Instead of using these read and write assist circuits, column read and write assist can also be used to remove this read and write conflict, as demonstrated in Fig. 3.

The different conflict combinations can be considered to minimize the supply voltage \(V_{\mathrm{DD},~\mathrm{min}}\) using the most probable failure point (MPFP) approach [31,32,33]. The minimum supply voltage \(V_\mathrm{DD,\mathrm min}\) is determined by successful data storage in the inverter node. In the proposed design, we consider that each transistor can have a different threshold voltage. Successful data transfer can be achieved by manipulation of the threshold voltage using a Gaussian distribution. The minimum supply voltage for read, write, and retention is assumed to be 0.325 V. In the proposed 9T SRAM device, the minimum supply voltage can be maintained by adjusting the threshold voltage by selection of the CNT diameter, the number of tubes, and the dual chirality, as well as modification of the circuit.

The CNTFET-based 9T SRAM cell architecture is less affected by temperature variations compared with CMOS SRAM devices, as shown by simulations performed in the temperature range from \(-10\) to \(90\,^{\circ }\mathrm{C}\) [9]. For the proposed design, simulations performed at different temperatures revealed write failure below \(-10\,^{\circ }\mathrm{C}\), data flipping at \(90\,^{\circ }\mathrm{C}\), insufficient BL swing at \(-10\,^{\circ }\mathrm{C}\), and retention of data failure at \(90\,^{\circ }\mathrm{C}\).

The read and write assist techniques applied in the SRAM are word line A low select (WLA) and world line B high select (WLB), respectively, supported by a suppressed bit line (BL_2), negative VSS (NVSS), a negative bit line (BL_1), and transient control collapse (TVC) to remove the conflict between read and write [34,35,36]. In the cited work, for all conditions, the minimum load capacitance was assumed, to minimize delay. However, these techniques are not suitable for the 6T SRAM due to its unreliable operation at supply voltages near the threshold voltage region. Hence, the new approach was explored to reduce the power consumption with the minimum physical layout area. Considering all these challenges, a a new 9T SRAM structure was proposed.

3.2 Drawbacks of previously published 9T SRAM cell

Previously published 9T SRAM cell [2]

The CNTFET-based 9T SRAM cell proposed for more reliable read and write is shown in Fig. 4 [2]. The cross-coupled inverter is similar to in a conventional 6T SRAM cell. The transistor x3 and p-CNTFET x6 are used for write bit line access. The transistors x7 and x9 are used as a read port to isolate data from the write line. Therefore, data reading is improved compared with the conventional 6T SRAM cell. Use of a p-CNTFET transistor with an identical n-CNTFET results in current due to both electrons and holes. The layout is also optimized for high integration. The previous 9T SRAM cell design offered significantly improved leakage current, power dissipation, and write voltage margin. The number of tubes was selected as one or two, for simplicity of circuit arrangement.

In the previous 9T SRAM design, one or two CNTs were used for the practical implementation, resulting in very low yield (assumed to be 0.0045 %), which is less suitable for practical low-power applications. The half-select also results in problems, in addition to the pseudo read operation. The data conflict between read and write is also a serious issue with the previous 9T SRAM cell design. Consideration of all of these factors led to the introduction of a new, robust 9T SRAM cell using an increased number of tubes, shared bit line, and a half-select-free circuit, offering high yield. The circuit of the existing 9T SRAM cell is redrawn in Fig. 4.

3.3 Design and operation of proposed 9T SRAM cell

Various researchers have proposed 9T SRAM cells using different read and write assist combinations for reliable operation and reduced power consumption. An alternative approach to implement a CNTFET-based 9T SRAM with read and write assist ports is proposed herein, as illustrated in Fig. 5. One transistor can be removed between two adjacent cells by using a shared BL to implement the 9T SRAM cell. This shared BL technique also removes the problem of half-select, which eliminates the pseudo read operation. In the proposed 9T SRAM cell design, single-ended read, three transistors \(\left( {X7,~X8,~X9} \right) \), and a pair of transistors (\(X1-X9~\mathrm{and}~X5-X8\)) are used to form the read and write port, respectively, thereby removing the read and write conflict and also rectifying the half-select problem. The data stored in the node can be obtained by performing the read operation with the BL precharged to \(V_{\mathrm{DD}} \) then activating the bus lines using signals RWL and RRWLA and deactivating WL and RRWLB. Using the WL signal, the read operation can be isolated from data writing in the proposed cell. The write conflict is removed in the proposed cell by using separate bus lines to select the read path instead of using the WL interleaving approach [37]. First, the BL voltage is kept at \(V_{\mathrm{DD}}\) to perform the read operation; while storing the data 1 at node Q, the BL voltage decreases during the write operation, while for data 0 at node Q, transistor X2 in the read path goes off. When writing data, RWL and WL are enabled to turn on the write assist circuit, while the read assist circuit (RRWLs) goes off.

The read operation can be performed with the shared BL by disabling WL and enabling RWL and RRWLA/B, using column addressing. To write the data 0/1, RWL and WL are enabled and RRWLA/B is stored at the node pair BL1 and BL_1, assuming that the WL completely isolates the storage node pairs, which efficiently removes the half-select problem. The signal WL ensures the write half-select, completely removing the half-select problem for a sufficient difference between row and column select voltages of 25 mV, with minimum retention voltage of 325 mV. The proposed architecture completely eliminates the leakage path, hence the dynamic power consumption is drastically reduced compared with the previously published 9T SRAM cell. Furthermore, the dynamic power consumption is reduced when using the precharge scheme with the selection line [38].

The physical layout of the proposed CNTFET-based 9T SRAM cell design is presented in Fig. 6. Four extra transistors \(\left( {X6,X7,X8,~and~X9} \right) \) are used to implement the proposed cell, which therefore occupies 18 % greater area compared with the conventional 6T SRAM cell. Due to the shared bit line technique used in the proposed CNTFET-based 9T SRAM, it occupies 4.8 % less area compared with the 9T Si-MOSFET SRAM cell at the same technology node. The use of an increased number of tubes enhances the probability of functionality and results in acceptable yield, albeit increasing the area by 1 % as shown in Fig. 7.

4 Performance and results analysis of 9T SRAM cell

The proposed CNTFET-based 9T SRAM cell has been optimized for an applied voltage near the threshold voltage of 325 mV. Simulations were performed in HSPICE using CNTFET compact model codes for 16-nm technology, to evaluate the different parameters [6].

4.1 Read and write ability test

The voltage transfer characteristic can be changed by properly adjusting the size ratio of the transistors. CNTs of constant size were applied to implement the proposed cell with enhanced read and write ability [39,40,41]. The proposed 9T SRAM exhibits improved read and write ability near the threshold voltage at 325 mV compared with the 6T SRAM cell. The write ability of the different SRAM cells was defined as the write noise margin and evaluated here to analyze the performance of the different SRAM cell designs. Wider read and write SNM indicates greater stability when reading and writing data. The dedicated read and write assist circuit provides increased ability to read and write data. The dual diameter selection in the CNTFETs results in the enhanced performance metrics, i.e., significantly reduced delay, mitigation of leakage current, and increased read and write ability. The dual diameter selection also has a positive impact on the \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) current ratio [42].

4.2 Minimum supply voltage \(V_{\mathrm{DD}}\)

Aggressive supply voltage scaling degrades the performance of the 6T SRAM cell in the absence of parametric variation in the device. Furthermore, the performance can be improved by read and write assist circuits and dedicated read and write lines with row and column select. The supply voltage was scaled in the range from 0.2 to 1 V to determine the best operating voltage for the operating frequency range of 1.2 MHz to 1.8 GHz. The proposed 9T SRAM cell operating near the threshold voltage region of 325 mV at frequency of 1.25 GHz exhibited the best performance.

4.3 Leakage current analysis

Table 1 presents the leakage current evaluated for the conventional 6T, previously published 9T, and proposed 9T SRAM cell designs. The average leakage current to retain the data 1/0 was evaluated, due to the asymmetric structure of the 9T SRAM cell. Using the dedicated read and write assist circuit, the proposed 9T SRAM cell exhibited the minimum leakage current when compared with the conventional 6T and previously published 9T SRAM cells, by 49.8- and 9.7-fold, respectively [18].

The average leakage current per bit for the proposed 9T SRAM cell was evaluated as 1.83 pA consuming power of 0.549 pW for supply voltage of 0.3 V, or 2.4 pA consuming power of 0.168 pW for supply voltage of 0.7 V. The minimum leakage current achieved for supply voltage of 325 mV was 2.0 pA consuming power of 0.75 pW. The proposed 9T SRAM cell consumes the minimum leakage power when compared with the previous 9T SRAM cell at the same technology node. As shown in Fig. 8, the proposed 9T SRAM cell offers the minimum leakage power consumption and dissipation.

4.4 \(I_{\mathrm{ON}} /I_{\mathrm{OFF}} \) distribution

Placement of a CNT between the drain and source with local oxidation enhances the \(I_{\mathrm{ON}} \) current, resulting in reduced leakage current and improved data stability. Use of high voltage threshold (HVT) technology and a similar number of CNTs enhances channel formation, thereby increasing the \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) ratio. The modification in the dedicated read and write assist circuit of the proposed 9T SRAM also improves the \(I_{\mathrm{ON}} /I_{\mathrm{OFF}}\) ratio. Also, the use of dual diameter selection offers excellent control over the threshold voltage, increasing \(I_{\mathrm{ON}}\) for low supply voltage. The wider SNM provides stable data operation, improved by 99.58 % in the proposed 9T SRAM cell as compared with the 6T device shown in Fig. 9. Due to the use of the modified CNTFET device, the proposed 9T SRAM cell has very high \(I_{\mathrm{ON}}/I_{\mathrm{OFF}}\) current ratio of \(2\times 10^{4}\), providing 1.83-fold higher switching speed compared with the previously published 9T SRAM cell. The delay for the proposed 9T SRAM cell to move the data 0 onto Q and 1 onto Q_n is improved by 13.58 and 8.5-fold as compared with the 6T device and previously proposed 9T SRAM cell [26].

4.5 Power consumption

The average read and write power consumption were evaluated for the proposed 9T SRAM cell, the previously published 9T SRAM cell, and the conventional 6T SRAM cell. Compared with the conventional 6T SRAM cell, the proposed 9T SRAM cell showed 12.4-fold less read power consumption at operating frequency of 1.25 GHz. The dedicated read and write line isolate the data and completely cut off the leakage current path, hence reducing the dynamic power dissipation. Therefore, the proposed 9T SRAM has power consumption of 12.1 nW at 325 mV, while the previously published 9T SRAM cell and conventional 6T SRAM cell consume 65.7 and 272.8 nW, respectively. The write power consumption of the proposed 9T SRAM cell was found to be 11 nW, which is 1.63-fold lower than that of the previously proposed 9T SRAM cell. At the minimum operating voltage of 0.325 V, the proposed 9T SRAM cell consumes a worst-case average read and write power of 0.0138 nW per bit. However, the high voltage threshold reduces the delay when performing a write operation on a node, increasing the power consumption. To minimize the power consumption, low voltage threshold (LVT) is applied for read operations.

4.6 Stability test

The read and write stability of the 9T SRAM cell was evaluated by analysis of the read and write voltage margin. The use of the dedicated read and write line resulted in a wider SNM compared with the conventional 6T or previously published 9T SRAM cell, as presented in Fig. 9. Proper adjustment of the transistor ratio also resulted in a significantly improved noise margin. The transistor size ratio was taken as 1.4 for X5/X6 and 1.8 for X1/X9 to obtain better SNM. A wider SNM provides higher data stability. The proposed 9T SRAM cell achieved read SNM of 345 mV and write voltage margin of 576 mV, as shown in Table 2.

4.7 Read and write delay analysis

The read and write delay were evaluated for the different SRAM cells and are presented in Fig. 8. The write speed was improved by 1.89-fold compared with the conventional 6T SRAM cell. Due to the dedicated read line, the read delay was improved by 46.5 and 32 ps, respectively. When using the write port in the proposed cell to write the data 1 or 0, the delay was evaluated as 32 and 4.3 ps, respectively. The read and write delays for the different SRAM cells are compared in Fig. 10 and presented in Table 3.

4.8 Layout area

Despite offering significant advantages in terms of data stability, high-speed read and write, and improved overall design metrics, the proposed 9T SRAM cell increases the physical layout area for 16-nm technology. Although the use of a CNT array increases the width by 1 %, it also improves the probability of functionality by 1423-fold and enables high yield under process variations. The physical layout area is \(0.187\,\upmu \hbox {m}\times 0.372\,\upmu \hbox {m}\) (0.069 \(\upmu \hbox {m}^{2}\)), which is 3.1-fold less compared with the Si-MOSFET based 9T SRAM cell. The conventional 6T SRAM cell occupies an area of \(0.856\,\upmu \hbox {m}^{2}\) when using 65-nm CMOS technology. Optimization of the design for a \(32\times 32\) bit array of the proposed 9T SRAM cells results in a physical layout area of \(71.23\,\upmu \hbox {m}^{2}\). Due to transistor sharing between the proposed SRAM cells, this is 3 % less compared with the previous 9T SRAM cell.

5 Conclusions

The challenge of implementing conventional 6T SRAM cells using aggressively scaled devices can be overcome by using a novel CNTFET design [43]. An array of CNTs is used to increase the probability of functionality and the yield of 9T SRAM cells [44]. The reliability of the proposed cell is enhanced by removing all possible open and short nodes from the CNTFET. Variation of the CNT diameter is applied to achieve multithreshold voltage and adjust the supply voltage to near the threshold voltage region. The proposed SRAM cell design offers significantly improved read and write delay due to the dedicated read and write port, respectively. The proposed SRAM cell was also tested and verified under process, voltage, and temperature (PVT) variations to confirm its robust and stable read and write operations. Shared bit line and half-select-free techniques were applied to reduce the number of transistors and remove the read and write conflict, respectively. The proposed cell occupies a very small area, 3.2-fold less than for conventional technology, due to the shared bit line and use of ultralow-feature-size CNTFET devices.

References

Wang, A., Calhoun, B., Chandrakasan, A.P.: Sub-Threshold Design for Ultra Low-Power Systems. Secaucus. In: Series on integrated circuits and systems, Springer, New York (2006)

Sun, Y., Jiao, H., Kursun, V.: A novel robust and low-leakage SRAM cell with nine carbon nanotube transistors. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 23(9), 1729–1739 (2015)

Delgado-Frias, J.G., Zhang, Z., Turi, M.A.: Low power SRAM cell design for FinFET and CNTFET technologies, In: Proc. Int. Conf. Green Comput., pp. 547–553 (2010)

Cakici, T., Kim, K., Roy, K.: FinFET based SRAM design for low standby power applications, In: Proceedings 8th International Symposium Quality Electronic Design 26–28, pp. 127–132 (2007)

Tawfik, S.A., Liu, Z., Kursun, V.: Independent-gate and tied-gate FinFET SRAM circuits: design guidelines for reduced area and enhanced stability. In: Proceedings International Conference Microelectronic (ICM), pp. 171–174 (2007)

Liu, Z., Kursun, V.: Characterization of a novel nine-transistor SRAM cell. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 16(4), 488–492 (2008)

Goel, A., Sharma, R.K., Gupta, A.: Process variations aware area efficient negative bit-line voltage scheme for improving write ability of SRAM in nanometer technologies. IET Circuits Devices Syst 6(1), 45–51 (2012)

Paul, B.C., Fujita, S., Okajima, M., Lee, T.H., Wong, P.H.-S., Nishi, Y.: Impact of a process variation on nanowire and nanotube device performance. IEEE Trans. Electron Devices 54(9), 2369–2376 (2007)

Pop, E.: The role of electrical and thermal contact resistance for joule breakdown of single-wall carbon nanotubes. Nanotechnology 19(295202), 1–5 (2008)

Lin, S., Kim, Y.-B., Lombardi, F.: Design of a CNTFET-based SRAM cell by dual-chirality selection. IEEE Trans. Nanotechnol. 9(1), 30–37 (2010)

Tu, M., et al.: A single-ended disturb-free 9T subthreshold SRAM with cross-point data-aware write word-line structure, negative bit-line, adaptive read operation timing tracing. IEEE J. Solid-State Circuits 47(6), 1469–1482 (2012)

Teman, A., et al.: A 250 mV 8 kb 40 nm ultra-low power 9T supply feedback SRAM (SF-SRAM). IEEE J. Solid-State Circuits 46(11), 2713–2726 (2011)

Kim, T., et al.: A voltage scalable 0.26 V, 64 kb 8T SRAM with lowering techniques and deep sleep mode. IEEE J. Solid-State Circuits 44(6), 1785–1795 (2009)

Wang, A., Calhoun, B.H., Chandrakasan, A.P.: Sub-Threshold Design for Ultra Low-Power Systems. Springer, New York (2005)

Pasandi, G., Fakhraie, S.M.: A new sub-300 mV 8T SRAM cell design in 90 nm CMOS, In: Proceedings 17th CSI International Symposium Computer Architecture Digital System (CADS), pp. 39–44 (2013)

Kim, Y.B., Kim, Y-B., Lombardi, F.: New SRAM cell design for low power and high reliability using 32 nm independent gate FinFET technology. In: Proceedings IEEE Internatinal Workshop Design Test Nano Devices, Circuits System, pp. 25–28 (2008)

Noguchi, H., Okumura, S., Iguchi, Y., Fujiwara, H., et al.: Which is the best dual-port SRAM in 45 nm process technology 8T, 10T single end, and 10T differential. In: IEEE International Conference on Integrated Circuit Design and Technology and Tutorial, pp. 55–58 (2008)

Chang, I.J., Kim, J.-J., Park, S.P., Roy, K.: A 32 kB 10T subthreshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS. IEEE J. Solid-State Circuits 44(2), 650–658 (2009)

Chang, L., et al.: An 8T-SRAM for variability tolerance and low-voltage operation in high-performance caches. IEEE J. Solid-State Circuits 43(4), 956–963 (2008)

Sun, Y., Kursun, V.: N-type carbon-nanotube MOSFET device profile optimization for very large scale integration. Trans. Elect. Electron. Mater. 12(2), 43–50 (2011)

Kim, Y.B., Kim, Y-B., Lombardi, F., Lee, Y.J.: A low power 8T SRAM cell design technique for CNTFET. In: Proceedings IEEE Internatinal SoC Design Conference, Pusan, Korea, 24–25, pp. 176–179 (2008)

Ohno, Y., Kishimoto, S., Mizutani, T., Okazaki, T., Shinohara, H.: Chirality assignment of individual single-walled carbon nanotubes in carbon nanotube field-effect transistors by micro-photocurrent spectroscopy. Appl Phys Lett 84(8), 1368–1370 (2004)

Li, Y., Kim, W., Zhang, Y., Rolandi, M., Wang, D.: Growth of single walled carbon nanotubes from discrete catalytic nanoparticles of various sizes. J Phys Chem 105, 11424–11431 (2001)

Stanford University CNFETModelWeb site. (2014). [Online]. Available: http://nano.stanford.edu/model.php?id=23. Accessed 14 Dec 2017

Wong, P.H-S.: Field effect transistors-from silicon MOSFETs to carbon nanotube FETs, In: Proceedings 23rd International Conference Microelectronics 12– 15, pp. 103–107 (2002)

Hills, G., Zhang, J., Shulaker, M.M., Wei, H., Lee, C., Balasingam, A., Wong, H.-S.P., Mitra, S.: Rapid co-optimization of processing and circuit design to overcome carbon nanotube variations. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst 34(7), 1082–1095 (2015)

Wei, H., Patil, N., Zhang, J., Lin, A., Chen, H., Wong, H.-S. P., Mitra, S.: Efficient metallic carbon nanotube removal readily scalable to wafer-level VLSI CNFET circuits. In: Proceedings of the IEEE Symposium on VLSI Technology (VLSIT), pp. 237–238, (2010)

Shulaker, M.M., Hills, G., Wu, T.F., Bao, Z., Wong, H.S.P., Mitra, S.: Efficient metallic carbon nanotube removal for highly-scaled technologies. In: Proceedings of the IEEE International Electron Devices Meeting (IEDM), pp. 32.4.1–32.4.4, (2015)

Miranda, M., Zuber, P., Dobrovolny, P., Roussel, P.: Variability aware modeling for yield enhancement of SRAM and logic. In: Proceedings of the IEEE/ACM Conference on Design, Automation and Test in Europe, pp. 1–6 (2011)

Zhang, Zhe, Delgado-Frias, Jos’e G.: Carbon Nanotube SRAM design with metallic CNT or removed metallic CNT tolerant approaches. IEEE Trans. Nanotechnol. 11(4), 788–798 (2012)

Choi, W., Park, J.: A charge-recycling assist technique for reliable and low power SRAM design. IEEE Trans. Circuits Syst. I Reg. Papers 63(8), 1164–1175 (2016)

Khalil, D., Khellah, M., Kim, N.S., Ismail, Y., Karnik, T., De, V.K.: Accurate estimation of SRAM dynamic stability. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 16(12), 1639–1647 (2008)

Kida, T., Tsukamoto, Y., Renesas, Y.K.: Optimization of importance sampling Monte Carlo using consecutive mean-shift method and its application to SRAM dynamic stability analysis, In: Proceedings 13th International Symposium Quality Electronic Design (ISQED), (2012), pp. 572–579

Lien, N.-C., et al.: A 40 nm 512 kb cross-point 8 T pipeline SRAM with binary word-line boosting control, ripple bit-line and adaptive data- aware write-assist. IEEE Trans. Circuits Syst. I, Reg. Papers 61(12), 3416–3425 (2014)

Joshi, R.V., Kanj, R., Ramadurai, V.: A novel column-decoupled 8T cell for low-power differential and domino-based SRAM design. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 19(5), 869–882 (2011)

Wang, D.-P., Lin, H.-J., Chuang, C.-T., Hwang, W.: Low-power multiport SRAM with cross-point write word-lines, shared write bitlines, and shared write row-access transistors. IEEE Trans. Circuits Syst. II Express Briefs 61(3), 188–192 (2014)

Fujiwara, H., et al.: A 20 nm 0.6 V 2.1 \(\text{W}/\text{ MHz }\) 128kb SRAM with no half select issue by interleave wordline and hierarchical bitline scheme, In: Proceedings Symposium VLSI Technology, pp. C118–C119 (2013)

Turi, M.A., Delgado-Frias, J.G.: High-performance low-power selective precharge schemes for address decoders. IEEE Trans. Circuits Syst. II Express Briefs 55(9), 917–921 (2008)

Sun, Y., Kursun, V.: Uniform carbon nanotube diameter and nanoarray pitch for VLSI of 16nm p-channel MOSFETs. In: Proceedings of the IEEE International Conference on VLSI and System-on-Chip (VLSI-SoC), pp. 226–231, (2011)

Sun, Y., Kursun, V.: Carbon nanotubes blowing new life into NP dynamic CMOS circuits. IEEE Trans Circuits Syst I 61(2), 420–428 (2014)

Wong, H.-S.P., Akinwande, D.: Carbon Nanotube and Graphene Device Physics. Cambridge University Press, Cambridge (2011)

Brady, G.J., Way, A.J., Safron, N.S., Evensen, H.T., Gopalan, P., Arnold, M.S.: Quasi-ballistic carbon nanotube array transistors with current density exceeding Si and GaAs. Sci. Adv. 2(9), e1601240 (2016)

Chen, T.-C.: Overcoming research challenges for CMOS scaling: Industry directions, In: Proceedings International Conference Solid-State and IC Technology 23–26, pp. 4–7 (2006)

Miranda, M., Zuber, P., Dobrovolny, P., Roussel, P.: Variability aware modeling for yield enhancement of SRAM and logic. In: Proceedings of the IEEE/ACM Conference on Design, Automation and Test in Europe, pp. 1–6 (2011)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Patel, P.K., Malik, M.M. & Gupta, T.K. Reliable high-yield CNTFET-based 9T SRAM operating near threshold voltage region. J Comput Electron 17, 774–783 (2018). https://doi.org/10.1007/s10825-017-1127-z

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-017-1127-z