Abstract

A continuous and accurate model based on the two-dimensional (2D) potential solution of a tunnel field-effect transistor (TFET) with undoped vertical surrounding-gate (VSG) structure is proposed. Both ambipolarity and dual modulation effects are included to obtain a more accurate analytical model, whose validity is demonstrated by comparison with two-dimensional numerical simulations using ATLAS-2D. The continuity of the proposed model enables extraction of analog/radiofrequency (RF) parameters and device figures of merit. Moreover, the effect of introducing a high-\(\kappa \) layer on the gate oxide in improving the behavior of the VSG-TFET is explored for use in high-performance analog/RF applications. The proposed continuous analytical model can be easily implemented in commercial simulators to study and investigate VSG-TFET-based nanoelectronic circuits.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

As complementary metal–oxide–semiconductor (CMOS) downscaling approaches its physical limits due to the emergence of major degradation mechanisms, new transistor structures using multiple gates, novel materials, and doping engineering have been successfully employed to extend performance [1,2,3,4]. However, to follow the technology roadmap, and the growing requirements for low operating and leakage powers, as well as reliability against short-channel effects (SCEs) and process fluctuations, use of nonconventional devices based on different physical phenomena that overcome classical limitations is highly desired, especially tunneling field-effect transistors (TFETs). The TFET is considered to be an emerging logic device, representing a potential alternative for use in future high-performance and low-power processor chips [5]. Experiments have confirmed the viability of the complementary TFET architecture [6], including fabrication of a fully functional low-power Si gate-all-around (GAA) nanowire tunnel field-effect transistor (NWTFET) inverter with suppressed ambipolarity and large noise margin. Enhanced electrostatic control of the gate-all-around structure compared with planar TFETs has also been demonstrated [7]. The ambipolar behavior of a TFET depends on the drain doping concentration. Generally, such devices are characterized by low leakage current, steep subthreshold slope, efficient transconductance, and high intrinsic gain. Experiments and studies have shown the potential of tunneling transistors for use in low-power amplifiers, logic devices, and analog/RF and sensing applications [6,7,8,9]. At circuit level, various new mixed CMOS–TFET designs with different reliability issues have been presented [8, 10]. The main difficulty with such mixed designs is how to align the operating voltage of both devices and keep it as low as possible, thus lowering power consumption. Even if TFETs have better immunity against SCEs than conventional metal–oxide–semiconductor field-effect transistors (MOSFETs), this feature is drastically degraded beyond 30 nm, where drain-induced barrier thinning (DIBT) exponentially increases [11, 12]. Moreover, the analog/RF performance and linearity are also affected by SCEs [13]. Therefore, new practical design solutions such as high-\(\kappa \) dielectric materials, drain underlap, source/drain doping, gate material engineering, heterojunctions, and III–V materials have been proposed to overcome these physical limitations [11,12,13,14]. On the other hand, compact and continuous models that can be applied in both sub- and superthreshold operating domains are useful for understanding both types of device and for circuit simulation. Tunneling phenomena in semiconductor materials are well understood and can be efficiently modeled in Zener diodes and p–i–n junction or tunneling transistors, for which several approaches have been proposed to investigate the quantum and tunnel transport mechanisms in semiconductor devices [15,16,17,18,19,20]. All these models are directly dependent on the potential profile as a basis to calculate the current, by means of energy bands for nonlocal models or electric field for local ones. In TFETs, the tunneling effect occurs at both channel junctions, viz. source/channel and drain/channel, if ambipolarity is considered. In this case, development of an accurate potential profile model is complex due to the additional processes that have to be taken into account, such as depletion, the fringing effect on source–drain extensions (SDEs), and the impact of the high lateral field near the junctions [21,22,23,24,25,26]. In addition, the assumption of a constant electric field used in local tunneling models overestimates the current and produces a nonzero current at equilibrium, although this can be resolved by introducing a Fermi occupancy factor difference between the source and drain [26]. The complex barrier shape in TFET devices indicates that a nonlocal approach based on the Wentzel–Kramers–Brillouin (WKB) approximation and Landauer formula is more appropriate [18, 27, 28]. Nevertheless, the exact barrier profile cannot be used when elaborating such analytical models, so an arbitrary shape is adopted. The assumption of the simplest triangular barrier is equivalent to the Kane approach (i.e., constant electric field) and thus results in the same overestimation [9, 27]. On the other hand, the exponential shape is more accurate, but unfortunately the resulting expression for the tunneling probability cannot be integrated analytically, requiring use of numerical integration methods [28].

Recently, several analytical models were developed to investigate TFET devices [24,25,26,27,28,29,30]. However, in these models, the simplified Kane’s generation rate is used to replace the total electric field by an average one based on the tunneling distance or tunneling window. This approach does not evaluate the generation rate over the entire tunneling barrier and thus fails to reproduce the characteristic response profile. Besides, these models produce complex expressions, making their mathematical differentiation intractable. The derivatives of such formulas are primarily used for extraction of various parameters and figures of merit (FOMs) for assessment of device performance. Furthermore, most of these elaborated models do not take into account drain modulation. In this context, new analytical and continuous models that capture the physics of tunneling transport accurately and efficiently and are suitable for implementation in commercial simulators are required to study and design TFET-based nanoelectronic circuits.

In this work, an undoped vertical surrounding-gate TFET device with high-\(\kappa \) dielectric stack is considered. A continuous semianalytical model is developed by mathematical integration over the channel length of the complete Kane generation rate expression for direct local tunneling. This integral has the merit of preserving the spatial distribution of the generation rate, yielding an accurate response. Both ambipolarity and dual modulation effects are investigated. The electric field expression is derived from an accurate solution of Poisson’s equation using Bessel–Fourier series. The analog/RF parameters and various FOMs of the device are deduced from the proposed drain-current model. Moreover, the role of such gate dielectric material engineering in improving the analog/RF performance is investigated. The analytical results are validated against numerical simulations, revealing good agreement for a wide range of design parameters [31].

The remainder of this manuscript is organized as follows: Section 2 is devoted to a description of the various steps for the derivation of the drain-current model. The main simulation results are provided in Sect. 3, where both analog/RF parameters and linearity criteria are treated. We complete this work in Sect. 4 with a summary and some guidelines for future work.

2 Current model derivation

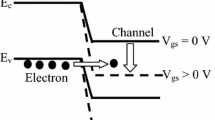

The device considered is a vertical surrounding-gate structure as presented in Fig. 1. The source/drain extensions are symmetric and heavily doped to around \(10^{20}\,\hbox {cm}^{-3}\). The introduction of this high dopant concentration is motivated by attenuation of the depletion effect [32] and attaining a high built-in potential, which in turn will lead to significant tunneling generation. With the channel length of 100 nm, short-channel effects are considerably reduced and the assumption of an intrinsic body is well justified, where only mobile charges define the electrostatic distribution [12]. However, both charge types have to be taken into account to obtain a high transfer characteristic over both positive and negative gate supply values. The dielectric gate stack is composed of silicon oxide with thickness of 2 nm and a high-\(\kappa \) dielectric material with thickness of 1 nm to reduce gate current leakage. Two-dimensional numerical simulations were performed to validate the current model based on Boltzmann statistics and drift–diffusion transport. In addition, we adopted the Kane direct tunneling model to support the tunneling generation phenomenon.

The first step in the derivation of the model is to extract the potential profile over the channel by solving the 2D Poisson’s equation, which can be expressed in cylindrical coordinates as

where \(\psi \) represents the 2D electrostatic potential, \(\varepsilon _\mathrm{Si}\) is the silicon dielectric constant, q is the electron charge, \(n_\mathrm{i}\) is the intrinsic carrier concentration, \(V_\mathrm{t}\) is the thermal voltage, and \(\rho \) is the channel mobile charge concentration.

Depending on the polarity of the gate supply, current transport by only the majority carriers in the channel are considered. Indeed, such neglect of the minority carriers has no consequence even near charge equilibrium, where the center channel potential varies linearly. The quasi-Fermi level \(V_\mathrm{q}\) included in the boundary conditions is assumed to be constant over the radius and varies from 0 at the source side to \(V_\mathrm{ds}\) at the drain side [33]. At the channel center, the quasi-Fermi levels associated with both carrier types (\(V_{\mathrm{q}n}\), \(V_{\mathrm{q}p }\)) equal, respectively, \(V_\mathrm{ds}\) and 0. To solve Poisson’s equation, it must be projected onto two components [33], i.e., a one-dimensional (1D) Poisson equation where the potential \(V_\mathrm{c}(r)\) represents the solution of Gauss’s law in a disk of finite charge density, while the potential U(z, r) in the 2D Laplace equation represents the solution of Gauss’s law in a finite cylinder of null charge density. The sum of these two terms gives the total potential distribution in the channel and is expressed with boundary conditions as

where \(V_\mathrm{fb}\) represents the flat-band voltage, \(C_\mathrm{ox}\) is the oxide capacitance, \(\varepsilon _\mathrm{ox}\) is the silicon oxide dielectric constant, and \(t_\mathrm{oxeff}\) is the effective oxide stack thickness (EOT) depending on the thicknesses of the two (oxide and high-\(\kappa \)) layers and their dielectric constants. Note that, near the channel center, the 2D potential component is neglected so that only the 1D component is involved in the charge concentration expression. Following the Chambré method [34] for solving the Poisson–Boltzmann equation and using the boundary conditions (2b), the channel center potential depending upon the gate polarity is given by

where \(\delta ={qn_\mathrm{i} }/{\varepsilon _\mathrm{Si} V_\mathrm{t} }\) and the constant \(\beta \) is obtained by substituting (4) into (2b), resulting in the formulas

Using the boundary conditions in (3b) and (3c), the solution of the 2D Laplace equation can be expressed based on Bessel–Fourier series as [35]

where \(\lambda _{n}\) is the nth root of the Robin condition \({\lambda _n }/C={J_0 (\lambda _n a)}/{J_1 (\lambda _n a)}\) and \(C={C_\mathrm{ox} }/{\varepsilon _\mathrm{Si} }\) [36]. The Bessel coefficients \(A_{n}\) and \(B_{n}\) are given by [35]

The expression for the total electric field is then deduced by differentiating the potential expression over the length and radius dimensions. However, the channel potential (4) is neglected in the transversal field component to simplify the subsequent analytical integration. The total electric field expression is divided into two components, corresponding to the source and drain sides, as indicated in (8), to calculate the tunneling current separately for each junction so that the ambipolarity behavior can be obtained.

At this stage, even if the channel potential at the center is accurately modeled, a substantial part of the electrostatic potential at the junctions may be lost due to the numerous assumptions and simplifications applied. The first assumption used to explicitly solve Poisson’s equation neglects the 2D potential part in the charge concentration term, which is valid only near the channel center [33,34,35,36,37]. Secondly, simulations show that the quasi-Fermi levels included in the boundary conditions (3c) differ from their ideal values, as shown in Fig. 2. In addition, the channel potential \(V_\mathrm{c}\) is assumed to be constant over the radius in the expressions for the integrals used to obtain the Bessel coefficients (7).

As mentioned above, the effect of depletion and fringing on the source/drain extensions impacts on the potential of the junctions. These effects depend directly on the voltage supply to both the drain and gate terminals. Note that many studies have included such depletion and fringing field effects when modeling various types of structure [21, 22, 29, 38]. Nevertheless, the remarkable lack of accuracy depicted by the outcomes of the cited works makes addition of fitting parameters inevitable to adjust the boundary potential. Although in our case the depletion effect is neglected due to the high SDE doping, numerical simulations show an important linear variation in the boundary potentials at the silicon interface, which attenuates in depth direction. As use of additional parameters seems necessary, it is preferable to avoid such effects when modeling and rather include fitting parameters and functions directly at the level of the final obtained expressions to simplify their extraction. Consequently, a correction potential \(V_\mathrm{p}\) is added to the boundary potentials (3c). Guided by the numerical fitting, we observe that this potential depends only on geometrical parameters.

Since analytical integration of the tunneling generation rate over the radius can be difficult under some situations, only the surface total electric field in (8) is considered. Moreover, the process of integrating a long or infinite series is an intractable task, justifying the simplification of expressions (8) by focusing on the first order, given by

with

with

The exponential term describes the dual modulation effect. In the gate modulation regime, one has \(V_\mathrm{c} =V_\mathrm{g}^*\), so the exponential term equals one; otherwise the channel-to-gate potential ratio determines the amount of drain modulation on tunneling generation, corrected using the coefficients \(V_\mathrm{cn}\) and \(V_\mathrm{cp}\), whose values vary around one and are dependent on geometrical parameters and the drain supply for \(V_\mathrm{cn}\).

These simplified expressions for the electric field are analogous to the exponential surface potential distribution used in pseudo-2D potential models [18, 21, 24], as well as the root of the Robin condition, whose inverse is equivalent to the characteristic length. This parameter defines the barrier bending profile, or more specifically the electric field amplitude. Near the junctions, the effect of the high lateral field cannot be neglected, which means that the classical MOSFET interface boundary condition (3b) used to extract the Robin condition roots is no longer valid. In [30], the first-order electric field expression is multiplied by a fitting coefficient to compensate for the truncation of the Fourier series to first order. Moreover, the dependence of the characteristic length on the gate bias was demonstrated and modeled in [23]. To achieve satisfactory accuracy for the potential distribution and reduce the series expression for the total electric field to first order, a dimensionally dependent fitting function is used in the Robin condition as \({C_\mathrm{p} C}/\lambda ={J_1 (\lambda a)}/{J_0 (\lambda a)}\), with \(C_\mathrm{p }\) defined by

where all the parameters can be fit numerically. The Kane tunneling generation rate used in this work is given by \(G_\mathrm{T} =A_\mathrm{k} E^{G_\mathrm{k}}\exp \left( {{-B_\mathrm{k} }/E} \right) \), where \(A_\mathrm{k}= 3.3679 \times 10^{21}\), \(B_\mathrm{k} = 2.5253 \times 10^{7}\) for silicon material, and \(G_\mathrm{k} = 2\), since only the direct tunneling process is considered. By replacing the total electric field E by expressions (9a) and (9b), the generation rate for each channel side becomes

Figure 3 shows good agreement of the modeled tunneling generation rate with the simulated responses. As expected, the rate is maximum at the junctions, where the major tunneling process occurs, but drops drastically when receding from the channel boundaries. Hence, one can obtain the total tunneling current by summing the integrals of the generation rate equations over the channel length and radius at the junction locations, as illustrated below:

with D a fitting function that evaluates the depth of the tunneling process when only the surface electric field is involved. The second term is a correction function that permits the relative error against numerical simulations to be reduced to around 0.1 % during gate modulation, where \(V_\mathrm{gm}\) is the gate voltage and \(\Delta _\mathrm{r}\) is the relative error corresponding to the minimum current.

The next figures validate the current model for different configurations and voltage supplies. As can be deduced from the model, reducing the oxide layer thickness will increase the oxide capacitance, electric field, and tunneling current in turn, as illustrated in Figs. 4a and 5b. In an analogous manner, reduction of the channel radius leads to an increase in the tunneling current.

a Multiple derivates of the current with respect to the applied gate voltage (\(T_\mathrm{Si}=14\) nm, EOT \(=\) 3 nm, and \(V_\mathrm{ds}=1\) V); the inset illustrates the simulated third derivative with more accuracy. b First derivative of the current with respect to applied drain voltage (\(T_\mathrm{Si}=12\) nm and \(V_\mathrm{gs}=1\) V)

The ambipolarity behavior is well described, as well as the dual modulation effect. The tunneling current on the drain side increases relative to the drain bias and shifts the minimum current forward with gate voltage. Furthermore, it is clearly shown that, during gate modulation, the tunneling process on the source side is totally independent of the drain bias. The dual modulation effect is also described in Fig. 5b, where for low drain bias, the tunneling on the source side is controlled by the drain modulation. The channel potential varies linearly with the drain bias until the drain boundary potential exceeds the channel potential. Then, the regime switches to gate modulation, where the constant gate bias fixes the tunneling near the source side and raises its value at the drain side.

The next step is differentiation of the expression for the current with respect to the gate and drain supplies, with the aim of extracting different analog/RF parameters. Note that only the source tunneling current is considered.

with

and

The last equation is obtained by differentiation of expression (4a) then replacing the derivative of \(\beta \) by

Following the same methodology, the derivative with respect to the drain supply is given by

where

and

Here, the fitting function \(V_\mathrm{ce}\) replaces the exponential term since the drain-bias-dependent parameter \(V_\mathrm{cn}\) is difficult to model and by doing so the derivative expression is simplified. The numerical fitting provides the formula \(V_\mathrm{ce} =4\left( {V_\mathrm{c} +c_1 } \right) ^{-1/4}+c_2 V_\mathrm{ds} +c_3 \).

a \(\text {SS}_\mathrm{min }\) (solid) and \(I_\mathrm{on}/I_\mathrm{off }\) (dashed) as functions of channel diameter for different drain biases (EOT \(=\) 3 nm and \(L=100\) nm). b \(\text {SS}_\mathrm{min}\) (solid) and \(I_\mathrm{on}\)/\(I_\mathrm{off}\) (dashed) as functions of channel length for different high-\(\kappa \) dielectric constant (\(T_\mathrm{Si}=12\) nm and \(V_\mathrm{ds}=0.5\) V)

The transition from gate to drain modulation of the tunneling barrier is reflected in the third derivative in Fig. 6a. This transition occurs smoothly over an interval of gate bias. The start point corresponds to the maximum of the third derivative, while the end point is revealed by a kink effect. On the basis of the expressions elaborated above, any degree of differentiation can be obtained with good agreement in comparison with its numerical counterpart, especially during the gate modulation, as depicted in Fig. 6. Nevertheless, the exponential term accounting for the drain modulation must be accurately modeled. One of the important parameters obtained from the expression for the derivative of the current to assess TFET performance is the subthreshold slope (SS), expressed as

with

where

Note that the derivative of the term B is limited to the gate modulation regime, where the exponential term equals one. The next figures illustrate the variation of the minimum subthreshold slope and \(I_\mathrm{on}/I_\mathrm{off}\) current ratio for different dimensions and drain supplies (\(I_\mathrm{on}\) at \(V_\mathrm{gs}=1\) V and \(I_\mathrm{off}=I_\mathrm{Tmin}\)). As mentioned above, reduction of the channel diameter or oxide thickness enhances the on-current. Unfortunately, the off-current is increased as well, by an amount that exceeds the magnitude of the on-current increase. Consequently, the \(I_\mathrm{on}/I_\mathrm{off }\) current ratio as well as \(\text {SS}_\mathrm{min}\) degrade for reduced channel diameter and oxide thickness (Fig. 7a, b). Furthermore, these degradations are accentuated with drain bias increase. Such major alterations can be attributed to the wide bandgap of silicon and the enhanced ambipolar current. In practice, many solutions are available to improve TFET performance. In this regard, the validity of the developed model for any material may be useful to explore the impact of material engineering. Nevertheless, as our model is based on a local tunneling approach, it is not suitable for heterostructure TFETs, for which a nonlocal model should be applied [18, 28].

To obtain a more reliable modeling framework, the model must be adapted to describe SCEs. Indeed, the model is derived based on the assumption that \(\sinh (\lambda L) \approx \hbox { exp}(\lambda L)/2\), which is correct only for long channel lengths. Furthermore, drain-induced barrier thinning will modify the electrostatic distribution, resulting in higher lateral electric field, indicating the need to include the effect of the length on the root of the Robin condition \(\lambda \) [11]. To avoid additional modeling complexity, the impact of length variation is added to the parameters D and \(V_\mathrm{p}\) by means of a fitting coefficient expressed as \(1+\alpha ^{{\prime }}\hbox { exp}(\beta ^{{\prime }}L)\). This solution gives good agreement of the model with numerical results, as illustrated in Fig. 7b.

As reported in literature [11, 12], the TFET exhibits good immunity against SCEs, while this feature is drastically degraded beyond 30 nm, where the subthreshold slope as well as \(I_\mathrm{on}/I_\mathrm{off }\) ratio are degraded in an exponential manner, as depicted in Fig. 7b. Note that the direct and trap-assisted tunneling from source to drain that become possible for lengths approaching 20 nm are not taken into account but may further degrade device performance [9]. However, the high-\(\kappa \) layer attenuates the SCEs, with \(\text {SS}_\mathrm{min}\) varying around 4 % for a layer with dielectric constant of 80 compared with 9 % for a device without a high-dielectric layer.

3 Results and discussion

This section is composed of two parts. The first subsection is dedicated to the presentation of the analog/RF measures, while the second part is reserved for analysis of different linearity criteria.

3.1 Analog/RF parameters

Investigation of the scaling capability, device performance, and linearity in the high-frequency regime is mandatory for circuit design purposes. The TFET paradigm has been considered as a competitive alternative to MOSFET devices for use in analog/RF applications. Device performance can be assessed by compact modeling of the analog/RF parameters jointly with FOM analysis [13, 39]. The next figures depict various analog/RF criteria for different geometrical parameters in gate modulation mode (\(V_\mathrm{gs}=V_\mathrm{ds}\)=1 V). The transconductance, defined as \(\partial I_\mathrm{ds} /\partial V_\mathrm{gs} \), is shown in Fig. 8a as a function of channel diameter for different high-\(\kappa \) values. Similarly to the case of the current, reducing the channel or the effective oxide thickness increases the transconductance. However, attenuation of the high-\(\kappa \) layer effect is observed for a value of 10 nm. Likewise, the output conductance, defined as \(\partial I_\mathrm{ds} /\partial V_\mathrm{ds} \), shows an increasing tendency with respect to the high-\(\kappa \) dielectric value (Fig. 8b). Note that, even if the transconductance of the TFET is relatively low with respect to MOSFETs, the output conductance is as much lower, leading to an acceptable intrinsic gain expressed as \(A_\mathrm{v} =G_\mathrm{m} /G_\mathrm{d} \). However, the impact of the high-\(\kappa \) layer is more pronounced on \(G_\mathrm{d}\) than \(G_\mathrm{m}\), resulting in degradation of the gain, as highlighted in Fig. 8b.

As a consequence of the transconductance enhancement, the unity-gain cutoff frequency is improved in the same way, as shown in Fig. 9a. It is expressed as \(f_\mathrm{t} \approx {G_\mathrm{m} }/{(2\pi C_\mathrm{gg} )}\), where \(C_\mathrm{gg} =C_\mathrm{gs} +C_\mathrm{gd} \) represents the total gate capacitance extracted numerically.

The transconductance generation factor, expressed by \(\mathrm{TGF}={G_\mathrm{m} }/{I_\mathrm{d} }\), is another important criterion for analog/RF applications, playing a vital role in the field of RF circuit design [40]. It can be interpreted as the efficiency of a device to convert current (or implicitly power) into transconductance and therefore gain and frequency [41]. To evaluate the effect of the gate stack and radius on the TGF, it is shown at constant transconductance in Fig. 9b. It seems that the TGF drops with reduction of the channel thickness. However, this degradation is largely compensated by the reduction of the effective oxide thickness.

3.2 Linearity analysis

As for MOSFETs, nonlinearity is an inherent TFET characteristic. In analog/RF applications such as low-noise amplifiers (LNAs) or filters, linearity in the operating range must be obtained to preserve circuit performance. Due to high second- and third-order transconductance derivatives, gain compression, distortion, and intermodulation become important, leading to signal corruption and loss of output power [42]. In a nonlinear system, the output can be expressed in a Taylor series expansion as a function of the alternating-current (AC) gate voltage as [43]

where \(I_{0}\) is the direct-current (DC) component and \(g_{\mathrm{m}i} =\frac{\partial ^{i}I_\mathrm{ds} }{\partial v_\mathrm{gs}^i }\) is the ith derivative of the drain current. Based on the previous expression, the linearity FOMs can be extracted as follows [44]:

The second and third voltage intercept points, denoted by VIP\(_{2}\) and \(\hbox {VIP}_{3}\), respectively, represent the voltage at which the second and third harmonics reach the fundamental tone and determine the amount of signal distortion [44]. Therefore, higher values of these FOMs indicate a wider linear operating range. Ideally, in a system with odd symmetry, harmonics of even order vanish, while in a real circuit, symmetry corruption yields a finite number of even-order harmonics [42]. As illustrated in Fig. 10, reducing the channel width and effective oxide thickness widens the linear operating range. For an input comprising two tones, additional nonharmonic components are generated from the frequency difference, a phenomenon called intermodulation (IM). In analogy with \(\hbox {VIP}_{3}\), the third-order intermodulation intercept point \(\hbox {IIP}_{3}\) represents the input at which the amplitude of the generated third-order IM components equals that of the fundamentals [42, 45]. In the case of a differential LNA, the extrapolated voltage input (\(\sqrt{{8g_\mathrm{m1} }/{g_\mathrm{m3} }})\) is squared and divided by twice the ideal input resistance \(R_\mathrm{s}\) of \(50\,\Omega \) to yield \(\hbox {IIP}_{3}\) in terms of power [46]. As for the previous FOMs, \(\hbox {IIP}_{3}\) (Fig. 11a) exhibits the same improvement trend.

Even if the increase of the signal amplitude worsens the distortion, the second and third harmonics can be filtered, which is not the case for the total amplitude of the fundamental, for which the increase of the negative second term yields signal compression [45, 46]. This term is generated by the third harmonic and is generally neglected for very small signals. Its effect for higher amplitudes can be extrapolated by means of the 1-dB compression point, defined as the input at which the fundamental amplitude drops by 1 dB, expressed as \(0.38\sqrt{\left| {{6g_\mathrm{m1} }/{g_\mathrm{m3} }} \right| }\) for one-tone input and \(0.22\sqrt{\left| {{6g_\mathrm{m1} }/{g_\mathrm{m3} }} \right| }\) for input of two tones with the same amplitude [42, 45]. Note that \(g_\mathrm{m3}\) becomes negative above the threshold voltage and during drain modulation. As observed in Fig. 6a, the results computed for the modeled current derivatives show an important error for high \(V_\mathrm{gs}\). Thus, a more accurate expression for the exponential term describing the drain modulation as \(\exp \left( {V_\mathrm{cn} \left( {1-\left( {\frac{V_\mathrm{c} }{V_\mathrm{g}^*}} \right) ^{{V}'_\mathrm{cn} }} \right) } \right) \) is used. Figure 11b shows the 1-dB compression point input power extracted for both one and two tones, respectively, in the case of a single-ended LNA and a differential LNA for \(50\,\Omega \) input resistance at 1.8 V DC gate bias. It is shown that, by reducing either the channel diameter or effective oxide thickness, the 1-dB compression point can be lowered, thereby reducing the dynamic operating range.

4 Conclusions

A continuous, accurate tunneling current model based on a cylindrical harmonics solution of the 2D potential was developed for a vertical surrounding-gate structure. The model describes the ambipolar tunneling and dual modulation effects remarkably well. The continuity and high transfer characteristic permit evaluation of device scaling capability, analog/RF performance, and linearity. The results show that decreasing either the channel diameter or effective oxide thickness improves the current and the majority of device FOMs. Moreover, the role of introducing a high-\(\kappa \) layer on the gate oxide in improving the behavior of the VSG-TFET is investigated for use in high-performance analog/RF applications, revealing strong effects on the power consumption and dynamic operating range. Thus, the dimensions and operating supply range should be carefully chosen depending upon the device application. Overall, the results demonstrate a comfortable upper limit of the dynamic operating range with high gain and acceptable cutoff frequency, making such TFET structures promising candidates for use in low-power analog/RF applications.

References

International Technology Roadmap for Semiconductors (ITRS). http://itrs.net (2013). Accessed 20 Dec 2013

Chen, Q., Meindl, J.D.: Nanoscale metal oxide semiconductor field effect transistors: scaling limits and opportunities. Nanotechnology 15, 8549–8555 (2004)

Bentrcia, T., Djeffal, F., Benhaya, A.: Continuous analytic I–V model for GS DG MOSFETs including hot-carrier degradation effects. J. Semicond. 33, 14001–14006 (2012)

Djeffal, F., Ferhati, H., Bentrcia, T.: Improved analog and RF performances of gate-all-around junctionless MOSFET with drain and source extensions. Superlattices Microstruct. 90, 132–140 (2016)

ITRS Summer Meeting, Palo Alto, CA, July 11–12 (2015)

Luong, G.V., et al.: Complementary strained Si GAA nanowire TFET inverter with suppressed ambipolarity. IEEE Electron Device Lett. 37, 950–953 (2016)

Schulte-Braucks, C., et al.: Experimental demonstration of improved analog device performance of nanowire-TFETs. Solid State Electron. 113, 179–183 (2015)

Datta, S., Liu, H., Narayanan, V.: Tunnel FET technology: a reliability perspective. In: Microelectronics Reliability, vol. 54, pp. 861–874 (2014)

Seabaugh, A.C., Zhang, Q.: Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98, 2095–2110 (2010)

Schmitt-Landsiedel, D., Werner, C.: "Innovative devices for integrated circuits—a design perspective,"Solid-State. Electronics 53, 411–417 (2009)

Liu, L., Mohata, D., Datta, S.: Scaling length theory of double-gate interband tunnel field-effect transistors, IEEE Trans. Electron Devices 59, 902–908 (2012)

Chien, N.D., Shih, C.H.: Short channel effects in tunnel field-effect transistors with different configurations of abrupt and graded Si/SiGe heterojunctions. Superlattices Microstruct. 100, 857–866 (2016)

Biswal, S.M., Baral, B., De, D., Sarkar, A.: Study of effect of gate-length downscaling on the analog/RF performance and linearity investigation of InAs-based nanowire Tunnel FET. Superlattices Microstruct. 91, 319–330 (2016)

Lee, J.S., et al.: Simulation study on effect of drain underlap in gate-all-around tunneling field-effect transistors. Curr. Appl. Phys. 13, 1143–1149 (2013)

Kane, E.O.: Zener tunneling in semiconductors. J. Phys. Chem. Solids 12, 181–188 (1960)

Ahmed, K., Monzure Elahi, M.M., Shofiqul Islam, Md.: A compact analytical model of band-to-band tunneling in a nanoscale p-i-n diode. In: International Conference on Informatics, Electronics & Vision (ICIEV), Dhaka, Bangladesh, 18–19 May (2012)

Bhushan, B., Nayak, K., Rao, V.R.: DC compact model for SOI tunnel field-effect transistors. IEEE Trans. Electron Devices 59, 2635–2642 (2012)

Taur, Y., Wu, J., Min, J.: An analytic model for heterojunction tunnel FETs with exponential barrier. In: IEEE Transactions on Electron Devices, vol. 62, pp. 1399–1404 (2015)

Mamidala, J.K., Vishnoi, R., Pandey, P.: Tunnel field-effect transistors (TFET): modeling and simulation. Wiley, New York (2017)

Kane, E.O.: Theory of tunneling. J. Appl. Phys. 32, 83–91 (1961)

Bardon, M.G., Neves, H.P., Puers, R., Hoof, C.V.: Pseudo-two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans. Electron Devices 57, 827–834 (2010)

Zhang, L., Lin, X., He, J., Chan, M.: An analytical charge model for double-gate tunnel FETs. IEEE Trans Electron Devices 59, 3217–3223 (2012)

Shen, C., et al.: A variational approach to the two-dimensional nonlinear poisson’s equation for the modeling of tunneling transistors. IEEE Trans. Electron Devices 29, 1252–1255 (2008)

Pan, A., Chen, S., Chui, C.O.: Electrostatic modeling and insights regarding multigate lateral tunneling transistors. IEEE Trans. Electron Devices 60, 2712–2720 (2013)

Patel, P.A.: Steep turn on/off green tunnel transistors, PhD dissertation. University of California, Berkeley (2010)

Zhang, L., Chan, M.: SPICE modeling of double-gate tunnel-FETs including channel transports. IEEE Trans. Electron Devices 61, 300–307 (2014)

Pal, A., Dutta, A.K.: Analytical drain current modeling of double-gate tunnel field-effect transistors. IEEE Trans Electron Devices 63, 3213–3221 (2016)

Min, J., Wu, J., Taur, Y.: Analysis of source doping effect in tunnel FETs with staggered bandgap. IEEE Electron Device Lett. 36, 1094–1096 (2015)

Tajik Khaveh, H.R., Mohammadi, S.: Potential and drain current modeling of gate-all-around tunnel FETs considering the junctions depletion regions and the channel mobile charge carriers. IEEE Trans. Electron Devices 63, 5021–5029 (2016)

Gholizadeh, M., Hosseini, S.E.: A 2-D analytical model for double-gate tunnel FETs. In: IEEE Transactions on Electron Devices, vol. 61, pp. 1494–1500 (2014)

ATLAS User Manual: Device Simulation Software (2012)

Wu, C., Huang, R., Huang, Q.: An analytical surface potential model accounting for the dual-modulation effects in tunnel FETs, IEEE Trans. Electron Devices 61, 2690–2696 (2014)

Abd El Hamid, H., Iñíguez, B., Guitart, J.R.: Analytical model of the threshold voltage and subthreshold swing of undoped cylindrical gate-all-around-based MOSFETs. IEEE Trans Electron Devices 54, 572–579 (2007)

Chambré, P.L.: On the solution of the Poisson–Boltzmann equation with application to the theory of thermal explosions. J. Chem. Phys. 20, 1795–1797 (1952)

Polyanin, A.D.: Handbook of Linear Partial Differential Equation for Engineers and Scientists. Chapman & Hall/CRC, London (2002)

Asmar, N.H.: Partial Differential Equations with Fourier Series and Boundary Value Problems. Pearson Prentice Hall, Upper Saddle River (2004)

Ray, B., Mahapatra, S.: Modeling and analysis of body potential of cylindrical gate-all-around nanowire transistor. IEEE Trans. Electron Devices 55, 2409–2416 (2008)

Abdi, D.B., Kumar, M.J.: 2-D threshold voltage model for the double-gate p-n-p-n TFET with localized charges. IEEE Trans. Electron Devices 63, 3663–3668 (2016)

Rechem, D., Khial, A., Azizi, C., Djeffal, F.: Impacts of high-k gate dielectrics and low temperature on the performance of nanoscale CNTFETs. J. Comput. Electron. 15, 1308–1315 (2016)

Cornetta, G., Santos, D.J., Vazquez, J.M.: Wireless Radio-Frequency Standards and System Design: Advanced Techniques, 1st edn. IGI Publishing Hershey, Hershey (2012)

Baruah, R.K., Paily, R.P.: A dual material double-layer gate stack junctionless transistor for enhanced analog performance. In: VLSI Design and Test 17th International Symposium, VDAT 2013, Jaipur, India, July 27–30 (2013)

Razavi, B.: RF Microelectronics. Prentice Hall, Englewood (1998)

Ma, W., Kaya, S.: Impact of device physics on DG and SOI MOSFET linearity. Solid State Electron. 48, 1741–1746 (2004)

Bentrcia, T., Djeffal, F., Chebaki, E., Arar, D.: Impact of the drain and source extensions on nanoscale Double-Gate Junctionless MOSFET analog and RF performances. Mater. Sci. Semicond. Process. 42, 264–267 (2016)

Rogers, J., Plett, C.: Radio Freq. Integr. Circuit Des. Artech House, Norwood (2003)

Lee, T.H.: The Design of CMOS Radio-Frequency Integrated Circuits, 2nd edn. Cambridge University Press, Cambridge (2004)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Abdelmalek, N., Djeffal, F. & Bentrcia, T. Continuous semianalytical modeling of vertical surrounding-gate tunnel FET: analog/RF performance evaluation. J Comput Electron 17, 724–735 (2018). https://doi.org/10.1007/s10825-018-1141-9

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-018-1141-9