Abstract

This paper presents a low leakage power 10T single-ended SRAM cell in the sub-threshold region that improves read, write, and hold stability. While at low voltages, the write-ability is increased by temporarily floating the data node, the read stability of the cell is maintained approximately as equal as the hold state by separating the data-storage node from the read bit line by using only a single transistor. According to Simulations using HSPICE software in 10 nm FinFET technology, the read stability of the proposed cell is approximately 4.8× higher than the conventional 6T at 200 mV. Furthermore, the proposed cell is found to have the lowest static power dissipation, as it tends to be 4% lower than the standard six-transistor cell at this voltage. This study shows that the yield of the proposed cell is higher than 6σ in all operations, and supply voltages down to 200 mV.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

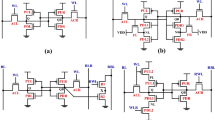

Nowadays, as the demand for ultra-low leakage power applications such as implantable devices in the human body, wireless sensor networks, and other portable devices has increased, the need for managing power consumption in digital chips has become an important issue [1]. SRAM cells are one of the most important components of digital chips, which consume a large percentage of power [2]. Therefore, reducing the leakage power of these memories can significantly lower the leakage power consumption of an entire chip. One way to reduce the power consumption in a cell involves reducing the operating voltage of the cell near and under the threshold voltage. However, as the supply voltage of the cell decreases below the threshold voltage, the effects of variations in the manufacturing process increase, followed by short-channel effects in technologies below 100 nm [3]. Therefore, maintaining the stability of SRAM cells poses a significant challenge in the sub-threshold region [4]. As a result, new technologies have been introduced to reduce the variations in the manufacturing process and diminish the short-channel effects of nanometer technologies. One of the promising candidates is the FinFET structure because of its better gate control over the channel [5]. Despite the benefits of this technology for memory cell design, conventional 6T cell (Fig. 1(a)) still not have a proper yield in the read and write operations at low supply voltages. This is because of conflicts in the read and write requirements of conventional 6T cells, leading to a trade-off in the sizing of the cells [6]. The width quantization property of FinFET aggravates this issue because of the constant height [7].

To overcome this issue, different SRAM cell structures have been proposed, such as conventional 8T SRAM cell (Fig. 1(b)). In this cell, the read operation is separated from the write operation by using two transistors. Considering this technique, the voltage division between the data node and the bitline does not occur, resulting in a read stability that is approximately equal to the hold stability. However, due to the existence of three bitlines in this cell, the cell overhead is increased. Furthermore, at low voltages, due to the positive feedback of the inverters, the cell suffers from a low write-ability [8]. To improve the write-ability, the inverters involved in the write operations are weakened to ease the operation. However, the ability to write “1” at low supply voltages remains an important challenge in single-ended structures. The rest of this paper is organized as follows. Section 2 introduces the proposed structure and explains its operation in detail. Results and discussion are given in Sect. 3. Section 4 concludes the paper.

2 Proposed 10T SRAM cell structure

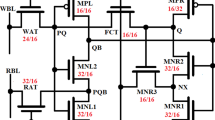

Figure 2 demonstrates the schematic of the proposed 10T SRAM cell. The cell is operational at low supply voltages down to the sub-threshold region. This cell consists of two back-to-back inverters, INVL (PDL1, PDL2, PUL1, and PUL2) and INVR (PDR1, PDR2, and PUR). We chose a tristate inverter with enable signals of WLB and WL for the INVL. On the other hand, the right inverter, INVR, has two series nMOS transistors as pull-down. A transmission gate (ACL1 and ACL2) is used for the single-ended write operation and a pass transistor (RD) as an access transistor is used for read operation. The read bitline (RBL) and the word line (RWL) are the control signals for the read operation. On the other hand, the write bitline (BL) and the write word lines (WL and WLB) are for the write operation.

2.1 Hold state

In the hold state, data is stored in the cross-coupled inverters INVL and INVR. To have the maximum hold stability, the pull-up and pull-down strengths of the inverters should be equal. Due to the greater mobility of the n-type transistor than the p-type one, we exploit two series nMOS transistors in the pull-down of INVR to balance the pull-down and pull-up strengths. Besides, the stacked pull-down transistors are effective in lowering static power dissipation. Also, for the left inverter INVL, it has been investigated that by increasing the number of PUL1 fins to two, the strength of the pull-up network becomes close to the pull-down network leading to maximum hold stability. To increase the density, other transistors in the inverters are minimum-sized as one fin. The values of the control signals are also set as listed in Table 1.

2.2 Read operation

For the read operation, RWL is grounded and the operation is performed using the RD transistor. If QB = “1”, RD turns on and discharges RBL and then a sense amplifier completes the read operation. If QB = “0”, RBL remains pre-charged. As the RD transistor gate is connected to the QB node, no voltage disturbance occurs from the read bitline on the QB node. Hence, read stability is high, approximately equal to hold stability. However, as RWL is a row-based signal, the RWL driver must have the ability to sink currents from the read access transistors of the cells with QB = “1” in a row. The RWL driver is designed for the worst-case scenario, in which all cells in a row have QB = “1” [9]. Also, the readout circuitry may face the sneaking currents from unselected RWLs for the cells in the same column with QB = “1” as shown in Fig. 3. The sneaking current emerges as RBL discharges until the current becomes equal to the discharging current and RBL voltage saturates. To solve this issue, the proposed cell benefits from a sense amplifier that can discern a small voltage difference before sneaking currents emerge [10]. To increase the read performance, the size of the RD transistor is also selected two fins.

2.3 Write operation

The write operation of the proposed cell is done via a single bitline (BL). Since in single-ended structures, the n-type access transistors are weak in transferring “1”, we exploit an extra p-type access transistor in parallel to the n-type access transistor similar to [11]. In this case, “1” is completely transmitted by the p-type access transistor to the data-storage node (Q). Further, we used the tristate inverter to facilitate the write operation, for the left inverter. During the write operation, WL and WLB control signals are “1” and “0”, respectively.

Hence, PDL1 and PUL1 transistors are cut off, switching the INVL to the high impedance mode. Therefore, data can enter the cell easily augmenting the write performance and stability. A similar technique is used for WRE8T cell [12] shown in Fig. 1(d). For WRE8T, the left inverter becomes power gated during write easing the operation. As discussed later, our technique presents less leakage power. It should be noted that by asserting the row-based WL and WLB signals, the data of an unselected cell in the same selected row may be flipped. This is because for the half-selected cells, the write access transistors are ON and the left inverters are in the high impedance mode. To conquer this issue, an efficient write-back technique can be used [13]. In this technique, the data of the half-selected cells are first read by their read bitlines. Then the read data is put on the write bitlines of the half-selected cells by three n-type transistors and an inverter to restore the original data.

3 Simulation results and comparisons

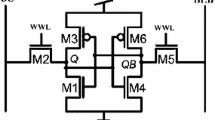

In this section, metrics of the SRAMs such as stability, speed, power, and area are evaluated, and the results are analyzed. We compare the results of the proposed cell with the 6T and 8T cells and two similar single-ended 8T (SE-DFC) and WRE8T structures. HSPICE simulations were performed using 10 nm FinFET predictive technology model [14] to measure the performance parameters. To evaluate the timing of different operations and calculate the energy-delay product (EDP), all cells are examined in a 4 kb array (64 × 64 as shown in Fig. 4) and the interconnect capacitance is assumed 0.16 fF/µm [15]. In Fig. 4, we have shown the proposed cell array. Our results are supported by rigorous Monte-Carlo simulations performed for 5000 samples to analyze process variation effects. Variations in the manufacturing process can be divided into global and local categories. Global variations for the channel length, fin width, and fin height are considered Gaussian with 3σ = 10% of their nominal values and for the gate oxide thickness with 3σ = 5% of its nominal value. Besides, local variations of the channel length and fin width are also considered Gaussian with 3σ = 5% of the nominal value [16]. It has been shown that different stability parameters follow Gaussian distribution (Fig. 5). To compare the variability of the stability parameters, the mean of the corresponding parameter is divided by the standard deviation which is called yield. The amount of obtained yield represents the minimum variation needed to cause a failure. Today, Six-Sigma (6σ) yield or more is needed for big SRAM arrays [16].

3.1 Hold stability

Hold stability is measured using the hold static noise margin (HSNM) metric, which is the length of the largest square encompassed in the butterfly curves in the hold state [17]. Figure 6 illustrates the hold butterfly curve of the proposed structure at 200 mV supply voltage. As shown in Fig. 7(a), HSNM of the proposed cell is slightly higher than all the investigated cells. Figure 7(b) shows the hold yield of the compared cells at different supply voltages. As displayed, the hold yield of this cell is lower than all other compared cells at a supply voltage of 600 mV (still higher than 20).

This may be attributed to the fact that the DIBL at high supply voltages is exacerbated by an increase in the drain-to-source voltage. Hence, the proposed cell is more sensitive to this phenomenon due to the use of two OFF access transistors (ACL1 and ACL2) with Vds = VDD when Q = “0”. However, by decreasing the supply voltage, the effect of DIBL is attenuated and the proposed cell shows good robustness against the process variability. For instance, at supply voltages below 300 mV, the proposed structure has the highest hold yield.

3.2 Read stability

Read SNM (RSNM) is the popular metric for read stability [18]. As shown in Fig. 8(a) the proposed cell, followed by the conventional 8T cell, has the highest RSNM among all the studied cells. In these cells, by decoupling the data-storage node from the read bitline, the voltage division between these two nodes will not occur. Hence the RSNM of the proposed cell and the conventional 8T cell is close to their HSNM. It should be noted that RSNM of the 8T (SE-DFC) cell has not been examined. Since for this cell, the PDL1 and PDR1 pull-down transistors are turned off during the read operation, no read butterfly curve is formed for this cell. As illustrated in Fig. 8(b), the read yields of the proposed cell and conventional 8T are higher than the other cells due to the higher nominal RSNM. According to Fig. 8(b), the yield of the proposed cell is approximately 5× higher than the WRE8T cell at 200 mV supply voltage. It should be noted that at this voltage, all the compared cells except the proposed cell and the conventional 8T cell, suffer from a read yield less than 6σ. It asserts that the other compared cells cannot have a robust read at sub-threshold voltages, except the proposed and the conventional 8T cells.

3.3 Write-ability

There are various methods to calculate the write margin. One of them is CWLM [19]. In this case, the desired data is first placed on the bitline, followed by sweeping the word line WL from the ground to the supply voltage. Meanwhile, when the Q voltage is equal to QB, the difference between the WL voltage and the supply voltage indicates the write margin. It can be seen from Fig. 9(a) that for write “1”, the write margin of the proposed cell is higher than all the cells, including the WRE8T. This is attributed to the fact that in the proposed cell we exploit two write access transistors, which one of them is p-type passing “1” strongly. To facilitate the single-ended write further, the (PDL1 and PUL1) transistors also become off during write operation floating the Q node. This allows the strong write access transistors to easily write the data into the cell. Following the proposed cell, the WRE8T cell has the highest write margin. For write “0”, the write margin of the proposed cell and WRE8T cell is approximately equal because the n-type write access transistor transmits “0” completely. Since the storage node of both mentioned cells is disconnected from supply and ground, these cells have the highest write “0” margin. Given that the write “1” margin of the proposed cell is higher than all the studied cells, the yield of the proposed cell for “write “1” is higher than all the compared cells. Also, the yield of write “0” operation is close to the WRE8T cell. It can be seen from Fig. 10 that for write “1” operation at a supply voltage below 300 mV, the yield of all investigated cells is below (6σ) except the proposed cell. Furthermore, for write “0”, the yield is less than (6σ) among all of the cells except the WRE8T cell and the proposed cell. Therefore, the proposed cell is suitable for ultra-low voltage applications.

3.4 Read and write access times

Read time is defined as the time from when read word line reaches VDD/2 to when the voltage of read bitline reaches 90% of VDD as the used sense amplifier can sense 10% of VDD in this work [10]. For the proposed cell as the read access transistor RD is upsized, the read time is the least between the other compared cells for supply voltages below 400 mV as shown in Fig. 11. It should be noted during the read operation, the RWL control signal is grounded by the driver. However, for high supply voltages (upper than 400 mV), the driver cannot discharge RWL completely resulting in increased read time, which is still about equal to other structures.

Write time is defined as the time taken between VDD/2 of write word line and the time that voltages at the storage-nodes of the cell become equal. For writing “0” and “1” in the proposed cell, both the pull-up and pull-down transistors of the left inverter (PDL1 and PUL1) are turned off, making the write operation easy. Also, in the proposed cell, given the fact that two transistors of two different types (n and p) are used for write access, this operation is much faster than other single-ended cells where it is difficult to pass “1”. However, the write operation is still slower than differential cells; because in differential cells, data is written from both sides of the cell, which speeds up the write operation. As shown in Fig. 12(a), for write “1”, at 200 mV supply voltage, the speed of the proposed cell is 5.7x higher than the WRE8T cell. Moreover, as illustrated in Fig. 12(b), the write “0” time of the proposed cell is very close to the differential cells.

3.5 Read and write power

During read and write, dynamic power is consumed in SRAM arrays due to charging and discharging of long bitline and word lines. Dynamic power consumption is formulated as

where ∝, C and f are activity factor, (bitline or word line) capacitance and frequency, respectively. As shown in Fig. 13. Read power consumption of the proposed structure and WRE8T with single-ended read is lower than other compared structures. This is attributed to the half activity factor of the bitline capacitance for the single-ended structures versus differential ones. Despite 8T (SE-DFC) is a single-ended structure, it has higher read power. This is due to the high word line capacitance and dynamic power because of the high height layout (see Table 2).

During “write” operation for single-ended structures like WRE8T and 8T (SE-DFC), the n-type access transistor is not capable to transfer ‘1’ completely. Hence, the speed of writing ‘1’ is low in these cells which leads to a reduction of frequency (f) during write ‘1’. According to Eq. (1), the power consumption of write ‘1’ is low in these structures (Fig. 14(a)). In the proposed structure, both n-type and p-type access transistors are used for full transferability (‘1’ or ‘0’), meanwhile enhanced writing process and boosted write operation frequency are results that can be derived from this idea. According to Eq. (1), it increases write ‘1’ and ‘0’ power consumption as shown in Fig. 14.

3.6 Static power consumption

With technology scaling, static power consumption increases significantly due to the lower threshold voltages and severe short channel effects such as DIBL [20]. On the other hand, SRAM cells are mostly in the hold state consuming the static power consumption [21]. Using the tristate inverter INVL in the proposed cell (Fig. 2) leads to less subthreshold current than the INV1 in the WRE8T (Fig. 1(d)). Figure 15 depicts, the INV1 and INVL inverters used in the WRE8T cell and the proposed cell during the hold state. In the hold state, WL and WLB are at zero and VDD respectively.

For the INV1 inverter, when the input is “0”, the drain-to-source voltage of the OFF transistor PD1 is equal to VDD and if the input of this inverter is “1”, the drain- to-source voltage of the OFF transistor PU1 is also equal to VDD. This causes maximum DIBL and leakage current for the inverter. However, for the proposed INVL, when the input is “0”, the Vds of the OFF transistor PD2 is equal to VDD-Vthn and when the input is “1”, the Vds of the OFF transistor PU2 is equal to VDD-Vthp. Therefore, the leakage power of the INVL is less than the leakage power of the INV1, as the leakage current has an exponential relationship with Vds due to DIBL. Moreover, from the static power perspective, the right inverter of the proposed cell INVR benefits from stacked pull-down transistors.

Furthermore, only one transistor is used for the read operation, and the control signal of the transistor (RWL) in the hold state is set to VDD. This causes the Vds of RD to be zero and thereby minimizing the transistor leakage current. As shown in Fig. 16, the proposed cell with these techniques has the lowest static power consumption among all the compared cells at all supply voltages.

3.7 Cell layout and area

Figure 17 shows the layout of the studied cells. The layouts were drawn based on FinFET design rules reported in [22]. The proposed cell has the least occupied area after the conventional 6T and 8T cells. Table 2 shows the height, width, and the area occupied by different cells. It can be seen from Table 2 that the area of the proposed cell is approximately five percent lower than the WRE8T cell.

4 Conclusion

In this paper, a low-leakage single-ended 10T SRAM cell has been proposed. This cell improves read and write yields by decoupling the storage node from the read bitline and temporarily floating the left inverter during the write operation. Moreover, since writing ‘1’ is difficult in single-ended SRAM cells, using an extra p-type access transistor parallel to an n-type access transistor mitigates the problem. Simulations in FinFET technology show that the proposed cell achieves a six-sigma (6σ) yield for read, write, and hold operations at a supply voltage down to 200 mV while other compared cells fail to have acceptable yield at the sub-threshold voltage. Also, by benefiting from the stack effect, reduced DIBL, and using only one transistor for the read operation, the proposed cell has the least static power, e.g., 4 and 24% lower than the conventional 6T and 8T cells at 200 mV, respectively. In conclusion, the proposed 10T cell is a suitable candidate for noise-immune, high-performance applications and a convenient option for low leakage demands.

References

Ahmad, S., Alam, N., & Hasan, M. (2018). Pseudo differential multi-cell upset immune robust SRAM cell for ultra-low power applications. AEU: International Journal of Electronics and Communications, 83, 366–375.

Singh, A. K., Saadatzi, M., & Venkataseshaiah, C. (2017). Design of a single-ended energy efficient data-dependent-write-assist dynamic (DDWAD) SRAM cell for improved stability and reliability. Analog Integrated Circuits and Signal Processing, 90(2), 411–426.

Singh, A. K., Seong, M. M., & Prabhu, C. M. R. (2014). A data aware 9T static random access memory cell for low power consumption and improved stability. International Journal of Circuit Theory and Applications, 42(9), 956–966.

Saeidi, R., Sharifkhani, M., & Hajsadeghi, K. (2014). Statistical analysis of read static noise margin for near/sub-threshold SRAM cell. IEEE Transactions on Circuits and Systems I: Regular Papers, 61(12), 3386–3393.

Manju, I., & Senthil Kumar, A. (2015). A 22 nm FinFET based 6T-SRAM cell design witah scaled supply voltage for increased read access time. Analog Integrated Circuits and Signal Processing, 84(1), 119–126.

Zeinali, B., Madsen, J. K., Raghavan, P., & Moradi, F. (2017). Low-leakage sub-threshold 9 T-SRAM cell in 14 nm FinFET technology. International Journal of Circuit Theory and Applications, 45(11), 1647–1659.

Jeong, H., Oh, S. H., Oh, T. W., Kim, H., Park, C. N., Rim, W., et al. (2019). Bitline charge-recycling SRAM write assist circuitry for V MIn improvement and energy saving. IEEE Journal of Solid-State Circuits, 54(3), 896–906.

Chang, L., Fried, D. M., Hergenrother, J., Sleight, J. W., Dennard, R. H., Montoye, R. K., & Guarini, K. W. (2005, June). Stable SRAM cell design for the 32 nm node and beyond. In Digest of Technical Papers. 2005 Symposium on VLSI Technology, 2005. (pp. 128–129). IEEE.

Yueh, W., Chatterjee, S., Zia, M., Bhunia, S., & Mukhopadhyay, S. (2015). A memory-based logic block with optimized-for-read SRAM for energy-efficient reconfigurable computing fabric. IEEE Transactions on Circuits and Systems II: Express Briefs, 62(6), 593–597.

Jeon, D., Dong, Q., Kim, Y., Wang, X., Chen, S., Yu, H., et al. (2017). A 23 mW Face Recognition Processor with Mostly-Read 5T Memory in 40 nm CMOS. IEEE Journal of Solid-State Circuits, 52(6), 1628–1642.

Saxena, S., & Mehra, R. (2017). Low-power and high-speed 13T SRAM cell using FinFETs. IET Circuits Devices and Systems, 11(3), 250–255.

Pasandi, G., & Fakhraie, S. M. (2014). An 8t low-voltage and low-leakage half-selection disturb-free SRAM using bulk-CMOS and FinFETs. IEEE Transactions on Electron Devices, 61(7), 2357–2363.

Pasandi, G., & Pedram, M. (2018). Internal write-back and read-before-write schemes to eliminate the disturbance to the half-selected cells in SRAMs. IET Circuits Devices and Systems, 12(4), 460–466.

Predictive Technology Model (PTM). (2007). Nanoscale Integration and Modeling (NIMO) Group. Retrieved from http://ptm.asu.edu/.

Ingerly, D., Agrawal, A., Ascazubi, R., Blattner, A., Buehler, M., Chikarmane, V., & Glassman, T. (2012, June). Low-k interconnect stack with metal-insulator-metal capacitors for 22 nm high volume manufacturing. In 2012 IEEE International Interconnect Technology Conference (pp. 1–3). IEEE.

Ansari, M., Afzali-Kusha, H., Ebrahimi, B., Navabi, Z., Afzali-Kusha, A., & Pedram, M. (2015). A near-threshold 7T SRAM cell with high write and read margins and low write time for sub-20 nm FinFET technologies. Integration, The VLSI Journal, 50, 91–106.

Anitha, D., Manjunathachari, K., Sathish Kumar, P., & Prasad, G. (2017). Design of low leakage process tolerant SRAM cell. Analog Integrated Circuits and Signal Processing, 93(4), 1–8.

Mishra, J. K., Srivastava, H., Misra, P. K., & Goswami, M. (2019). Analytical modelling and design of 9T SRAM cell with leakage control technique. Analog Integrated Circuits and Signal Processing, 101(1), 31–43.

Makino, H., Nakata, S., Suzuki, H., Mutoh, S., Miyama, M., Yoshimura, T., et al. (2011). Reexamination of SRAM cell write margin definitions in view of predicting the distribution. IEEE Transactions on Circuits and Systems II: Express Briefs, 58(4), 230–234.

Lorenzo, R., & Chaudhury, S. (2017). A novel 9T SRAM architecture for low leakage and high performance. Analog Integrated Circuits and Signal Processing, 92(2), 315–325.

Sharma, V., Gopal, M., Singh, P., Vishvakarma, S. K., & Chouhan, S. S. (2019). A robust, ultra low-power, data-dependent-power-supplied 11T SRAM cell with expanded read/write stabilities for internet-of-things applications. Analog Integrated Circuits and Signal Processing, 98(2), 331–346.

Salahuddin, S., Jiao, H., & Kursun, V. (2013, March). A novel 6T SRAM cell with asymmetrically gate underlap engineered FinFETs for enhanced read data stability and write ability. In International Symposium on Quality Electronic Design (ISQED) (pp. 353–358). IEEE.

Kushwah, C. B., & Vishvakarma, S. K. (2016). A single-ended with dynamic feedback control 8T subthreshold SRAM cell. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 24(1), 373–377.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Eslami, N., Ebrahimi, B., Shakouri, E. et al. A single-ended low leakage and low voltage 10T SRAM cell with high yield. Analog Integr Circ Sig Process 105, 263–274 (2020). https://doi.org/10.1007/s10470-020-01669-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01669-y