Abstract

A current mode multiplier is a valid structured block in many signal processing operations, such as modulation and demodulation schemes in communications, in development of bio-medical equipments, in analog computations, and fuzzy logic controllers. A single second generation current controlled conveyor (CCCII) based current mode multiplier without passive components is designed. CCCII has the eccentricity of intrinsic resistance in between the two input ports which are tunable by the external bias current. PSPICE simulator is utilized to examine the proposed design. The topology yields a simple structure and highly suitable for monolithic IC fabrication. Simulation results are confirmed with a voltage requirement of ± 2.5 V, the non linearities, total harmonic distortion (THD), and power dissipation are anticipated. Comparison of the proposed design with the existing methods is also performed. The parametric sweep and temperature analysis are also determined. The simulated results very well agree with the theoretical expectancy.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

Analog multipliers ascertain in various fields like signal processing, communication systems, instrumentation, and measurement systems. Several multiplier configurations are proposed previously using translinear bipolar transistors, MOS square law characteristics, and switching capacitors. However, they are bounded to voltage mode operations and therefore not suitable for current mode. The current mode designs have several advantages such as large dynamic range, greater linearity, large signal bandwidth, simple configuration, and low power consumption [1,2,3,4,5,6,7,8].

In contemporary world, the analog VLSI has arised as a exceptional technology for the imminent demands of large bandwidth and less power requisites. A number of multiplier topologies as such is designed based on voltage mode. The eminent fact is that the dynamic range of voltage dependent devices is uttered by the frequency dependent gain. This glitch can also be elucidated by the current mode devices. Many voltage mode and current mode multipliers based on different active building modules have been proposed in the literature, but they involve two or more active devices, having the drawback of large area constraint and dissipation of more power. Abuelma’atti [2] has developed the current mode multiplier design possessing two CCCIIs without external passive components. The configuration proposed by Erkan Yuce [3] implies a single CCCII for realization along with a current controlled grounded resistor (CCGR), which is then realized with four-bipolar junction transistors (BJTs). Many such techniques using various active devices exist in the literature that uses operational transconductance amplifier (OTA), current controlled current differencing buffered amplifier (CCCDBA), current differencing transconductance amplifier (CDTA), current controlled current differencing transconductance amplifier (CCCDTA), current follower transconductance amplifier (CFTA), current controlled current conveyor transconductance amplifier (CCCCTA), digitally programmable current conveyor (DPCCII) [9,10,11,12,13,14,15,16,17,18,19]. In this manuscript, current mode CCCII-based multiplier utilizing only one CCCII without passive components is proposed with two input current signals and one controllable bias current. Compared with the existing current mode multipliers, the main advantage of the proposed topology is that it occupies less area and low power dissipation because of having only one CCCII with no passive components for realization.

2 Second Generation Current Controlled Conveyor

Basically, CCCII is a mixed translinear loop, current mode active structured block for several analog applications. It has the additional advantage of intrinsic resistance (RB) that can be observed at input terminal X that can be varied by tuning the external bias current and thus avoids the usage of external resistor which is more preferred for IC fabrication.

The matrix relationship between input and output currents, by considering the intrinsic resistance RB into account of an basic CCCII is given in matrix form (1).

Conventionally, using (1), the plus and minus sign signify the direction of current between input port X and output port Z. If the direction of current is same, then it is a positive current conveyor (CCCII+). If the direction of current is in opposite direction, then it is a negative current conveyor (CCCII-). At port X, RB denotes the input intrinsic resistance, tuned with bias current, (RB = VT/2IB), where VT ≈ 26 mV is the voltage equivalent of temperature, and IB ≥ 0 is the external bias current of the CCCII. At node Y, the current IY is zero since the impedance at the input of node Y is infinite. Therefore, the current applied at input node X is transformed to output node Z.

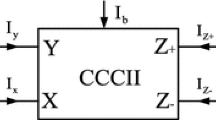

Several applications and other methods of realizing a multiplier topology are available by applying bias current to the CCCII [9,10,11,12,13,14]. Figure 1 shows the symbolic depiction of CCCII.

Transistor model of CCCII is shown in Fig. 2 in which the translinear loop is realized using bipolar junction transistors to achieve a wide frequency range. The transistor loop (M1–M4) forms a mixed translinear, DC biased by means of current mirrors (M5–M6, and M9–M10). The transistors (M11–M12, and M13–M14) are helpful to produce output current Z+ in response to the X terminal input current. The output Z- terminal is realized using additional current mirrors (M15–M17, and M18–M20), and the transconductance gain can be varied by IB.

3 Proposed Current Mode Multiplier

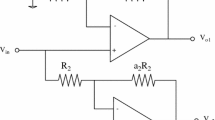

The work is organized to design a new current-based multiplier using a single CCCII, with no passive components and has various applications in current mode signal processing circuits. The proposed design of Fig. 3 can multiply two current signals and is able to operate at a broad range of frequencies. The design is insensible to temperature variations, and the output current (IZ) can be inhibited by varying the input bias current. The main advantage of the developed circuit is that it uses only one CCCII for construction which ultimately requires less area and low power. The internal structure of CCCII is as shown in Fig. 2.

Using routine design analysis for the multiplier configuration of Fig. 3, the simplified output current expression is:

Considering non-idealities, the above expression is denoted by

where α0 is the DC gain with current tracking error, and β0 is the voltage gain with voltage tracking error, which are ideally equal to unity.

4 Simulation Results

The proposed design of Fig. 3 has been simulated by using PSPICE simulator. Figure 4 shows the simulated results with the specifications shown as under. The CCCII was realized by the transistor schematic shown in Fig. 2; PR100N for PNP and NP100N for NPN transistors of bipolar group ALA400 of AT and T are utilized. The supply voltage is ± Vcc = 2.5 V, and the value of bias current is IB = 50 µA (RX = 260 Ω). The input signal frequencies are I1 = 10 Sin (2 × π × 10 × 103t) μA and I2 = 10 Sin (2 × π × 100 × 103t) μA. The total harmonic distortion (THD) of the proposed multiplier circuit is 1.876%, and the total power dissipation is 3.74 mW. The harmonic distortion and power dissipation values are quite low and reasonably good.

The simulated outcome of Fig. 3 represents the multiplication of two sinusoidal currents

Figure 5 is the frequency spectrum of the proposed design, and Fig. 6 shows the variation of bias current versus the output current; the input signal frequencies are I1 = 10 Sin (2 × π × 10 × 103t) μA, and I2 = 10 Sin (2 × π × 100 × 103t) μA are preserved constant. The graph imitates the closeness of theoretical and simulated results for the variation of bias current over a range of 50–250 µA.

Figure 7 is the graphical representation of total harmonic distortion versus the bias current. The bias current is varied over a range of 50–250 µA, and the observed distortion is in the range of 3.912 × 10−3 to 0.7824 × 10−3. The THD is 1.876%, which is very low. Figures 8 and 9 are also the graphical interpretation confirming the variation of amplitudes of output current over the variation of temperature from 0 °C to a maximum of 150 °C. It reflects the insensitiveness over the temperature variations, keeping the input signal frequencies I1 = 10 μA Sin (2 × π × 10 × 103t), and I2 = 10 μA Sin (2 × π ×100 × 103t) unaltered (Table 1).

The proposed multiplier employs a single CCCII with no passive components for the realization. The design of [3] consists of a single CCCII and one current controlled grounded resistor (CCGR), which is then realized with four BJTs and is able to produce a total harmonic distortion up to 5%. The design of [9] has been involved with 3 CCDDCCs along with a capacitor, and its distortion is 0.8% for a 0.6 VPP. The configuration of [10] has the advantage of using a single CFCTA with no passive components, but suffers a distortion of 4% which is less preferred. Whereas the design of [12] has the advantage of having less distortion of 1.21%, but at a cost of 3 op-amps, 6 resistors, and 2 CMOS transistors for its construction. It requires 1 CDBA and 6 MOS transistors for the implementation of the design of [13]. Referring to all the above designs, the advantages of the proposed design are that it requires only one CCCII with no passive components and offers low distortion and also highly suitable for monolithic IC fabrication.

5 Conclusion

A current mode multiplier design is developed, having no capacitors or resistors involved which is suitable for IC fabrication. The total harmonic distortion and power dissipation are evaluated that are 1.876% and 3.74 mW, respectively. To improve the potency of the design, the non-linearity, frequency spectrum, and temperature insensitivity are determined. The simulation results for the variation of bias current with respect to the THD are verified and found satisfactory. The proposed design is compared with the existing methods and tabulated. Thus, the reported multiplier design has a simple structure that requires small area and dissipates low power over the other existing technologies.

References

Sedra S, Roberts GW, Gohh F (1990) The current conveyor: history, progress and new results. IEE Proc Part G Circ Dev Syst 137(2):78–87. https://doi.org/10.1049/jp-g-2.1990.0015

Abuelma’atti MT, Al-Qahtani MA (1998) A current-mode current controlled current conveyor based analogue multiplier/divider. Int J Electron 85(1):71–77. https://doi.org/10.1080/002072198134364

Yuce E (2008) Design of simple current mode multiplier topology using a single CCCII+. IEEE Trans Instrum Measur 57(3):631–637. https://doi.org/10.1109/tim.2007.910112

Srinivasulu A, Pal D (2016) CCII + based novel waveform generator with grounded resistor/capacitor for tuning. In: Proceedings of IEEE applied electronics 2016 international conference, Czech Republic, pp 247–251. https://doi.org/10.1109/ae.2016.7577283

Mahendranath B, Srinivasulu A (2017) An output buffer for +3.3 V applications in A 180 nm +1.8 V CMOS technology. Radioelectr Commun Syst 60(11):512–518. https://doi.org/10.3103/s0735272717110061

Krishna PVSM, Srinivasulu A, Lal RK (2015) Two new first order all pass filters based on differential difference complementary current conveyor. Int J Cont Theo Appl 8(1):140–148

Linitha R, Srinivasulu A, Reddy, VV (2015) A Schmitt trigger based on DDCCTA without any passive components. In Proceedings of IEEE international conference on communication and signal processing, India, April 2–4, pp 1695–1698. https://doi.org/10.1109/iccsp.2015.7322808

Sivakumari K, Srinivasulu A, Reddy VV (2014) A high slew rate, low voltage CMOS class-AB amplifier. In: Proceedings of IEEE applied electronics 2014 international conference, Czech Republic, pp 267–270. https://doi.org/10.1109/ae.2014.7011717

Prommee P, Somdunyakanok M (2009) CMOS based current controlled DDCC and its applications to capacitance multiplier and universal filter. Int J Electron Commun:1–8. https://doi.org/10.1016/j.aeue.2009.12.002

Tuntrakool S, Suwanjan P, Jaikla W (2017) Temperature insensitive current-mode four quadrant multiplier using single CFCTA. MATEC Web Conf 95:1–4. https://doi.org/10.1051/matecconf/20179514001

Sawigun C, Serdijn WA (2009) Ultra low power, class-AB, CMOS four quadrant current multiplier. Electron Lett 45(10):483–484. https://doi.org/10.1049/el.2009.3311

Roy S, Paul TK, Pal RR (2017) A new method of realization of four quadrant analog multiplier using operational amplifiers and MOSFETs. J Phy Sci 22:163–173

Pathak JK, Singh AK, Senani R (2014) New multiplier/divider using a single CDBA. Am J Elect Electron Eng 2(3):98–102. https://doi.org/10.12691/ajeee-2-3-7

Saatlo AN, Ozoguz IS (2016) Design of a high-linear, high-precision analog multiplier, free from body effect. Turk J Electr Eng Comput Sci 24:820–832. https://doi.org/10.3906/elk-1307-159

Srınıvasulu A, Rukmini MSS, Sarada M, Ram MP, Prasad S (2014) Pulse width modulator based on second generation current conveyor. In: Proceedings of the IEEE international conference on devices, circuits and communications, pp 1–4, Ranchi, India. https://doi.org/10.1109/icdccom.2014.7024740

Avırenı S (2011) Current conveyor based Schmitt trigger and its applications as a relaxation oscillator. Int J Circ Theo Appl 39(6):679–686. https://doi.org/10.1002/cta.669

Bhargav A, Srinivasulu A, Pal D (2018) An operational transconductance amplifiers based sinusoidal oscillator using CNTFETs. In: Proceedings of the 23rd IEEE international conference on applied electronics, Pilsen, Czech Republic, 6p. https://doi.org/10.23919/ae.2018.8501428

Suma M, Reddy VV, Srinivasulu, A (2016) Current mode Schmitt trigger based on ZC-current differencing transconductance amplifier. In: Proceedings of IEEE international conference on inventive computation technologies, Coimbatore, pp 1–5. https://doi.org/10.1109/inventive.2016.7823226

Srivyshnavi T, Srinivasulu A (2015) A current mode Schmitt trigger based on current differencing transconductance amplifier. In: Proceedings of 3rd IEEE international conference on signal processing, communication and networking, pp 1–4. https://doi.org/10.1109/icscn.2015.7219884

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Zahiruddin, S., Srinivasulu, A., Sarada, M. (2021). A New Current Mode Multiplier Using Single CCCII Without Passive Components. In: Reddy, M.J.B., Mohanta, D.K., Kumar, D., Ghosh, D. (eds) Advances in Smart Grid Automation and Industry 4.0. Lecture Notes in Electrical Engineering, vol 693. Springer, Singapore. https://doi.org/10.1007/978-981-15-7675-1_10

Download citation

DOI: https://doi.org/10.1007/978-981-15-7675-1_10

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-7674-4

Online ISBN: 978-981-15-7675-1

eBook Packages: EnergyEnergy (R0)