Abstract

In this paper, a novel CMOS circuit of second-generation current controlled conveyor (CCCII) is proposed, which offers wide input voltage range and large 3 dB bandwidth of voltage–current transfer gain with high linearity under low supply voltage. The core of this CCCII adopts cross-coupled differential transistor pair as input stage instead of conventionally source-coupled and the principle of the circuit is analyzed theoretically in detail. This CCCII is implemented by PSPICE program in TSMC 0.18 µm RF CMOS technology and verified by simulation results. A current-mode universal filter which consists of two proposed CMOS CCCIIs is also simulated to validate the feasibility of the new circuit topology.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The current-mode (CM) circuits have received significant attentions in recent years as they have advantages of high slew-rate, wide bandwidth, small nonlinear distortion, large dynamic-range and so on. The Second-Generation Current Conveyor (CCII) is introduced in 1970 [1], and it is a versatile and flexible building block in current-mode analog circuit design [2–8]. However, CCII has two main drawbacks: (1) large voltage tracking error from terminal Y to terminal X because of the parasitic resistor of terminal X, which leads to transfer function error; (2) lack of electronically tunable feature, which means the parameters can not be adjusted by additional bias current.

In 1996, A. Fabre proposed a CCCII [9]. It possesses electronically tunable function by utilizing the parasitic floating intrinsic transimpedance at port X (RX), which can be tuned electronically by adjusting the bias current.

In the past, the core of CCCII is simply constructed by the mixed translinear-loop, which is originally realized in BJT [10, 11] and later in MOSFET [12–15]. BJT has advantages of low noise and high operating frequency, but it is not compatible with CMOS VLSI technology, so it is inconvenient for VLSI integration. Minaei proposed a CMOS CCCII circuit based on MOS translinear loop in 2002 and Al-Shahrani proposed a CMOS CCCII based on source-coupled differential pair input stage in 2003 [16]. However, the CCCII based on MOS translinear-loop has unsymmetrical dynamic-range and strict restrictive condition in fabrication technology. Meanwhile, CMOS CCCII based on source-coupled differential pair has poor input voltage range and low linearity. Hence, the objective of this paper is to present a new CMOS CCCII with high linearity to overcome the problems mentioned above, then it can be better applied in more application fields [17–25], such as chaotic system, oscillators, current mode filters, radio frequency oscillators, low noise amplifiers, ASK/FSK modulators and so on [26–28].

This paper is organized as follows: the cross-coupled differential pair input stage and the proposed novel CMOS CCCII are described in Sects. 2 and 3, respectively. The PSPICE simulation results of this proposed CCCII circuit in TSMC 0.18 μm CMOS RF technology and performance comparison with other reported circuits are included in Sect. 4. To further illustrate merits of this proposed CMOS CCCII, A current-mode universal filter is simulated in Sects. 5 and 6.

2 The Cross-Coupled Differential Pair Input Stage

Assuming that all MOSFET are enhancement-mode types and biased in saturation region with substrates connected to their respective sources. Then the body effect is ignored and the transistor drain current can be approximated by the relation [29]:

where V GS is gate-source voltage, V TH is the threshold voltage, k = (W/L)μC ox /2 is the trans- conductance parameter, W and L are width and length of the transistor channel, μ is the effective surface carrier mobility and C ox is the gate oxide capacitance per unit area. The channel length modulation effect is not included in (1).

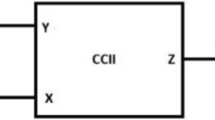

The CCCII circuit symbol is illustrated in Fig. 1 and its ideal defining equation can be given as [12]:

In Fig. 1, terminal X is a current input which possesses low input impedance; terminal Y is a voltage input which possesses high input impedance; Z+ is the non-inverting current output port, and Z− is the inverting current output port. Ib is the biasing current, by which the voltage relation between terminal X and terminal Y is adjustable.

The current output at port Z(iz), which is conveyed from the input current at port X(ix), can be expressed as [14]:

As R x is the parasitic resistance, the CCCII-based application can be realized in resistor-free and tunable architectures by utilizing R x as the adjustable circuit parameter. To better understand the function of CCCII, the equivalent circuit of it is displayed in Fig. 2.

Considering a matched transistor pair (Mn1, Mn2) coupled by two voltage sources with equal value of \( ({\text{V}}_{\text{TH}} + {\text{V}}_{x} ) \), which is shown in Fig. 3. Representing \( (V_{2} - V_{1} ) \) by ν, using (1) gives:

The output current \( i_{x} = I_{1} - I_{2} \), obtained by a simple p-channel current mirror, will be

Thus this configuration exhibits a perfectly linear transconductance of value \( G_{m} = 4kV_{x} \).

3 The Proposed CMOS CCCII

Considering a actual implementation of the circuit described in Fig. 3, the sources \( ({\text{V}}_{\text{TH}} + {\text{V}}_{x} ) \) are substituted by two additional n-channel transistors (Mn3 and Mn4) biased by constant currents. The practical circuit configuration is displayed in Fig. 4. Mn1 and Mn4 share a same p-well connected to their common source node, whereas Mn2 and Mn3 are in a separate well to avoid back-gate bias effects. For obtaining reasonable voltage sources with low source impedance, these devices must be biased with currents which are larger than the signal currents through them.

Mn1, Mn2, Mn3 and Mn4 have the same channel length, but the channel widths of Mn3 and Mn4 are made n times wider than Mn1 and Mn2. For maintaining the value of \( {\text{V}}_{b} = \sqrt {{{I_{0} } \mathord{\left/ {\vphantom {{I_{0} } k}} \right. \kern-0pt} k}} \), Mn3 and Mn4 are biased with nI 0 . Defining normalized variables \( {\text{X}} = {{{\text{V}}_{\text{XY}} } \mathord{\left/ {\vphantom {{{\text{V}}_{\text{XY}} } {{\text{V}}_{\text{b}} }}} \right. \kern-0pt} {{\text{V}}_{\text{b}} }} \) and \( {\text{Y}} = {{i_{x} } \mathord{\left/ {\vphantom {{i_{x} } {\text{I}}}} \right. \kern-0pt} {\text{I}}}_{ 0} \) with reference to Fig. 4, we write:

where

and

The output \( {\text{Y}} = {{i_{x} } \mathord{\left/ {\vphantom {{i_{x} } I}} \right. \kern-0pt} I}_{ 0} = {{\left( {i_{1} + i_{2} } \right)} \mathord{\left/ {\vphantom {{\left( {i_{1} + i_{2} } \right)} {I_{0} }}} \right. \kern-0pt} {I_{0} }} \) is obtained as

We can change the formula by following equation

From (6c) and (7), the estimation of symmetrical dynamic-range of the cross-coupled input stage is

and the roughly linear input range is

For n = 10, in order to obtain better than 1 percent linearity, the actual linear input range is

During the linear input range, we know the parasitic resistor is

For large n, we can obtain wider linear input range. For n = 1, we obtain \( \alpha = 2 \), \( \beta = 0.25 \), \( \gamma = 0 \), and the two equations become identical. With the value of n is increased, β becomes smaller, resulting in improved linearity in the transfer characteristics. For \( n > > 1 \), from (6c) we get \( \alpha \cong 4 \), \( \gamma \cong 1 \), and \( \beta \cong {1 \mathord{\left/ {\vphantom {1 n}} \right. \kern-0pt} n} \). In the limit as \( n \to \infty \), \( \beta \to 0 \) and a linear parasitic resistance \( R_{x} = {1 \mathord{\left/ {\vphantom {1 {4\sqrt {kI_{0} } }}} \right. \kern-0pt} {4\sqrt {kI_{0} } }} \) is obtained over the entire range \( \left| X \right| \le 1 \) (i.e.\( \left| {V_{XY} } \right| \le \sqrt {{{I_{0} } \mathord{\left/ {\vphantom {{I_{0} } k}} \right. \kern-0pt} k}} \)). Furthermore, the circuit is also operated for input voltages well outside this range, though in a nonlinear fashion. The maximum available input current is \( \left( {n + 1} \right)I_{0} \).

Figure 5 shows the proposed CCCII ± circuit, of which the Z ± differential pair is identical to the active loaded NMOS differential pair of the input stage. For maintaining the same value of drain current, Mn5 and Mn6, Mn7 and Mn8 have the same size of Mn1 and Mn2, while biased with I0.

For the Z+ differential pair of Fig. 5, we can get:

Therefore, the \( i_{x} \) and \( i_{z} \) are approximated equal through the condition shown in (15):

The Z− differential pair which horizontally flipped from the Z+ differential pair yields:

From (16) and (17), we can get:

In summary, any required output properties of the CCCII can be generated by putting the appropriate Z+ or Z− pairs in concurrent with the NMOS differential pair of the input stage. Three types of differential pairs illustrated in Fig. 6 are fundamental blocks for synthesizing a CCCII. As the input stage differential pairs must be existed, the number and type of output pairs can be selected to fulfill the requirement.

4 Performance Simulations

The proposed CMOS CCCII in Fig. 5 is simulated by PSPICE program. In the simulation process, the W/L ratios of each MOS transistor are shown in Table 1 and TSMC 0.18 µm CMOS RF technology parameters are used.

The circuit uses 14 transistors with a ±1.5 V voltage supply and the DC biased current is 50 µA. From Table 1, we can get that Mn3 and Mn4 are made ten times wider than Mn1 and Mn2 with the same channel length of 0.18 µm.

In order to validate the correctness of (2), the static characteristic is firstly analyzed. By conducting DC scan for Y port, the voltage relationship between X and Y port is obtained and charted in Fig. 7. From the curve we can find that voltages of X and Y port meet the voltage relationship of (2) with very low offset-voltage. It exhibits a linear one-to-one voltage following characteristic over large voltage range as well as DC current transfer characteristics displayed in Fig. 8, but has little poor follower characteristic at port Z+.

In Fig. 9, the small signal current gain characteristics between terminals Z+ and X with grounded node Y is displayed. It is clearly that the 3 dB bandwidth of current gain approximates about 7.78 GHz. Fig 10 shows the small signal voltage gain between terminals X and Y when node Z is grounded. The 3 dB bandwidth of voltage gain is 11.61 GHz.

Table 2 compares the main performances of the proposed new CCCII described in Fig. 5 with those recently published relevant works. All these simulation results are obtained under a bias current of I0 = 50 μA. The symbols α0 and β0 represent current transfer (between X and Z) and voltage transfer (between Y and X), respectively. As exhibited in Table 2, the CCCII of Fig. 5 provides higher input impedance in Y port, wide input voltage range and higher 3 dB bandwidth for current and voltage gain.

Figure 11 shows the characteristics of R x at terminal X, and it is denoted that the simulation result of R x is nearly equal to 2.25 kΩ in the frequency range from 1 to 630 MHz at bias current I0 = 100 µA. Different R x values are also obtained at various bias current in the figure, which indicates that the transresistance of the new CCCII is electronically tunable in large bias current range.

5 Application of the CCCII to Current-Mode Filter

The CCCII can be made electronically adjustable in different applications. In this section, a novel universal filter with single-input, triple-output employing only four elements (include two proposed CCCIIs) is presented in Fig. 12.

This filter contains only two capacitors without requirement of any additional passive resistance and its structure can be characterized by the following expressions [26]:

Then the transfer function of this circuit is given as follows:

Equations (21)–(25) show that the proposed filter produces bandpass, lowpass, highpass, bandreject and all-pass responses simultaneously at its outputs. The natural frequency and the quality factor of the proposed circuit can be obtained as [26]:

The validity of the proposed filter is verified using PSPICE. For these simulations, the passive components are configured as C1 = C2 = 1nF and CCCIIs are implemented using the model in Fig. 5. The voltage supplies are taken as ±1.5 V and the bias current IB1 = IB2 = 100 µA. The results shown in Fig. 13 validate the feasibility of the proposed filter topology. By changing the bias current value of the two CCCIIs, the function of this filter can be adjusted.

6 Conclusion

This paper proposes a new CMOS CCCII based on cross-coupled differential transistor pair instead of source-coupled as input stage. By using cross-coupled differential transistor pair and other improvements in circuit design, the presented topology has merits of wide input voltage range and improved maximum operational frequency with competitive linear performance under lower supply voltage. Simulation results obtained from PSPICE shows that the proposed circuit not only meets the port characteristics of standard CMOS CCCII but also conforms theoretical behavior prediction. As compared with previously reported works and analyzed a universal filter based on it, the proposed CCCII can be potentially applied in many fields for accomplishing high performance circuit systems.

References

Sedra, A., & Smith, K. (1970). A second generation current conveyor, and its applications. IEEE Transactions on Circuits Theory, 17(1), 132–134.

Kurashina, T., Ogawa, S., & Watanabe, K. (2002). A CMOS rail-to-rail current conveyor. IEICE Transactions on Fundamentals, E85-A(12), 2894–2900.

Toumazou, C., Lidgey, F. J., & Haigh, D. G. (1990). Analog IC design: The current mode approach. London: Peter Peregrinus.

Karybakas, C. A., & Papazoglou, A. (1999). Low-sensitive CCII-based biquadratic filters offering electronic frequency shifting. IEEE Transactions on Circuits and Systems II: Analog And Digital Signal Processing, 46(5), 527–539.

Martinez, P. A., Sabdall, J., Aldea, C., & Celma, S. (1999). Variable frequency sinusoidal oscillators based on CCII+. IEEE Transaction on Circuits and Systems I: Fundamental Theory and Applications, 46(11), 1386–1390.

Khan, A. A., Bimal, S., Dey, K. K., & Roy, S. S. (2005). Novel RC sinusoidal oscillator using second generation current conveyor. IEEE Transactions on Instrumentation and Mearsurement, 54(6), 2402–2406.

Hwang, Y.-S., Liao, L., Tsai, C.-C., et al. (2005). A new CCII-based pipelined analog to digital converter. In IEEE international symposium on circuits and systems, pp. 6170–6173.

Fabre, A., Saaid, O., Wiest, F., & Boucheron, C. (1995). Current controlled bandpass filter based on translinear conveyors. Electronics Letters, 31(20), 1727–1728.

Fabre, A., Saaid, O., & Boucherron, C. (1996). High frequency applications based on a new current controlled conveyor. IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, 43(2), 82–91.

Kiranon, W., Kesorn, J., & Wardkein, P. (1996). Current controlled oscillator based on translinear conveyors. Electronics Letters, 32(15), 1330–1331.

Abuelmaatti, M. T., & Al-Qahtani, M. A. (1998). A new current-controlled multiphase sinusoidal oscillator using translinear current conveyors. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 45(7), 881–885.

Ozoguz, S., Tarim, N., & Zeki, A. (2001). Realization of high-Q bandpass filters using CCCIIs. In Proceedings of the 44th IEEE 2001 midwest symposium on circuits and systems, pp. 134–137.

Minaei, S., Kaymak, D., Ibrahim, A. M., & Kuntman, H. (2002). New CMOS configurations for current-controlled conveyors (CCCIIs). In Proceedings of the 1st IEEE international conference on circuits and systems for communications (ICCSC ‘02). pp. 62–65.

Katoh, T., Tsukutani, T., Sumi, Y., & Fukui, Y. (2006). Electronically tunable current-mode universal filter employing CCCIIs and grounded capacitors. In International symposium on intelligent signal processing and communications (ISPACS ‘06), pp. 107–110.

Xi, Y., & Liu, L. (2008). A novel CMOS current controlled conveyor II and its applications. In International conference on intelligent computation technology and automation (ICICTA), pp. 631–637.

Al-Shahrani, S. M., & Al-Absi, M. A. (2003). New realizations of CMOS current controlled conveyors with variable current gain and negative input resistance. In IEEE 46th midwest symposium on circuits and systems, pp. 43–46.

Sagbas, M., & Fidanboylu, K. (2004). Electronically tunable current-mode second order universal filters using minimum elements. Electronics Letters, 40(1), 2–4.

Anuntahirunrat, K., Tangsrirat, W., Riewruja, V., & Surakampontron, W. (2000). Sinusoidal frequency doubler and full-wave rectifier using translinear current controlled conveyors. In IEEE Asia-Pacific conference, pp. 166–169.

Siripruchyanun, M., Koseeyaporn, P., Koseeyaporn, J., & Wardkein, P. (2004). Two low-voltage high-speed CMOS frequency-insensitive PWM signal generators based on relaxation oscillator. In Proceedings of the 2004 international symposium on circuits and systems, pp. 549–552.

Kiranon, W., Kesorn, J., Sangpisit, W., & Kamprasert, N. (1997). Electronically tunable multifunctional translinear-C filter and oscillator. Electronics Letters, 33(7), 573–574.

Abuelmaatti, M. T., & Al-Qahtani, M. A. (1999). On the realization of the current controlled current-mode amplifier using the current controlled conveyor. International Journal of Electronics, 86(11), 1333–1340.

Masmoudi, D. S., Salem, S. B., Loulou, M., & Kamoun, L. (2004). A radio frequency CMOS current controlled oscillator based on a new low parasitic resistance CCII. In International conference on electrical, electronic and computer engineering, pp. 563–566.

Seguin, F., Godara, B., Alicalapa, F., & Fabre, A. (2004). A gain-controllable wide-band low-noise amplifier in low-cost 0.8 μm Si BiCMOS technology. IEEE Transactions on Microwave Theory and Techniques, 52(1), 154–160.

Abuelmaatti, M. T. (2002). New ASK/FSK/PSK/QAM wave generator using a single current-controlled multiple output current conveyor. International Journal of Electronics, 89(1), 35–43.

Chen, F., & Leung, B. (1997). A 0.25-mW low-pass passive sigma-delta modulator with built-in mixer for a 10-MHz IF input. IEEE Journal of Solid-State Circuits, 32(6), 774–782.

Chunhua, W., Haiguang, L., & Yan, Z. (2008). A new current-mode current-controlled universal filter based on CCCII. Circuits, Systems & Signal Processing, 27(5), 673–682.

Hamed, H. F. A. (2003). Low voltage low power highly linear CCIIs and its applications. In Proceedings of the 15th international conference on microelectronics, pp. 59–62.

Costas, P., & George, S. (2010). Low-voltage current controlled current conveyor. Analog Integrated Circuits and Signal Processing, 63(1), 129–135.

Chaisricharoen, R., Chipipop, B., & Sirinaovakul, B. (2010). CMOS CCCII: Structures, characteristics, and considerations. International Journal of Electronics and Communications (AEU), 64(6), 540–557.

Acknowledgments

This work is supported by the National Natural Science Foundation of China (No. 61274020), the Open Fund Project of Key Laboratory in Hunan Universities (No. 13K015), Scientific Research Fund of Hunan Provincial Education Department (No. 12C0918) and Changsha Aeronautical Vocational and Technical College (No. YC1203).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lv, Z., Chunhua, W. A Novel CMOS CCCII Based on Cross-Coupled Differential Transistor Pair and Its Application. Wireless Pers Commun 85, 2295–2307 (2015). https://doi.org/10.1007/s11277-015-2905-1

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-015-2905-1