Abstract

This paper presents a new current mode implementation of a balanced-output-signal generator that utilizes an operational floating current conveyor (OFCC) as a basic building block. The OFCC, as a current-mode device, shows flexible properties with respect to other current or voltage-mode circuits. The advantages of the proposed current mode balanced-output-signal generator (CMBG) are threefold. Firstly, it offers an accurate phase and amplitude performance over a wide bandwidth without requiring matched resistors. Secondly, it has a differential input and it can provide either current or voltage outputs. Finally, the proposed CMBG circuit offers a significant improvement in accuracy compared to other CMBGs based on the current conveyor. The proposed CMBG has been analyzed, simulated and experimentally tested. The experimental results verify that the proposed CMBG outperforms existing CMBGs in terms of the number of basic building blocks used and accuracy.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Generating a balanced-output-signal from a sinusoidal input over a large frequency range is used in many application areas, such as synchronous detection [1] and lock-in-based systems [2]. Also, signals which are both amplitude matched and phase balanced are very important in the transmission of analog signals over long lines in order to reject unwanted common mode signals [3]. Nowadays, lab-on-a-chip which requires the integration of the actuation and sensing parts, as well as the read-out circuitry in a single chip, needs also a wide bandwidth balanced-output-signal generator to generate two 180° out-of-phase signals from a sinusoidal input [4].

The voltage-mode balanced-output-signal generators (VMBG) based on an operational amplifier, as shown in Figs. 1 and 2, require the matching of amplifier poles [5, 6]. Also, due to the fixed gain bandwidth product of the operational amplifier, the system cannot simultaneously provide both a minimum phase-difference error between the outputs and minimum amplitude difference without compromising the bandwidth performance of the system. Additionally, VMBGs require precise resistor matching to achieve high common-mode rejection ratio (CMRR) [5, 6].

Circuit proposed in Ref. [5] for 180o out-of-phase signals

Circuit proposed in Ref. [6] for 180o out-of-phase signals

A current-mode balanced output signal generator (CMBG) is used as shown in Fig. 3 [7]. It uses two op-amps working in conjunction with two second-generation current conveyors (CCII). Unlike the circuits in Ref. [5] and [6], this circuit does not require precise matching of amplifier poles. However, when this circuit, see Fig. 3, works in a single ended input mode, i.e., vin1 is active and vin2 is grounded, the phase difference and the amplitude between vo1 and vo2 are: [7]

Two CCII+ used in conjunction with two Op-amps CMBG, Ref. [7]

Equation (1) shows that there is a phase error [tan−1(ωC 1 R G )] which increases with both the frequency and RG. Thus in order to minimize the phase error, RG should be as small as possible. Equation (2) also indicates an increase of the output-signal amplitude difference (error) with frequency and with RG. Additionally, this approach suffers from higher power consumption and a more complicated circuit topology when compared with the topologies shown in Figs. 1 and 2. Recently, a CMBG based on four CCIIs is presented [8] and is shown in Fig. 4, where the two Op-amps (OP1 and OP2) in Fig. 3, are replaced by two CCIIs. Figure 4 is taking into consideration the equivalent input resistance at X terminal (RX) of the CCIIs. This circuit used only CCII as a building block. However, this circuit has the same issue associated with the circuit shown in Fig. 3, i.e., when works in a single ended input mode, vin1 is active and vin2 is grounded, the phase difference and the amplitude between vo1 and vo2 are exactly the same ones given in Eqs. (1) and (2). Thus, it suffers from increasing the output-signal amplitude difference (error) with frequency and with RG.

Four CCII+ based CMBG, Ref. [8]

In this paper, the new proposed CMBG circuit has the following advantages: (1) it is simple and has symmetric circuit topology, (2) it has much improved amplitude and phase difference compared with the other voltage or current-mode balanced output signal generators, and (3) it has a differential input and it can provide either a balanced output current or voltage. The proposed CMBG circuit is based on the Operational Floating Current Conveyor (OFCC), which exhibits flexible characteristics with respect to other current-mode or voltage-mode devices [9–13]. The remainder of this paper is organized as follows:

Section 2 introduces and reviews the basic concept of the OFCC and its characteristics. Also, a simple model of the OFCC, as well as, the effect of feedback on the OFCCs performance are presented and discussed. A detailed analysis of the proposed CMBG is presented in Sect. 3. Section 4 presents the simulation and experimental results. Section 5 discusses the performance of the proposed CMBG and compares it to the performance of currently used CMBGs. Section 6 concludes the paper and discusses the merits of the proposed CMBG based on the experimental findings.

2 The operational floating current conveyor (OFCC)

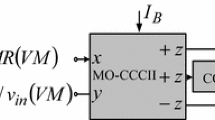

The OFCC is a five-port network, comprised of two inputs and three output ports, as shown in Fig. 5 [9–13]. In this diagram, the port labeled X represents a low impedance current input, port Y is a high impedance input voltage, W is a low impedance output voltage, and Z+, and Z− are the high impedance current outputs with opposite polarities. The OFCC operates where the input current at port X is multiplied by the open loop transimpedance gain Zt to produce an output voltage at port W. The input voltage at port Y appears at port X and thus a voltage tracking property exists at the input port. Output current flowing at port W is conveyed in phase to port Z+ and out of phase with that flowing into port Z−, so in this case a current tracking action exists at the output port. Thus, the transmission properties of the ideal OFCC can be conveniently described as:

where iy and vy are the inward current and voltage at the Y port, respectively, as shown in Fig. 5. ix and vx are the input current and voltage at the X port, respectively. iw and vw are the output current and voltage at W port, respectively. iz+ and vz+ are the output current and voltage at Z + port, respectively. Similarly, iz- and vz- are the output current and voltage at the Z− port, respectively. Zt represents the impedance between X and W ports.

The OFCC can be implemented by applying the principle of supply current sensing to a current feedback (CFB) op-amp [14] such as illustrated in Fig. 6. The current mirrors CM1 and CM2 establish the output current at port Z+. Also, CM1 and CM2 and their cross-coupling with the current mirrors CM3 and CM4 through the current steering transistors CS1 and CS2 generate a complementary output current at port Z−. The OFCC is basically designed to be used in a closed loop configuration, with current being fed back from port W to port X [9].

2.1 A simple model

A simple model of the OFCC based on the circuit topology shown in Fig. 6 is illustrated in Fig. 7. In this figure, Rx and Ry are the resistances of the CFB op-amp at negative (−) and positive (+) ports, respectively. Cx and Cy are the input capacitances of CFB op-amp (−) and (+) ports, respectively. RT and CT are the small signal resistance and internal compensation capacitance of the CFB op-amp. RZ+ and RZ− are the small signal output resistances of the respective current mirrors at node Z+ and Z−, respectively at the d.c. operating point. CZ+ and CZ− represent the output capacitances of the respective current mirrors at nodes Z+ and Z−, respectively.

The OFCC’s model, Ref. [10]

2.2 OFCC with feedback

The OFCC, unlike the CCII, is designed with a feedback resistor between W and X, i.e. negative feedback between W and X. This feedback resistor allows the OFCC to operate at a positive or negative current-conveyor while simultaneously reducing the input resistance at X port [11]. Also, the negative feedback improves the dc stability as well as the transfer function accuracy [7, 9, 10].

To understand why the input resistance at the X terminal is reduced by negative feedback, consider the OFCC with feedback resistor RW, as shown in Fig. 8. The capacitive reactance to ground due to Cx is quite high and can therefore be ignored in the frequency range of interest. In this case, the input current iin is defined as:

and,

where vin is the input voltage at port X, vw is the output voltage at port W, Rw is the feedback resistance, i1 is the feedback current, and i.e. is the error current.Using Eq. (3), the output signal voltage vw is given as,

where Zt = RT//(1/jωCT). For low frequencies (ω < <1/RTCT) the reactance due to CT is very high and can be ignored. Thus Zt ≈ RT and

Now since the Y port is connected to ground, v2 = 0, and therefore the error current is defined as:

By substituting Eqs. (5), (7), and (8) in (4), iin can be expressed as

The low frequency input resistance at X port can therefore be expressed as,

Circuit to measure OFCC’s RX, Ref. [10]

With typical resistor values of: Rx = 50 Ω, Rw = 1 KΩ, and RT = 200 MΩ. Equation (10) yields Rin = 0.0025 Ω. Therefore, the input resistance at X is greatly reduced, thus minimizing the voltage tracking error between X and Y, and therefore can be neglected at low frequencies.

3 The proposed CMBG

The proposed CMBG consists of two operational floating current conveyors (OFCC), two feedback resistors (RW1 and RW2), a gain determined resistor (RG) and a ground loads (RL1 and RL2), as shown in Fig. 9. The two OFCC are arranged such that the output current into the load resistor RL1 is equal and 180o out of phase of the current into RL2. C1 and C2 are the parasitic capacitances at the inverting input (X) of OFCC1 and OFCC2, respectively, while CZ1, and CZ2 are that parasitic capacitances at the outputs.

Taking into consideration both the voltage and current tracking errors of the OFCC, the current tracking error between ports X, Z + and Z− is:

and

where: \(\varepsilon_{ + }\) and ε- denotes the finite current tracking error at the high impedance output Z+ and Z−, respectively. Thus, the port currents may then be expressed as \({\text{i}}_{{{\text{z}} + }} = \alpha {\text{i}}_{\text{x}}\) and \({\text{i}}_{{{\text{z}} - }} = \gamma {\text{i}}_{\text{x}}\).The voltage tracking error between ports X and Y is defined as:

where εV denotes the finite voltage tracking error at the low impedance X from the high input impedance node Y.The voltage at nodes vA and vB, as shown in Fig. 9, can be expressed as:

where β 1 and β 2 are the voltage tracking error of OFCC (1) and OFCC (2), respectively. Because of the effect of the OFCC, the voltage transfer error is zero, i.e., β 1 = β 2 = 1 [9–12]Thus,

The current i x can be expressed as:

3.1 Differential input mode

For the differential Input mode, \(v_{{\rm {in1}}} = \, - v_{{\rm {in2}}} = \frac{{v_{d} }}{2}\). The resulting current i x and i 4 can be calculated as:

Similarly,

The output currents i 5 and i 6 are calculated as follows:

The output voltages v o1, and v o2 are:

where C Z1 and C Z2 are the output node capacitance at Z + , Z− terminals which are in parallel with RL1 and RL2.

Using i5 and i6 from Eqs. (22) and (23), respectively, v o1 and v o2 can now be computed,

The phase differences Φ 1, and Φ 2 of v o1 and v o2 are given by:

The output phase difference ΔΦ 12 is given by:

The output signal amplitude difference Δv12 can be calculated from (26) and (27)

For ideal OFCCs, α1 = γ1 = 1, thus the output voltage is:

Assuming matched resistors and capacitors, i.e., R L1 = R L2 and Cz1 = Cz2. ∆φ 12 = 180° and ∆v 12 = 0 dB, i.e., the phase and amplitude errors disappear. v o1 and v o2 therefore become balanced amplitude-matched signals. The mismatching impacts of R L1, R L2 and Cz1 and Cz2 will be discussed and investigated in details in part 4.

3.2 Single ended input mode

For a single ended input, v in1 = v 1 and v in2 = 0, then i x and i 4 can be expressed as:

and

Using a routine circuit analysis we can prove that:

The phase differences Φ 1 and Φ 2 of v o1 and v o2 are given by:

The output phase differences ΔΦ 12 is given by:

The output signal amplitude difference Δv 12 is:

For ideal OFCCs, α1 = γ1 = 1, thus the output voltage is:

From (40) and (41), and assuming matched resistors and capacitors (i.e., R L1 = R L2 and Cz1 = Cz2). Then ∆φ 12 = 180° and ∆v 12 = 0 dB, i.e., the phase and amplitude errors disappear. v o1 and v o2 therefore become balanced amplitude-matched signals. The mismatching impacts of R L1, R L2 and Cz1 and Cz2 will be discussed and investigated in details in part 4.

4 Impact of mismatch variations on the proposed CMBG performance

In this section, the ideal assumption made in Eqs. (31) and (41) where RL1 = RL2 and Cz1 = Cz2, is investigated. It is assumed that resistances RL1 and RL2 have a mismatch ΔR. Capacitances Cz1 and Cz2 are assumed to have a mismatch ΔC. Ten thousands Monte Carlo simulation points are calculated for different values of ΔR/R and also for different values of ΔC/C. Following that, the resulting magnitude variations around the nominal value of 1.0 and the phase variations around the nominal value of 180o is determined.

4.1 Resistor mismatch

The resistance mismatch variation (i.e., ΔR/R) is assumed to be 2, 5, 10, and 20 %. Monte Carlo simulations are performed to get the corresponding mean and standard deviation of the magnitude and the phase. Figure 10 shows the relative variations of the magnitude and phase (i.e., the standard deviation divided by the nominal mean value) resulting from different resistance mismatch values (i.e., 2, 5, 10, and 20 %) when the operating frequency is 1 MHz.

From Fig. 10, it is obvious that the relative phase variations are higher than the relative magnitude variations, especially at higher resistance mismatch values. In addition, as the resistance mismatch variations increase, the relative magnitude variations increase at a lower rate than that of the relative phase variations.

Also, the relative magnitude variations and the relative phase variations are calculated for different operating frequency values (1, 5 and 10 MHz) when the resistance mismatch variations are fixed at 20 % and are shown in Fig. 11. In Fig. 11, it can be noted that the effect of the operating frequency on the relative magnitude and phase variations is not significant.

4.2 Capacitor mismatch

Similarly, the relative variations of the magnitude and phase are calculated for different values of the capacitance mismatch (i.e., 2, 5, 10, and 20 %) at 1 MHz operating frequency and plotted in Fig. 12.

As shown in Fig. 12, the relative phase variations are higher than the relative magnitude variations and also increasing at a higher rate. Moreover, the relative variations in magnitude and phase due to the capacitance mismatch are smaller than that due to the resistance mismatch by a factor of 10. This shows that the selection of the resistances should be done very carefully as the resistance mismatch has an impact on the proposed circuit performance. However, this impact is still not significant as it is less than 4 % when the resistance mismatch variations are 20 %.

Figure 13 displays the relative magnitude and phase variations for different frequency values at 20 % capacitance mismatch. It is shown that increasing the operating frequency helps in reducing the relative phase variations significantly (i.e., when the frequency changed from 1 to 10 MHz, the relative phase variations dropped by a factor of 5).

5 Experimental and simulation results of the proposed CMBG

To verify the operational characteristics of the proposed CMBG, the circuit of Fig. 9 was simulated using PSPICE version 9.1. The proposed CMBG was also prototyped, tested in the single-ended input mode and the simulation results verified. Each OFCC was constructed using an Analog Devices AD846AQ current feedback op amp [15] and current-mirrors composed of Harris transistor array CA3096CE [16]. The AD846AQ has a bandwidth of 80 MHz at unity gain, and slew rate 450 V/μs. We connected the input voltage to vin1 and connected vin2 to the ground. Resistors Rw1 and Rw2 were set at 1 KΩ, while RL1 and RL2 were set at 1.5 KΩ and RG was tested at values of 220Ω and 1 KΩ. All resistors have 1 % tolerance. For these resistors values, the low frequency gains were 6.8 (16.7 dB) and 1.5 (3.5 dB), respectively. The output-signal phase and amplitude differences were measured with respect to frequency. The amplitude error |∆V |in dB for the two values of R G is shown in Fig. 14. This error is 0 dB for RG = 220 and 1 KΩ for frequencies up to 1 MHz. The phase-difference error ∆Φ for the two values of R G is shown in Fig. 15, the system phase error remained less than about 1◦ for frequencies up to 1 MHz for R G = 1 kΩ and R G = 220 Ω. This performance up to 1 MHz is superior to the circuit performances in Ref [5–8]. Figures 14 and 15 confirm the independence of both the phase and amplitude responses with changing of RG. Also, from these figures, we can observe that the experimental results validate the simulated results and the analytical results of Eqs. (40) and (41), except at frequencies approaching the bandwidth of the OFCC. The difference between the experimental and simulation results can be interpreted as a result of tracking errors and the presence of additional stray capacitances at the various nodes in the circuit. The oscilloscope output taken at 1 MHz is shown in Fig. 16 with RG = 1 KΩ.

6 Discussion

Table 1 shows a performance comparison between the proposed current-mode balanced generator circuits and the other circuitry that used to provide the same functions [5–7]. Balanced generator circuits proposed in Ref. [5, 6] which utilized the operational amplifiers, these circuits require the amplifier-pole matching and gain restrictions. Inversely, the current-mode balanced generator, which uses two CCII+ and two Op-amps, or four CCII+ , Ref. [7, 8], respectively, have better amplitude and phase performance at low frequencies. However at high frequencies, the amplitude and phase errors increase and depend on the gain dependent resistor (RG), see Eqs. (1) and (2). Also, these topologies use 2 CCII+ in conjunction with 2 op-amps or 4 CCII+, which means more power consumption. The power consumptions and the expected fabrication area of the circuits proposed in Refs. [5–8] are as shown in Table 2 [15–18]. From Table 2, the expected fabrication die area of the proposed circuit is outperforming the circuits provided in Refs [7, 8]. For example, the expected die area of the circuit proposed in Refs [5, 6] is calculated as follows: the die area of a single LF351 Op-Amp is 2.286 × 2.286 mm2 = 5.2258 mm2 [17], there are two Op-amps used to implement the circuit proposed in Refs [5, 6], thus the total expected die area is 2 × 5.2258 mm2 = 10.4516 mm2. The expected die area of the proposed circuit is calculated as follows: The OFCC consists of 1 × AD846 current feedback amplifier and 2 × CA3069 transistor array [15, 16]. The die area of AD846 current feedback amplifier is 2.2 × 2.64 mm2 = 5.808 mm2 [15]. The die area of the CA3096 is 0.74 × 0.74 mm2 = 0.5476 mm2 [1]. Thus, the total die area of a single OFCC is 5.808 + (2 × 0.5476) = 6.9032 mm2 and the total die area of the proposed CMBG which includes 2 × OFCC is 2 × 6.9032 = 13.8064 mm2. Similarly, the expected die areas of the circuits proposed in Ref. [7, 8] are calculated and shown in Table 2. The power consumption of the proposed circuit is better than Refs [5–7]. However, Ref [8] shows better power consumption compared to the proposed circuit. On the other hand, the proposed topology uses only two OFCCs. It has a phase and amplitude errors 1 and 0 dB, respectively, up to frequency 1 MHz. This performance up to 1 MHz is superior to the circuit performances of Ref. [7, 8]. The proposed circuit’s output phase and amplitude are independent of RG, see Eqs. (39) and (41). In other words, in the proposed circuit RG controls only the gain of vo1 and vo2, as shown in Eqs. (35) and (36) and it does not control the phase or amplitude difference, as proven in Eqs. (39) and (41). Figure 17 shows the amplitude and phase performance of the proposed circuit and the circuit in Ref. [7], when RG = 1 KΩ. This figure shows that the proposed circuit provides accurate amplitude and phase-matched balanced signals for frequencies up to 1 MHz compared with circuit in Ref. [7]. The power consumption and expected fabrication area of the proposed circuit are 179.5 mW and 13.8064 mm2, respectively.

The amplitude and phase responses of the circuit in Ref. [7] and the proposed circuit when RG = 1 K Ohm

7 Conclusion

A new CMBG circuit based on an OFCC has been proposed, simulated and prototyped. The experimental results show that the new CMBG configuration has the following advantages: it produces accurate amplitude-matched balanced signals for frequencies up to 1 MHz without using matched devices. The voltage gain, as well as the bandwidth, of the proposed CMBG is independent of Rx of the current feedback op-amp used and dependent only on the external resistors (i.e., RG and RL). The mismatching impacts on the proposed CMBG are presented and discussed. The proposed CMBG is not complicated and offers advantages over and above currently used CMBG. On the other hand, it would be suitable candidate for integration in an IC process. Thus, it can be used in many applications, such as biomedical and lab-on-a-chip.

References

Rzeszewski, T. (1976). A system approach to synchronous detection. IEEE Transactions On Consumer Electronics, CE-22(2), 186–193.

Nakanishi, M., & Sakamoto, Y. (1996). Analysis of first-order feedback loop with lock-in amplifier. IEEE Transaction on Circuit and System II, 43(8), 570–576.

Duque-Carrillo, J. F. (1993). Control of the common-mode component in CMOS continuous-time fully differential signal processing. Analog Integrated Circuit and Signal Processing, 4, 131–140.

Ghallab, Y. H., & Badawy, W. (2010). Lab-on-a-chip: Techniques, circuits and biomedical applications. Boston: Artech House Publisher.

Golnabi, H., & Ashrafi, A. (1996). Producing 180° out-of-phase signals from a sinusoidal waveform input. IEEE Transactions on Instrumentation and Measurement, 45(1), 312–314.

Baert, D. H. J. (1999). Circuit for the generation of balanced output signals. IEEE Transactions on Instrumentation and Measurement, 48(6), 1108–1110.

Gift, S. J. G., & Maundy, B. J. (2006). Balanced-output-signal generator. IEEE Transactions on Instrumentation and Measurement, 55(3), 835–838.

Abuelma’atti, M. T.(2013) Balanced output signal generator, US Patent 8,368,464 B2.

Ghallab, Y. H., Badawy, W., Kaler, K. V. I. S., & Maundy, B. J. (2005). A novel current-mode instrumentation amplifier based on operational floating current conveyor. IEEE Transaction on Instrumentation and Measurement, 54(5), 1941–1994.

Ghallab, Y. H., & Badawy, W. (2006). A new topology for a current-mode wheatstone bridge. IEEE Transaction on Circuit and System II, 53(1), 18–22.

Ghallab, Y. H., Badawy, W., Abou El-Ela, M., & El-Said, M. H. (2006). The operational floating current conveyor and its applications. Journal of Circuits, Systems and Computers, 15(3), 352–371.

Ghallab, Y. H. & Badawy, W. (2006). A New Design of the Current-mode Wheatstone Bridge Using Operational Floating Current Conveyor, International Conference on MEMS, NANO, and Smart Systems 2006 (ICMENS 2006), Dec. 27–29th (pp. 41–44) Cairo, Egypt.

Ghallab,Y. H., Badawy, W. & Kaler, K. V.I.S. (2003). A novel differential ISFET current mode read–out circuit using operational floating current conveyor, ICMENS 2003( pp. 255–258). Banff, Alberta, Canada.

Soclof, S. (1991). Design and applications of analog integrated circuits, Chap.9 (pp. 443–460). New York: Prentice Hall Inc.

Analog Devices Manual “450 V/μs, precision, current-feedback OpAmp (AD846)” (pp. 2-307–2-317).

Harris semiconductor “CA3096, CA3096A, CA3096C, NPN transistor arrays” File Number 595.4, December 1997.

National Semiconductor LF351 Wide Bandwidth JFET Input Operational Amplifier Data Sheet.

Analog Devices Manual “ 60 MHz 2000 V/μs, monolithic Op Amp (AD844)”.

Acknowledgments

This research was partially funded by Zewail City of Science and Technology, AUC, the STDF, Intel, Mentor Graphics, and MCIT.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ghallab, Y.H., Mostafa, H. & Ismail, Y. A new current mode implementation of a balanced-output-signal generator. Analog Integr Circ Sig Process 81, 751–762 (2014). https://doi.org/10.1007/s10470-014-0419-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-014-0419-5