Abstract

This chapter introduces the design of a memristor emulator which can be used for fully integrated circuit applications. The design employs a single voltage differencing transconductance amplifier (VDTA) as the active building block for simulating emulator behavior. Further, the design also contains one active analog multiplier, one passive grounded resistor, and capacitor, respectively. The proposed emulator circuit is simulated on the 45 nm CMOS technology node making it both cost and power-efficient emulator circuit. All the analytical derivations mentioned in this research work have been verified by simulation results obtained using Virtuoso custom design platform of Cadence. The non-volatile nature of the proposed circuit has also been validated.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

- Voltage differencing transconductance amplifier

- Memristor emulator

- Voltage mode

- Memductance

- Hysteresis loop

1 Introduction

Memristor, which is the abbreviation of two words “Memory” and “Resistor,” is a nonlinear two terminal element. Memristor theory is initially introduced by Leon Chua in 1971 [1]. Later in 2008, memristor fabrication was successfully carried out by Stanley Williams from the Hewlett-Packard Company using titanium oxide (TiO2) [2]. Before the introduction of memristors, there were three basic passive elements, i.e., resistor, capacitor, and inductor. As such, a linear resistor forms a relation between “voltage” and “current” and the two other fundamental elements capacitor and inductor form the relation between “voltage” and “charge” and “current” and “flux,” respectively. Similarly, the two terminal passive element, memristor, forms the missing relation between “flux” and “charge.” Memristor possesses memristance, which exhibits pinched hysteresis behavior. Memristance depends on the direction of current flow; i.e., when current is allowed to pass in one direction, the memristance increases whereas it decreases once the direction of current is changed. The memristor is a versatile element due to its non-volatile behavior and therefore is used in high-density memory circuits [3] and neuromorphic systems [4]. A memristor can also be employed in various analog and digital applications such as programmable sinusoidal oscillators [5], adaptive filters [6], chaotic circuits [7], logic gates [8], and digital multipliers [9].

Since the commercial viability of physical memristor is complex and expensive, researchers have focused their attention toward emulating the behavior of TiO2 memristor as the reference model. Several research papers have been published on memristor emulator circuits which can be physically implemented [10,11,12,13]. Nevertheless, such emulators lack certain features such as use of more number of passive elements, electronic tunability, pinch hysteresis loop at reasonably lower frequencies, lower power dissipation, etc. This paper proposes a fully integrated memristor emulator circuit which employs the active element as voltage differencing transconductance amplifier (VDTA). The proposed circuit reports desirable memristor features such as tunability, lesser number of passive elements, and lower power consumption.

2 VDTA

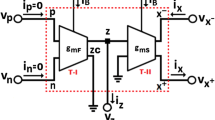

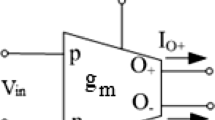

The active block used for realizing the memristor emulator circuit is voltage differencing transconductance amplifier (VDTA) [14, 15]. Figures 1 and 2 show block diagram of VDTA and its CMOS technology realized schematic. Basically, the VDTA consists of two operational transconductance amplifiers (OTAs) cascaded together as seen in Fig. 2.

The following matrix equation shows the current and voltage relations of VDTA’s input–output terminals:

Here, vp, vn, vz, vx+, vx− and ix+, ix−, iz are potential drops and currents at their respective VDTA ports. Current in p and n ports equals to zero due to very high impedance across them. gmf and gms are effective transconductances of first and second OTAs, respectively, and are given as

where gm1, gm2,…, gm8 are individual transistor transconductances and can be calculated by using following relation

where

Here, \(\mu_{k}\) is mobility of kth transistor, Cox is the ratio of oxide permittivity to its thickness, W and L are transistor dimensions, and IDS is drain-to-source current.

3 Memristor Emulator Circuit

The presented memristor emulator circuit introduces the change in resistance by changing the value of applied voltage, vin. The emulator circuit employs one VDTA as active element, two grounded passive elements, i.e., one resistor and one capacitor, an inverting/non-inverting buffer together with an analog multiplier. The configuration is shown in Fig. 3. The presented memristor emulator contains only active elements and grounded passive elements. Nonetheless, the earlier published emulator circuit comprises discrete multiplier circuits, which presents higher complexity, higher power, higher cost, etc. In this paper, the presented design consists of CMOS Gilbert cell-based analog voltage multiplier circuit which is fully integrated and consumes less power [16, 17].

Analyzing the circuit proposed Fig. 3 and using the current and voltage equations from [1], we obtain:

Using (6) and (7), the current at the x+ terminal is found to be:

The potential across capacitor C, i.e., vC, is given by the integral of \(i_{{x^{ + } }}\). From (8), vC is given as,

The feedback voltage vfb is obtained through CMOS Gilbert cell-based analog voltage multiplier circuit and is given by the multiplication of vC and vin, i.e.,

Therefore, the memductance GM is given by,

From (12), the mathematical model of the presented memristor emulator shows incremental (+)/decremental (−) mode of operations.

4 Simulation Results

The presented emulator circuit has been implemented at CMOS 45-nm technology node using Virtuoso ADE of Cadence. VDD = − VSS; i.e., the power supply is considered as ±0.95 V. The passive component values are selected as RS = 1 KΩ, C = 10 nF. For a sinusoidal input signal (iin) with amplitude of 50 μA, the behavior of characteristic frequency-dependent pinched hysteresis loop of the presented memristor emulator with variations in frequencies, i.e., at f = 500 Hz, f = 1 kHz, f = 5 kHz, and f = 10 kHz is shown in Fig. 4(a)–(d), respectively. The power dissipation of the emulator is calculated to be 3.956 mW.

The controllability of bias current (IBIAS) on the transconductance (gm) is used for tuning the memductance presented by the presented memristor emulator. In accordance with (12), the memductance gradually increases/decreases with the increase in bias current. This tunable nature of the proposed memristor emulator circuit is advantageous for integrated circuit applications. Further, the change in memconductance when a train of pulse is applied across the presented memristor emulator circuits showing its incremental and decremental operations is shown in Fig. 5a–b, respectively.

5 Conclusion

A VDTA-based fully integrated grounded memristor emulator circuit is presented and designed using one VDTA, one four quadrant analog multiplier, two grounded passive elements, i.e., one capacitor, one resistor, and one inverting/non-inverting buffer. The presented emulator has simple circuit topology, fully integrated configuration, and low power consumption. The simulations presented here support the theoretical derivations, thereby making it a robust and versatile emulator. Further, the tunability via varying the bias current overcomes the process mismatches that occur during fabrication.

References

Chua LO (1971) Memristor-the missing circuit element. IEEE Trans Circ Theory 18(5):507–519

Strukov D, Snider GS, Stewart DR, Williams RS (2008) The missing memristor found. Nat Lett 453:80–83

Ho Y, Huang GM, Li P (2011) Dynamical properties and design analysis for nonvolatile memristor memories. IEEE Trans Circ Syst I Reg Pap 58(4):724–736

Indiveri G, Chicca E, Douglas R (2006) A VLSI array of low-power spiking neurons and bistable synapses with spike-timing dependent plasticity. IEEE Trans Neural Netw 17(1):211–221

Talukdar A, Radwan AG, Salama KN (2011) Generalized model for memristor-based Wien family oscillators. Microelectron J 42(9):1032–1038

Driscoll T, Quinn J, Klein S, Kim HT, Kim BJ, Pershin YV, Di Ventra M, Basov DN (2010) Memristive adaptive filters. Appl Phys Lett 97(9):093502

Buscarino A, Fortuna L, Frasca M, Gambuzza LV (2012) A chaotic circuit based on Hewlett-Packard memristor. Chaos 22:023136

Borghetti J, Snider GS, Kuekes PJ, Yang JJ, Stewart DR, Williams RS (2010) Memristive switches enable stateful logic operations via material implication. Nature 464(7290):873–876

Serrano-Gotarredona T, Masquelier T, Linares-Barranco B, Adamatzky A, Chua L (2014) Spike-timing-dependent-plasticity with memristors. Memristor networks. Springer, Cham, pp 211–247

Alharbi AG, Fouda ME, Khalifa ZJ, Chowdhury MH (2017) Electrical nonlinearity emulation technique for current-controlled memristive devices. IEEE Access 5:5399–5409

Sánchez-López C, Aguila-Cuapio LE (2017) A 860 kHz grounded memristor emulator circuit. AEU-Int J Electron Commun 73:23–33

Sánchez-López C, Mendoza-López J, Carrasco-Aguilar MA, Muñiz-Montero C (2014) A floating analog memristor emulator circuit. IEEE Trans Circ Syst II Exp Briefs 61(5):309–313

Babacan Y, Kaçar F (2017) Floating memristor emulator with subthreshold region. Analog Integr Circ Sig Process 90(2):471–475

Aishwarya N, Nayak A, Pal I, Kumar V, Islam A (2019) A novel CNFET based tunable memristor emulator. Microsyst Technol Micro Nanosyst Inf Stor Process Syst, 1–9

Pal I, Kumar V, Aishwarya N, Nayak A, Islam A (2019) A VDTA-based robust electronically tunable memristor emulator circuit. Analog Integr Circ Sig Process, 1–13

Kumar V, Mehra R, Islam A (2017) A 2.5 GHz low power, high-Q, reliable design of active bandpass filter. IEEE Trans Dev Mater Reliab 17(1):229–244

Mehra R, Kumar V, Islam A (2018) Reliable and Q-enhanced floating active inductors and their application in RF bandpass filters. IEEE Access 6:48181–48194

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2020 The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Kumar, V., Pal, I., Islam, A. (2020). A Fully Integrated Tunable Memristor Emulator Circuit. In: Sikander, A., Acharjee, D., Chanda, C., Mondal, P., Verma, P. (eds) Energy Systems, Drives and Automations. Lecture Notes in Electrical Engineering, vol 664. Springer, Singapore. https://doi.org/10.1007/978-981-15-5089-8_54

Download citation

DOI: https://doi.org/10.1007/978-981-15-5089-8_54

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-5088-1

Online ISBN: 978-981-15-5089-8

eBook Packages: EnergyEnergy (R0)