Abstract

This paper presents a low-noise amplifier for wideband applications which requires a great challenge in achieving appropriate value for the gain, noise figure, power consumption, stability, and complexity. The proposed circuit is designed for the frequency range of 50 MHz–4 GHz with noise figure less than 2.6 dB, an input return loss (S11) < −10 dB, gain of 22.2 dB, IIP3 of −14.2 dBm with power consumption of 10.02 mW at 1.8 V power supply. The proposed design is simulated on ELDORF tool using 0.18-µm CMOS technology.

Access provided by CONRICYT-eBooks. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

Wideband technology has attracted many researchers because a wide range of future and modern communication system has been proposed that operates over a bandwidth of several gigahertz such as cognitive radio, software defined radio, etc. Wideband systems are capable of transmitting data over a wide spectrum of frequency bands with very low power and high data rates up to gigabits per second. The broadband behavior of wideband transceivers is mainly determined by the low-noise amplifiers. Low-noise amplifier has significant impact on the overall performance of the receivers as they are the first block of the receiver. Therefore, to achieve good performance parameters like ultrawide bandwidth with reasonable noise figure (NF) and good input (close to 50 Ω) and output impedance matching across the bandwidth of interest, it poses a more stringent requirement on the LNA.

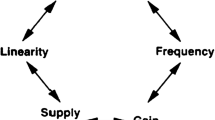

Trade-off between voltage headroom, noise figure, bandwidth, and linearity has been done for optimal low-noise amplifier design. Several topologies for wideband low-noise amplifiers exit in literature such as common gate amplifiers, negative feedback amplifiers, distributed amplifiers [1,2,3,4,5,6,7], and inductive source degeneration amplifiers. The topology used for a particular application begins with requirements of input matching. Most of the existing wideband LNAs are operated at high frequencies only. The proposed design operates at both high frequency and low frequency so it can be used for wideband applications and also for cognitive radio that operates in the frequency range of 50 MHz–10 GHz.

In this paper, a low-noise amplifier is designed based on cascode structure. The paper is organized in the following manner: In Sect. 2, wideband input matching techniques are described. Section 3 provides concept of proposed circuit. Section 4 discusses the simulation results. In the end, Sect. 5 presents the conclusion.

2 LNA Topologies

There are several topologies to design a wideband LNA and the choice of topology begins with the input matching requirements, and thus the first task of LNA design is to create 50 Ω resistive input impedance. The noise figure of LNA (about 2–3 dB of overall noise figure of a typical receiver) directly adds to the receiver, and thus the LNA should be designed in a way that it adds minimum noise in the input signal path. The input matching topologies used for LNAs have several forms such as inductively degenerated common source (CS) stage, gain stage with resistive feedback, common gate (CG) stage, and combination of CS and CG stages [8, 9]. Figures 1 and 2 shown below are inductively degenerated common source stage and common gate stage, respectively. The CS LNA has superior noise performance because inductive degeneration is ideally noiseless and the RF input signal is pre-amplified by the input matching series resonant network, whereas the CG LNA uses a parallel resonant network to match the input impedance at resonance (\(\frac{1}{{g_{m} }}\)) to 50 Ω [9]. Also, CG LNA provides a wideband input match that is less sensitive to the input parasitic capacitances.

The inductive source degeneration topology provides perfect matching without adding noise and without imposing any restriction on the transconductance [10]. To obtain the perfect matching, two inductors Ls and Lg are used as shown in Fig. 1. The circuit proposed in the paper is designed using inductive degeneration. Figure 3 shows the small signal equivalent circuit of the inductively degenerated CS stage.

Since for a low-noise amplifier the input impedance is an important parameter and is set to be 50 Ω, we will find the expression for input impedance. The input impedance of the circuit shown in Fig. 3 is capacitive and is given by

where

Putting s = jω and on solving (3) we get

For MOSFET, value of Rg is chosen as zero. Hence, the input impedance has only two components. For a low-noise amplifier, the input impedance should be resistive; hence, another inductance Lg is added to the gate terminal so that the capacitive effect is canceled out at resonant frequency, i.e.,

3 Proposed Circuit

The proposed circuit using cascode inductive source degeneration topology is shown in Fig. 4.

In this, M1 and Ls form a CS inductive degeneration amplifier which is the input stage of cascode circuit driven by the input signal source Vin. This input stage drives the M2 transistor act as common gate amplifier with output signal Vout. M2 reduces the Miller feedback capacitance Cgd of M1 by providing low input impedance to M2, thereby reducing voltage gain of M1. Thus, by introducing M2, isolation and low-frequency gain improve. However, the gain, linearity, and noise figure at high frequency degrade due to the parasitic capacitances of M2. To overcome these degradations, inductor LD is used in between M1 and M2. L D partially cancels the parasitic capacitance at the source of cascode transistor M2. The noise contributed by LD remains less than that of M1 even at relatively high frequencies. M3 and L2 are used to bias the transistor M1. RD is the load impedance of M2.

4 Simulation Results

The proposed circuit is designed using 180 nm CMOS technology and simulations were carried out using EldoRF tool. The proposed circuit consumes 10.2 mW power from 1.8 V supply.

Figure 5a shows that the input return loss S11 is less than −10 dB over all the bandwidth. Figure 5b shows the gain versus the power curve where power ranges from −20 to 10 dB. The noise figure of the circuit is shown in Fig. 5c which lies between 2.45 and 2.62 dB. The noise figure of the proposed circuit is close to the desired noise figure of 2.5 dB. Figure 5d illustrates the third-order intercept point which is less than −14 dBm. The performance of the proposed LNA and comparison with the existing circuits are summarized in Table 1.

5 Conclusions

Table 1 above helps to draw a conclusion that the present work offers better gain (22.2 dB) as compared to existing works, and also the power consumption (10.02 mW) and noise figure (2.64 dB) are competitive to the existing works. Further, these improvements occur for a wider frequency band (0.05–4 GHz).

References

Hidayov OA, Nam NH, Yoon G, Han SK, Lee SG (2013) 0.7–2.7 GHz wideband CMOS low-noise amplifier for LTE application. Electron Lett 49(23):1433–1435

Guo B, Chen J, Li L, Jin H, Yang G (2017) A wideband noise-canceling CMOS LNA with enhanced linearity by using complementary nMOS and pMOS configurations. IEEE J Solid State Circuits. IEEE

Liao W-R, Yang J-R (2016) A 0.5–3.5 GHz wideband CMOS LNA for LTE application. IEEE

Ma L, Wang Z-G, Xu J, Amin NM (2016) A high linearity wideband common-gate LNA with differential active inductor. IEEE

Ito T, Okada K, Matsuzawa A (2011) A 0.8–1.8 GHz wideband low noise amplifier with capacitive feedback. In: Proceedings of the Asia-Pacific microwave conference

Wang S-F, Hwang Y-S, Yan S-C, Chen J-J (2011) A new CMOS wideband low noise amplifier with gain control. Integr VLSI J 44:136–143

Moezzi M, Bakhtiar MS (2012) Wideband LNA using active inductor with multiple feed-forward noise reduction paths. IEEE Trans Microw Theory Tech 60(4)

Razavi B (2002) Design of analog CMOS integrated circuits. Tata McGraw-Hill. ISBN: 978-0-07-052903-9

Razavi B (2012) RF microelectronics. Prentice Hall. ISBN: 978-0-13-713473-1

Li RC-H (2009) RF circuit design. Wiley. ISBN: 978-0-470-16758-8

Acknowledgements

This work is supported by the project entitled “Study and Design of Low Power Circuits for Cognitive Radio” under the Faculty Research Scheme, DIT University, Dehradun, India (Ref. No.: DITU/R&D/2015/ECE). The author would like to thank Prof. K. K. Raina, Vice-Chancellor, DIT University for encouragement and support during the present research work. The author would also like to thank the anonymous reviewers for their valuable comments and suggestions.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2018 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Pandey, V.K., Verma, D.K., Sharma, S., Singh, S. (2018). A 50 MHz–4 GHz Low-Noise Amplifier for Wideband Applications. In: Bhattacharyya, S., Gandhi, T., Sharma, K., Dutta, P. (eds) Advanced Computational and Communication Paradigms. Lecture Notes in Electrical Engineering, vol 475. Springer, Singapore. https://doi.org/10.1007/978-981-10-8240-5_15

Download citation

DOI: https://doi.org/10.1007/978-981-10-8240-5_15

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-8239-9

Online ISBN: 978-981-10-8240-5

eBook Packages: EngineeringEngineering (R0)