Abstract

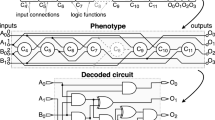

In recent years the evolution of digital circuits has been intensively studied. This paper proposes an elitist pool evolutionary algorithm based on novel approach in order to improve evolutionary design of logic circuits in efficiency and capability of optimization. In the process of evolution, a novel sub-circuit crossover strategy can improve the local optimization by inheriting the better parts of two parental circuits, and an adaptive mutation strategy based on importance of gene-position can maintain the diversity of a population. Experiments show that the proposed method is able to design logic circuits efficiently.

Access provided by Autonomous University of Puebla. Download to read the full chapter text

Chapter PDF

Similar content being viewed by others

References

Linden, D.S.: Optimizing signal strength in-situ using an evolvable antenna system. In: 2002 NASA/DoD Conference on Evolvable Hardware, pp. 147–151 (2002)

Vinger, K.A., Torresen, J.: Implementing evolution of FIR-filters efficiently in an FPGA. In: 2003 NASA/DoD Conference on Evolvable Hardware, pp. 26–29 (2003)

Glette, K., Torresen, J., Gruber, T., Sick, B., Kaufmann, P., Platzner, M.: Comparing Evolvable Hardware to Conventional Classifiers for Electromyographic Prosthetic Hand Control. In: NASA/ESA conference on adaptive hardware and systems, Noordwijk, the Netherlands, June 2008, pp. 32–39 (2008)

Koza, J.R., Bennett, F.H., Andre, D., Keane, M.A., Dunlap, F.: Automated Synthesis of Analog Electrical Circuits by Means of Genetic Programming. IEEE Transactions on Evolutionary Computation 1(2), 109–128 (1997)

Stomeo, E., Kalganova, T., Lambert, C.: Generalized Disjunction Decomposition for Evolvable Hardware. IEEE Transactions on, Systems, Man and Cybernetics (Part B) 36(5), 1024–1043 (2006)

Ishida, Y., Nosato, H., Takahashi, E., Murakawa, M., Kajitani, I., Furuya, T., Higuchi, T.: Proposal for LDPC Code Design System Using Multi-Objective Optimization and FPGA-Based Emulation. In: The 8th internalional Conference on Evolvable Systems: From Biology to Hardware, Prague, Czech Republic, September 2008, pp. 237–248 (2008)

Coello, C.A.C., Aguirre, A.H.: Design of combinational logic circuits through an evolutionary multiobjective optimization approach. Ai Edam-Artificial Intelligence for Engineering Design Analysis and Manufacturing, 16(1), 39–53 (2002)

Kalganova, T., Miller, J.F.: Circuit layout evolution: An evolvable hardware approach. In: IEE Colloquium (Digest), pp. 11–14 (1999)

Miller, J.F., Job, D., Vassilev, V.K.: Principles in the evolutionary design of digital circuits—part II. In: Genetic Programming and Evolvable Machines, vol. 1, pp. 259–288 (2000)

Bidlo, M., Vasicek, Z.: Gate-Level Evolutionary Development Using Cellular Automata. In: NASA/ESA conference on adaptive hardware and systems, Noordwijk, the Netherlands, pp 11–18 (June 2008)

Coello Coello, C.A., Christiansen, A.D., Aguirre, A.H.: Use of Evolutionary Techniques to Automate the Design of Combinational Circuits. International Journal of Smart Engineering System Design 2, 299–314 (2000)

Coello Coello, C.A., Aguirre, A.H.: Design of combinational logic circuits through an evolutionary multiobjective optimization approach. Artificial Intelligence for Engineering, Design, Analysis and Manufacture 16(1), 39–53 (2002)

Karnaugh, M.: A Map Method for Synthesis of Combinational Logic Circuits. Transaction of the AIEE, Communications and Electronic 72(I), 593–599 (1953)

Quine, W.V.: A Way to Simplify Truth Function. American Mathematical Monthly 62(9), 627–631 (1955)

McCluskey, E.J.: Minimization of Boolean Function. Bell Systems Technical Journal 35(5), 1417–1444 (1956)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2009 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

He, Gl., Li, Yx., Shi, Z. (2009). A Novel Crossover Operator in Evolutionary Algorithm for Logic Circuit Design. In: Cai, Z., Li, Z., Kang, Z., Liu, Y. (eds) Computational Intelligence and Intelligent Systems. ISICA 2009. Communications in Computer and Information Science, vol 51. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-04962-0_13

Download citation

DOI: https://doi.org/10.1007/978-3-642-04962-0_13

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-04961-3

Online ISBN: 978-3-642-04962-0

eBook Packages: Computer ScienceComputer Science (R0)