Abstract

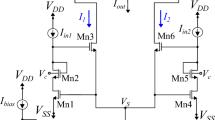

The self-similitude architecture developed in our previous work for multiple-resolution image perception [1] has been transformed into a non-subtraction configuration. In contrast to the previous work, the subtraction operations are entirely eliminated from the computation repertory of processing elements. As a result, the hardware organization of multiple-resolution edge-filtering image sensor has been greatly simplified. In addition, a fully pixel-parallel self-similitude processing has been established without any complexity in the interconnects. A proof-of-concept chip capable of performing four directional edge filtering at full, half and quarter resolutions was designed in a 0.18μm 5-metal CMOS technology and was sent to fabrication. The performance was verified by circuit simulation (Synosyps NanoSim), showing that the four directional edge filtering at multiple resolutions is carried out at more than 1000 frames/sec. with a clock rate of 500kHz.

Access provided by Autonomous University of Puebla. Download to read the full chapter text

Chapter PDF

Similar content being viewed by others

References

Takahashi, N., Fujita, K., Shibata, T.: An Analog Self-Similitude Edge-Filtering Processor for Multiple-Resolution Image Perception. In: 2008 IEEE International Symposium on Circuits and Systems, pp. 1640–1643 (2008)

Hubel, D.H., Wiesel, T.N.: Receptive fields of single neurons in the cat’s striate cortex. J. Physiology 148, 574–591 (1959)

Lowe, D.G.: Distinctive Image Features from Scale-Invariant Keypoints. J. Computer Vision 60(2), 91–110 (2004)

Yagi, M., Shibata, T.: An Image Representation Algorithm Compatible with Neural-Associative-Processor-Based Hardware Recognition Systems. Trans. Neural Networks 14(5), 1144–1161 (2003)

Suzuki, Y., Shibata, T.: An Edge-Based Face Detection Algorithm Robust Against Illumination, Focus, and Scale Variations. In: 13th European Signal Processing Conference, pp. 2279–2282 (2004)

Kemeny, S.E., Panicacci, R., Pain, B., Matthies, L., Fossum, E.R.: Multiresolution image sensor. Trans. Circuits and Systems for Video Technology 7(4) (1997)

Cembrano, G.L., et al.: A 1000 FPS at 128 x 128 vision processor with 8-bit digitized I/O. J. Solid-State Circuits 39(7) (2004)

Dudek, P., Hicks, P.J.: A general-purpose processor-per-pixel analog SIMD vision chip. Trans. Circuits and Systems 52(1) (2005)

Olyaei, A., Genov, R.: Focal-Plane Spatially Oversampling CMOS Image Compression Sensor. Trans. Circuits and Systems I 54(1), 26–34 (2007)

McIlrath, L.D.: A CCD/CMOS focal-plane array edge detection processor implementing the multiscale veto algorithm. J. Solid-State Circuits 31(9), 1239–1247 (1996)

Choi, J., Han, S.W., Kim, S.J., Chang, S.I., Yoon, E.: A Spatial-Temporal Multiresolution CMOS Image Sensor With Adaptive Frame Rates for Tracking the Moving Objects in Region-of-Interest and Suppressing Motion Blur. J. Solid-State Circuits 42(12), 2978–2989 (2007)

Gruev, V., Etienne-Cummings, R.: Implementation of Steerable Spatiotemporal Image Filters on the Focal Plane. Trans. Circuits and Systems II 49(4), 233–244 (2002)

Nakashita, Y., Mita, Y., Shibata, T.: An analog visual pre-processing processor employing cyclic line access in only-nearest-neighbor-interconnects architecture. In: 2005 NIPS Conference (2005)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2009 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Takahashi, N., Shibata, T. (2009). A Non-subtraction Configuration of Self-similitude Architecture for Multiple-Resolution Edge-Filtering CMOS Image Sensor. In: Alippi, C., Polycarpou, M., Panayiotou, C., Ellinas, G. (eds) Artificial Neural Networks – ICANN 2009. ICANN 2009. Lecture Notes in Computer Science, vol 5768. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-642-04274-4_41

Download citation

DOI: https://doi.org/10.1007/978-3-642-04274-4_41

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-642-04273-7

Online ISBN: 978-3-642-04274-4

eBook Packages: Computer ScienceComputer Science (R0)