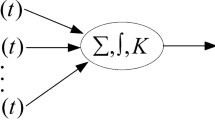

A compact analog programmable multidimensional radial- basis-function (RBF)-based classifier is demonstrated in this chapter. The probability distribution of each feature in the templates is modeled by a Gaussian function that is approximately realized by the bell-shaped transfer characteristics of a proposed floating-gate bump circuit. The maximum likelihood, the mean, and the variance of the distribution are stored in floating-gate transistors and are independently programmable. By cascading these floating-gate bump circuits, the overall transfer char- acteristics approximate a multivariate Gaussian function with a diagonal covariance matrix. An array of these circuits constitute a compact multi- dimensional RBF-based classifier that can easily implement a Gaussian mixture model. When followed by a winner-take-all circuit, the RBF- based classifier forms an analog vector quantizer. Receiver operating characteristic curves and equal error rate are used to evaluate the per- formance of the RBF-based classifier as well as a resultant analog vector quantizer. It is shown that the classifier performance is comparable to that of digital counterparts. The proposed approach can be at least two orders of magnitude more power efficient than the digital microprocessors at the same task.

Chapter PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

References

P. Hasler, P. D. Smith, D. Graham, R. Ellis, and D. V. Anderson, “Analog Floating-Gate, On-Chip Auditory Sensing System Interfaces,” in IEEE J. Sensors, vol. 5, no. 5, pp.1027–1034, Oct. 2005.

M. Ogawa, K. Ito, and T. Shibata, “A general-purpose vector-quantization processor employing two-dimensional bit-propagating winner-take-all,” in Symposium on VLSI Circuits, pp.244–247, 13–15 June 2002.

M. Bracco, S. Ridella, and R. Zunino, “Digital Implementation of Hierarchical Vector Quantization,” in IEEE Trans. Neural Networks, vol. 14, no. 5, pp.1072–1084, Sep. 2003.

G. Cauwenberghs and V. Pedron, “A low-power CMOS analog vector quantizer,” in IEEE J. Solid-State Circuits, vol. 32, no. 8, pp. 1278–1283, Aug. 1997.

P. Hasler, P. Smith, C. Duffy, C. Gordon, J. Dugger, D. Anderson, “A floating-gate vector-quantizer,” in Midwest Symposium on Circuits and Systems, Vol.1,4–7, Aug. 2002, pp. I-196–9.

T. Yamasaki and T. Shibata, “Analog soft-pattern-matching classifier using floating-gate MOS technology,” in IEEE Trans. Neural Networks, vol. 14, no. 5, pp. 1257–1265, Sep. 2003.

7. T. Delbruck, “Bump circuits for computing similarity and dissimilarity of analog voltage,” in Proc. Int. Neural Network Society, Seattle, WA, 1991.

S. S. Watkins and P. M. Chau, “A radial basis function neurocomputer implemented with analog VLSI circuits,” in Int. Joint Conf. Neural Networks, 1992, vol. 2, pp. 607V612.

J. Choi, B. J. Sheu, and J. C.-F. Chang, “A Gaussian synapse circuit for analog neural networks,” in IEEE Trans. VLSI Syst., vol. 2, pp. 129V133, Mar. 1994.

S.-Y. Lin, R.-J. Huang, and T.-D. Chiueh, “A Tunable Gaussian/Square Function Computation Circuit for Analog Neural Networks” in IEEE Transactions on Circuits and System II, vol. 45, no. 3, 1998, pp. 441–446.

11. D. S. Masmoudi, A. T. Dieng, and M. Masmoudi, “A subthreshold mode programmable implementation of the Gaussian function for RBF neural networks applications”, in Intelligent Control, 2002. Proceedings of the 2002 IEEE International Symposium on, Vancouver, Cananda, Oct. 2002, pp. 454–459.

D. Hsu, M. Figueroa, and C. Diorio, “A silicon primitive for competitive learning,” in Conference on Neural Information Processing Systems, Dec. 2000.

P. Hasler, “Continuous-Time Feedback in Floating-Gate MOS Circuits,” in IEEE Trans. Circuit and system II, Vol. 48, No. 1, pp. 56–64, Jan. 2001.

M. Kucic, A. Low, P. Hasler, and J. Neff, “A programmable continuous-time floating-gate Fourier processor,” in IEEE Trans. Circuit and system II, pp. 90–99, Jan. 2001.

A. Bandyopadhyay, G.J. Serrano, and P. Hasler, “Adaptive Algorithm Using Hot-Electron Injection for Programming Analog Computational Memory Elements Within 0.2% of Accuracy Over 3.5 Decades,” in IEEE J. Solid-State Circuits, vol. 41, no. 9, pp.2107–2114, Sept. 2006.

P. Hasler and J. Dugger, “Correlation Learning Rule in Floating-Gate pFET Synapses,” in IEEE Trans. Circuit and system II, vol. 48, no. 1, pp.65–73, Jan. 2001.

V. Srinivasan, G. J. Serrano, J. Gray, and P. Hasler, “A precision cmos amplifier using floating-gates for offset cancellation,” in Proc. CICC05, Sept. 2005, pp. 734737.

J. Glossner, K. Chirca, M. Schulte, H. Wang, N. Nasimzada, D. Har, S. Wang, A. J. Hoane, G. Nacer, M. Moudgill, M. S. Vassiliadis, “Sandblaster low power DSP,” in IEEE Prec. Custom Integrated Circuits Conference, pp.575–581, oct. 2004.

R. Chawla, A. Bandyopadhyay, V. Srinivasan, and P. Hasler, “A 531nW/MHz, 128×32 current-mode programmable analog vector-matrix multiplier with over two decades of linearity,” in IEEE Prec. Custom Integrated Circuits Conference, pp.651–654, oct. 2004.

R. Karakiewicz, R. Genov, A. Abbas, and G. Cauwenberghs, “175 GMACS/mW Charge-Mode Adiabatic Mixed-Signal Array Processor,” in Symposium on VLSI Circuits, June, 2006.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Copyright information

© 2009 Springer-Verlag US

About this chapter

Cite this chapter

Peng, SY., Hasler, P.E., Anderson, D.V. (2009). A Programmable Multi-Dimensional Analog Radial-Basis- Function-Based Classifier. In: VLSI-SoC: Advanced Topics on Systems on a Chip. IFIP International Federation for Information Processing, vol 291. Springer, Boston, MA. https://doi.org/10.1007/978-0-387-89558-1_3

Download citation

DOI: https://doi.org/10.1007/978-0-387-89558-1_3

Published:

Publisher Name: Springer, Boston, MA

Print ISBN: 978-0-387-89557-4

Online ISBN: 978-0-387-89558-1

eBook Packages: Computer ScienceComputer Science (R0)