Abstract

Organic thin-film transistor (OTFT) has grown significantly and is now an advanced technology. One of the biggest and most favourable electronic device technologies for printable and flexible electronics is the organic thin film transistor. However, designing large-scale integration circuits remains difficult due to device uniformity. Although semiconductor layer technology has advanced, the quality of the dielectric layers is similarly essential. Leakage current and transistor size are the main factors which impact the electronic device. However, leakage current occurs due to the reduction of dielectric material that affects the parameters like threshold voltage, capacitance and transconductance. To overcome the aforementioned drawbacks, the bi-polymer layers based on squid optimization with the dielectric medium is proposed. Bi-polymers such as PEI-EP (polyetherimide–epoxy polymer), POM-H (polyoxymethylene homopolymer) and SiO\({}_{2}\) is utilized as trilayer dielectric material in this proposed method to reduce the leakage current and act as insulator. Squid game optimization is applied to optimally select the dielectric thickness to perform better performance in the device. Electrical measurements such as \(I{-}V\), transfer characteristics, mobility (\(\mu\)) and capacitance (pF) are used to evaluate the performance of the device. The obtained electrical characteristics are mobility as 355 cm\({}^{2}\) V\({}^{-1}\) s\({}^{-1}\) and capacitance value as 7.00 pF are compared with the existing dielectric materials. The experiment shows that the simulation and modelling of the proposed method performs better than the other existing dielectric medium.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

INTRODUCTION

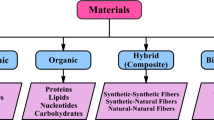

In recent years, organic thin film transistors (OTFTs) have become an essential component of a variety of flexible electronic applications, including electronic paper, smart cards, radio frequency identification (RFID) tags, sensors, large-area sensor arrays, liquid crystal flat panel displays, labels and electronic postage [1]. They are also used in electronic circuits for flexible structures of organic light-emitting diodes (OLEDs). The field of modern electronics, known as organic electronics, focuses on electronic devices made of electroactive organic materials, such as carbonaceous nanoparticles, tiny molecules and conjugated polymers [2]. The closest to biological macromolecules are, in fact, carbon-based compounds. Since a long time ago, typical organic materials are employed in a variety of electronic applications as protection or insulation [3]. Organic thin film transistors (OTFTs) are semiconductor-based transistors made from organic semiconductors (which are conjugated polymers or tiny molecules). The semiconductor layer functions as a layer of activity that regulates the movement of electric current [4]. OTFTs have the advantages of being more affordable and processing at lower temperatures than inorganic TFTs, as well as being lighter and more flexible. Low-temperature OTFT fabrication enables solvent processing, such as inkjet printing or spin coating, and flexible plastic substrates.

Inorganic high-k materials like Ta\({}_{2}\)O\({}_{5}\), Al\({}_{2}\)O\({}_{3}\), barium zirconate titanate (BZT), barium strontium titanate (BST), HfO\({}_{2}\), TiO\({}_{2}\) and transition-metal oxides like ZrO\({}_{2}\) and Y\({}_{2}\)O\({}_{3}\) are also studied as gate dielectric materials. The deposition methods for these materials, which involve thermal evaporation, chemical vapour deposition (CVD), and RF sputtering, can be high-cost and incompatible with the inexpensive plastic substrates employed in OTFTs. The gate dielectric in OTFTs is often made of polymer materials that are able to be deposited by low-temperature solution processing (LTSP) methods and are compatible with organic semiconductors (OSCs). Some of these polymer dielectrics are employed as gate dielectrics, including poly (4-vinylphenol) (PVP) [5], CYTOP [6], polyvinyl alcohol (PVA) [7], polymethylmethacrylate (PMMA), benzo cyclobutane (BCB), SU8, polyacrylonitrile (PAN) [8] and polystyrene. Hysteresis in the \(I{-}V\) characteristic of OTFTs is caused by polymers having -OH groups, which is unsuitable for components used in pixel driver designs.

A big challenge is raising the performance of organic devices to improve their use for real-time commercial. Research has been heavily concentrated on improving the mobility of organic materials by optimizing forming procedures to increase the device’s speed. To improve device performance, it is crucial to learn the features of the semiconductor layer and semiconductor-dielectric interface, as these elements have a substantial influence on how charges travel across the device due to charge localization [9]. Defects that are present in the interface level drastically reduce the device’s performance. Therefore, one of the essential factors affecting device performance is semiconductor layer thickness. Because it can handle the internal flow of the charge carriers, which largely influences the working efficiency of the device, the semiconductor layer is essential to OTFT [10]. Apart from mobility, altering the active layer thickness and scaling the length of the channel are other ways to enhance OTFT performance. Inorganic TFTs have been found to exhibit mobility and impact ionization degradation, which intensifies significantly for short-channel transistors. Device leakage caused by currents present in the devices OFF state is undesirable and restricts the device’s potential. Short-channel lengths cause these leakage currents to grow in size, which increases static power loss. Leakage currents may so impair the performance of organic TFTs, so their study and analysis is a major area of research. TO overcome the issues, OTFT using bi-polymer layers based on squid optimization with a dielectric medium to enhance electrical characteristics.

The designed OTFT model based on a tri-polymer dielectric medium has the following major contributions:

-

Simulation and modelling of OTFT using a bi-polymer dielectric medium with squid optimization to enhance the electrical characteristics.

-

To improve the electrical mobility between the source and drain with capacitance density, insulator or dielectric medium like PEI-EP, POM-H, and SiO\({}_{2}\) are utilized.

-

Developed triple-layered dielectric polymers are validated using \(p\)-type pentacene semiconductor material.

-

To optimally select the thickness of dielectric material, squid game optimization (SGO) is used based on the capacitance of the material.

-

Evaluation of developed OTFT characteristics using TCAD for improvements in mobility (\(\mu\)), capacitance (pF), threshold voltage (\(V_{\textrm{th}}\)), and trans-conductance (S/\(\mu\)m).

The articles subsequent sections are organized as Section 2 includes various survey articles about the existing OTFT model. The developed proposed approach of the OPTFT model is described in Section 3. The experimental study of the suggested triple layer OTFT model is then shown in Section 4. In the end, Section 5 concludes the proposed article.

LITERATURE REVIEW

Several methods are presented to improve the electrical mobility in the source and drain channels created utilizing single-, bi-, and tri-layer dielectric medium. A lot of currently used methods are being researched, and a few of them are discussed here.

Jain et al. [11] introduced the triisopropylsilyl-ethynyl (TIPS)-pentacene OTFT constructed using the drop-casting approach was analyzed for device properties using physics-based 2-dimensional computational modelling. The comprehensive analysis of the effect of active layer (TIPS-pentacene) thickness of device specifications was also presented in the investigation, utilizing a simulation technique that enables calibration. Electric field strength, current On/Off ratio, current density, and mobility are some retrieved parameters that change as the active layer thickness is reduced from 500 to 100 nm. The analysis also showed that the semiconductor layer’s thickness has a significant impact in terms of the off current and the On/Off current ratio (\(I_{\textrm{On}}/I_{\textrm{Off}}\)). Additionally, 100-nm thick TIPS-pentacene that could be employed for a variety of fast-switching purposes for digital circuits achieves the greatest value of \(I_{\textrm{On}}/I_{\textrm{Off}}\). The results from simulations not only substantially resemble those from experiments, but they also offer insight on how charges are transported at the semiconductor-dielectric interface and across the TIPS-pentacene layer as an entire structure.

Dwivedi et al. [12] presented the low voltage Pentacene-based OTFTs’ numerical simulation, compact modelling, and parameter extraction techniques using technology-assisted design (TCAD). The research used device numerical simulation to modify basic semiconductor equations to accurately depict the electrical properties of devices. The compact gadget design and parameter extraction of the low-voltages pentacene-based OTFT utilizing the universal UOTFT model are presented. The experimental outcomes of manufactured pentacene-based OTFT devices were used to validate the outcomes of the compact modelling and ATLAS simulation based on the finite element approach. To compare the compact model to a simulation of a basic circuit, an inverter based on a \(p\)-type TFT was also simulated.

McCulley et al. [13] demonstrated a method for designing short-channel OTFT that significantly improved their electrical performance. The structure incorporates elements that can enhance charge injection to drastically lower the contact resistance, which restricted the functionality of short-channel organic TFTs. Furthermore, the short-channel effects that could be common for nanoscale TFTs can be significantly reduced by the design. The semiconductors, namely dinaphtho [2,3-b:2\({}^{\prime}\),3\({}^{\prime}\)-f] thieno[3,2-b] thiophene (DNTT) and pentacene, having channel lengths ranging from 200 to 800 nm and 10 to 100 nm, respectively, were used to build TFTs. One of the lowest values observed for organic TFTs, the overall source-to-drain resistance was decreased to roughly 50 ohmcm.

Dallaire et al. [14] developed the creation of poly[N,N0 bis(2-octyldodecyl) naphthalene1,4,5,8-bis(dicarboximide)-2,6-diyl] -alt-5,50 (2,20 bithiophene) based organic thin film transistors that decrease contact resistance by adding metallic interconnected layers in between the gold contacts and semiconductor. The performance of OTFT was optimized with a minimal degree of contact resistance when a 10 nm thick manganese interlayer was added. The essential characteristics of the device can be extracted using a quick and efficient method using an enhanced organic virtual-source emission diffusion approach, which was used to describe better OTFT. In comparison to popular metal-oxide-semiconductor field-effect transistor designs like the Shichman–Hodges model, the organic virtual-source emitting diffused approach produced virtually flawless predictions utilizing gate dependent contact resistance and optimal gate voltages.

Elsaegh et al. [15] established an innovative general method that explicitly considers the impacts of the source and drain links when deriving the \(I{-}V\) characteristics of OTFTs. Any TFT might use this method, subject to the device design, layer thicknesses, materials, or fabrication method. TFTs made using 2,9-diphenyl DNTT (DPh-DNTT) semiconductor and dinaphtho[2,3-b:2\({}^{\prime}\),3\({}^{\prime}\)-f]thieno [3,2-b]thiophene (DNTT) semiconductor inverted coplanar and staggered architectures have both been subjected to the extraction process. For use in Verilog-A-based computer simulations, a concise analytical model which characterizes the stable performance of the two distinct kinds of organic TFTs have been developed. The design have been effectively applied for comparing computations to metrics of single TFTs having channel lengths that vary from 4 to 100 \(\mu\)m as well as to trans-impedance amplifiers constructed using OTFTs with various channel lengths.

Numerous method discussed above has been utilized to increase electrical performance by using a number of dielectric polymers. OTFTs have a variety of applications. However, they are limited by a few issues with the coffee stain effect reduces the carrier mobility in the device [11], the high operation voltage resulting from the low gate capacitance density [12], poor solubility [13], contact resistance [14], field effect mobility is higher and also insoluble in common organic solvents [15]. Therefore, the triple layer POM-H/PEI-EP/SiO\({}_{2}\) dielectric mediums are utilized as gate insulator to address these problems.

PROPOSED METHODOLOGY

Organic electronics contain unique characteristics that are uncommon in regular electronics. Because organic electronics have shown promise due to their low temperature, low cost and quick manufacture, along with their compatibility using different types of substrates which are large in area, transparent, thin, or mechanically flexible.

Figure 1 illustrates the diagram representation of OTFT using triple-layer dielectric mediums. OTFTs are created and developed as a tri-layer dielectric structure using silicon oxide (SiO2), Poly-Ether-PEI-EP, and POM-H as dielectric layers. An OTFT serves as a transistor composed of a thin layer of current conducting organic semiconductor (OSC), three electrodes and an insulator layer. The organic semiconductor is directly in connection with two of the electrodes—the source (S) and drain (D)—while the gate (G) electrode is separated from the semiconductor by a dielectric insulator. The two gate dielectric materials are Poly-PEI-EP and POM-H, and the active OSC material is pentacene where the \(p\)-type pentacene semiconductor is used to validate the triple layer structure. The source and drain metal electrodes are both made of copper (Cu).

Triple-Layer OTFT Design

Atlas version 5.26.1.R is employed to construct the triple-layer OTFT structure. The OTFT model’s mesh analysis should initially be carried out using the specified region from the structure design. The silicon substrate is doped at a \(1.6\times 10^{16}\) constant concentration to yield a significantly \(n\)-doped silicon with a thickness of 0.8 m, as well as a silicone substrate is covered with a first dielectric layer made of silicon dioxide. A 0.03 m pentacene semiconductor positioned on top of the triple layer dielectric medium was then used to evaluate the proposed OTFT model performance. After that, POM-H and PEI-EP has a thickness of 0.25 \(\mu\)m are implanted above the silicone dioxide. The Lombardi CVT model with \(3\times 10^{10}\) interface charge is utilized to set the model material. Following that, the triple-layer OTFT design with 0.05 \(\mu\)m thickness uses the copper terminal as its source and drain.

Bi-Polymer Dielectric Medium

OTFT concept uses a bi-polymer dielectric medium in order to attain the insulator surface property. The hydrophobicity and degree of smoothness of the insulator are two important factors taken into account for the bi-layer polymer OTFT model. Several studies have shown that roughness on surfaces has a variety of impacts, including the distribution of charges, restriction of charge flow, and the formation of surface traps. Strong hysteresis effects and high output voltage are consequently prevalent. According to research, hydrophilic surfaces with –OH groups, particularly raw SiO\({}_{2}\), can easily trap electrons, which results in poor OTFT performance. Because of the advantages of surface qualities, such as being substantially hydrophobic and finer, solution-processed dielectrics using hydroxyl-free polymers have been proposed for resolving the concerns.

POM-H. POM-H is one of the most flexible technical materials on the market right now since it also has excellent electrical insulating capabilities and remarkable machining features. POM, also known as acetal, polyformaldehyde, and polyacetal, can be described as poly-oxy-methylene. A typical thermoplastic-based polymer with a greater molecular weight that is used in a variety of manufacturing applications. Formaldehyde POM copolymer is composed of repeating units of –CH\({}_{2}\)O–. POM polymers offer superior mechanical qualities includes high tensile strength, lower friction, great fatigue resistance, and better stiffness and toughness. POM also exhibits strong scratch resistance and minimal moisture absorption qualities. It is also resistant to a variety of strong bases, weak acids and organic solvents. The polymeric substance also dissolves in hot and acidic (pH 4) settings, in accordance with the chemical properties of POM. POM is often mixed by ethylene oxide to enhance and alter the chemical composition and endurance of the polymer. The chemical formula for POM-H is given below

PEI-EP. Thin film is made by spin coating a mixture of PEI and EP with chloroform for two hours, followed by a low-temperature applying process at 70\({}^{\circ}\)C, which can be utilized for creating the PEI-EP polymer [16]. The amine groups in PEI and the epoxy groups in EP combine at this level of temperature to generate the hydroxyl groups that combine the secondary and tertiary amine groups. Epoxy groups and recently formed hydroxyl groups react in EP. The creation of an amine group along with ether link crosslinking network is the outcome of this process. Due to the PEI-EP dielectric, the device can operate for a duration of two months in situations with a humidity range of 20 to 100\(\%\) without experiencing any performance degradation. This has minimum hysteresis transfer features, an uninterrupted operating rate and a high electrical performance. These outstanding benefits make PEI-EP a suitable dielectric choice for solution-processed adaptable OTFTs.

The PEI-EP polymers and POM-H polymer characteristics are listed in Table 1. Anion polymers of formaldehyde are exchanged to make POM-H, which has good crystallization and provides a material with outstanding strength and stiffness. POM-H is advantageous for applications that need both resistance to fatigue and a relatively low coefficient of thermal expansion. With an initial decomposition temperature between 340 and 70\({}^{\circ}\)C and a low process temperature, the PEI-EP polymer dielectric offers greater temperature resistance.

Electrical Characteristics of a Triple-Layered OTFT

No carriers of charge exist in an organic semiconductor which is fundamentally undoped at zero gate voltage. To introduce particles that are charged into an organic substance, the source and drain electrodes are transferred to the dielectric. A positive or negative voltage at the gate must be given to a semiconductor in order to form an \(n\) or \(p\)-type conducting channel. When the metallic functioning of both the source and drain relates to the HOMO-LUMO degree of the OSC, it is possible to partition both positive and negative charges between the source and drain using electrodes and voltage. A \(p\)-type semiconductor has a significant number of holes as carriers. When a negatively charged gate voltage is applied, an electric field is created that passes perpendicular to the dielectric, which causes an accumulation of holes to form at the dielectric-semiconductor contact. A voltage is applied to the source-drain terminals, causing current to flow between the two contacts via the accumulation layer. \(V_{\textrm{d}}\ll V_{\textrm{g}}\) \({-}\) \(V_{\textrm{th}}\) the channel is continuous in the linear region and drain current (\(I_{\textrm{d}})\) is represented as,

When \(V_{\textrm{d}}>V_{\textrm{g}}-V_{\textrm{th}}\) is raised further, the electrical field at the drain contact will become 0. Thus, a pinch off region surrounds the drain contact. The saturation zone starts above this pinch-off point, and the only factor left to control the drain current is the gate voltage. This region has quadratically changing drain current:

Equations (2) and (3) represent the method for calculating mobility in OTFTs. Because of their greater mobility, organic semiconductor layers’ electrical mobility and conductivity are consistently performing well in terms of transistor characteristics. The field effect mobility, which gauges how quickly charge carriers may travel inside a device, is represented as the drift average charge carrier velocity for every given electric field. The mobility of various materials can be examined using their transfer characteristics. Trans-conductance \(g_{\textrm{m}}\) describes mobility in the linear region.

To demonstrate the mobility of the linear area (\(\mu_{\textrm{ln}}\)), a small, constant \(V_{\textrm{D}}\) is associated.

The mobility of the saturation area (\(\mu_{\textrm{st}}\)) is represented by Eq. (6)

where, terms \(w_{\textrm{Ch}}\) and \(l_{\textrm{Ch}}\) represent the channel width and length, respectively, \(V_{\textrm{g}}\) denoted as gate voltage and \(C_{\textrm{G}}\) refers to the gate capacitance insulator. The \(I_{\textrm{On}}/I_{\textrm{Off}}\) ratio evaluates the level of current flowing in accumulation modes to that flowing in depletion modes. The OTFT starts to conduct at the dielectric semiconductor contact at a minimal gate voltage called the threshold voltage (\(V_{\textrm{th}}\)). Devices with low threshold voltage and shorter channel lengths and thicker organic layers perform better because the organic layer thickness impacts the OTFTs’ threshold voltage. \(I_{\textrm{On}}/I_{\textrm{Off}}\) is calculated utilizing the transfer characteristics of numerous OTFT structures. The triple layer OTFT’s designed specifications are provided in Table 2.

Squid game optimizer (SGO). Squid game optimizer (SGO) is offered as a unique metaheuristic algorithm based on the basic principles of an ancient Korean game [17]. Squid game, sometimes referred to ojingeo, was founded an outdoor game for Korean kids and is essentially a combination of hopscotch and tag. A multiplayer game called squid game has two main goals: It is typically played on broad, open spaces with no predetermined rules regarding dimensions and size, with attackers aiming to finish their target whilst teams try to remove one another. According to historical evidence, the playing area for this kind of game often looks like a squid and is roughly half the dimension of a typical basketball court. This algorithm’s mathematical model is created using a population of potential solutions and a first-stage random initialization process. The solution candidates are classified into offensive and defensive player groups. The offensive player moves randomly toward the defensive players in an attempt to cause a fight among the defensive players. The position updating procedure is carried out, and new position vectors are generated by taking into account the successful situations of the players on both sides, which are computed using the objective function.

Step 1: Initialization

Consider the combination of thickness amount for PEI-EP and POM-H that range from 0.3 to 0.8 \(\mu\)m as the initial population for optimization.

Step 2: Fitness function

To estimate the ideal thickness for both PEI-EP and POM-H, the following fitness function is utilized:

Equations (9) and (10) are utilized for calculating this function based on capacitance maximization \((C_{\textrm{ins}})\) and threshold voltage \(\left(V_{\textrm{th}}\right)\) minimizing so as to enhance mobility and reduce leakage current. Where \(\varepsilon_{0}\) is represented as vacuum permittivity, \(t_{\textrm{i}}\) is indicated as the dielectric thickness and \(\varepsilon_{\textrm{ins}}\) is denoted as the gate dielectric relative permittivity.

Step 3: Updating

The various PEI-EP and POM-H thickness values are updated based on equation 11 until the perfect thickness value is discovered.

where, o and p is the number of successful offensive (scof) and successful defensive (scdef) players in successful offensive group (SOG), and successful defensive group (SDG) respectively; \(u_{m}^{\textrm{ofnew3}}\) shows the upcoming position vector of the \(m\)th successful offensive player \(u_{m}^{\textrm{ofnew1}}\)which passes the bridge; BS indicates the best solution candidate or the most successful offensive player in the SOG;\(g_{1}\) and \(g_{2}\) are two random numbers in the range of [0].

Step 4: Termination

After attaining the optimal value of dielectric thickness, the entire process of selecting the optimal value will be terminated.

RESULTS AND DISCUSSIONS

Utilizing Matlab and SILVACO TCAD, the proposed bi-polymer layers based on squid optimization with a dielectric medium has been designed and simulated to improve the electrical characteristics. These software tools for implementation are set up along with a 64-bit operating system, an Intel i5-3450S CPU running at 2.80 GHz, and 8 GB of RAM. In order to achieve the optimal thickness value for the dielectric medium according to the fitness function, the squid optimization algorithm is initially constructed in Matlab. Additionally, the thickness value from the TCAD is used to create the simulation model.

The design of a tri-layer dielectric of tri-layer dielectric OTFT using TCAD is illustrated in Fig. 2. Leakage current is reduced by the tri-layer dielectric medium in OTFT such as SiO\({}_{2}\), PEI-EP, and POM-H. The electrical characteristics of the OTFT model, which include the \(I{-}V\) and transfer characteristics, mobility, capacitance and transconductance can be obtained from this simulation.

I–V Characteristics of the Tri-Layer Dielectric OTFT Model

OTFT model drain current characteristics are performed between the drain current (ID) and the drain source voltage (V\({}_{\textrm{DS}}\)) while maintaining the gate source voltage (V\({}_{\textrm{GS}}\)) constant.

Drain current characteristics of the OTFT model for different dielectric material is shown in Fig. 3. Proposed dielectric material used as POM-H/PEI-EP is compared with existing material are polyacrylic acid (PAA)/poly (methyl methacrylate) [18] and polyvinyl alcohol (PVA)/poly-4-vinylphenol (PVP) [19]. The OTFT model employs the dielectric materials SiO\({}_{2}\), PEI-EP, and POM-H, with respective dielectric constant values of 3.9, 3.8, and 3.8. Due to the usage of organic polymers in the developed model, the proposed dielectric materials results with better drain current characteristics compared to the conventional SiO\({}_{2}\) material.

\(I{-}V\) characteristics for various dielectric material obtained from drain current is listed in Table 3. The table shows that the drain current attained for the proposed method is higher when compared to other existing dielectric materials, which are PMMA/PAA and PVA/PVP.

Transfer Characteristics of Tri-Layer Dielectric OTFT Model

The relationship between an OTFT’s gate (input) voltage and drain (output) current is shown by the device’s transfer characteristics. The OTFT threshold voltage can be calculated relying on these transfer properties.

The transfer characteristics of OTFT models based on various dielectric mediums are shown in Fig. 4. POM-H/PEI-EP dielectric material is used in the proposed method and compared with existing materials are polyacrylic acid (PAA)/poly (methyl methacrylate) and polyvinyl alcohol (PVA)/poly-4-vinylphenol (PVP). A transistor starts conducting current and leaves the off-state at a gate voltage known as the threshold voltage (V\({}_{\textrm{th}}\)), which may be observed on the transfer characteristics curve.

Table 4 compares the OTFT model with proposed and existing dielectric materials by highlighting the transfer characteristics of each type of material. From this analysis, it can be observed that the OTFT model that combines POM-H, PEI-EP, and SiO\({}_{2}\) achieves higher transfer characteristics.

A dielectric material-based capacitance for OTFT model is represented in Fig. 5. Gate capacitance in electronics refers to the capacitance of a field-effect transistor’s (FET) gate terminal. In terms of integrated circuit technology, it can be stated as the absolute capacitance of the transistor gate or as the capacitance/unit area. As it generates the requisite channel charge for operating, gate capacitance is crucial.

The evaluation of capacitance for various dielectric materials is given in Table 5. The performance of the device is dependent on \(I{-}V\) and transfer properties based on the assessment of capacitance. This analysis shows that triple layer dielectric mediums have a larger capacitance, which lessens the source-drain channel leakage current than those used in earlier approaches.

Figure 6 depicts the OTFT model’s mobility with various dielectric materials. For transistor properties, the mobility as well as conductivity of the organic semiconductor layer are attracting a lot of attention, and the transistor needs higher mobility to function reliably. The average rate of charge carrier drift velocity per unit applied electric field and a measurement in which the charge carriers can migrate within a device are known as field effect mobility.

The mobility of the POM-H/PEI-EP, PMMA/PAA and PVA/PVP dielectric material used in OTFT models is compared in Table 6. The mobility of the OTFT model increases as the gate voltage varies. The triple layer OTFT model achieves higher levels of mobility than the other existing OTFT methods.

CONCLUSIONS

Thin film transistor technology has been using low-\(k\) dielectric as a dielectric material for the last decade. The thickness of the active layer and the dielectric material can be reduced to reduce the device’s size. Drain current increases as a result of increased capacitances caused by a reduction in dielectric material thickness. But as the dielectric material is further reduced, leakage current occurs, which affects other parameters such as the threshold voltage. Use high-\(k\) dielectric materials to increase overall capacitances and reduce leakage current in order to improve transistor performance without reducing the thickness of the dielectric material. The bi-polymer layers based on squid optimization with dielectric media is proposed as a solution to the aforementioned limitations. In this designed model, substrate material is taken as silicon material and the biopolymer is utilized as POM-H and PEI-EP, this three dielectric material is referred as the trilayer OTFT model. Then, using the squid gamer optimization approach to determine the material thickness, bi-polymer dielectric materials constructed of POM-H/PEI-EP are used as insulation. These three-layer dielectric materials provide excellent insulating levels and smooth surfaces in addition to higher capacitance. To assess the effectiveness of the developed model, a pentacene-based semiconductor is positioned on top of three layers of dielectric medium. The performance is evaluated based on the electrical characteristics such as \(I{-}V\), transfer characteristics, mobility (\(\mu\)) and capacitance (pF) to determine the performance of the device. In addition to, the performance evaluation is compared with other existing materials like PMMA/PAA and PVA/PVP. The proposed model’s achieved electrical performance includes mobility of 355 cm\({}^{2}\) V\({}^{-1}\) s\({}^{-1}\) and capacitance of 7.00 pF. The proposed dielectric material performs better when compared to other existing methods. Future real-time devices can be use the developed and simulated tri-layer OTFT model to boost functionality and reduce leakage current.

REFERENCES

P. Mittal, S. Yadav, and Sh. Negi, ‘‘Advancements for organic thin film transistors: Structures, materials, performance parameters, influencing factors, models, fabrication, reliability and applications,’’ Mater. Sci. Semicond. Process. 133, 105975 (2021). https://doi.org/10.1016/j.mssp.2021.105975

D. Ho, J. Lee, S. Park, Yo. Park, K. Cho, F. Campana, D. Lanari, A. Facchetti, S. Seo, Ch. Kim, A. Marrocchi, and L. Vaccaro, ‘‘Green solvents for organic thin-film transistor processing,’’ J. Mater. Chem. C 8, 5786–5794 (2020). https://doi.org/10.1039/d0tc00512f

R. K. Hallani, M. Moser, H. Bristow, M. V. C. Jenart, H. Faber, M. Neophytou, E. Yarali, A. F. Paterson, T. D. Anthopoulos, and I. Mcculloch, ‘‘Low-temperature cross-linking benzocyclobutene based polymer dielectric for organic thin film transistors on plastic substrates,’’ J. Org. Chem. 85, 277–283 (2019). https://doi.org/10.1021/acs.joc.9b02981

K. B. R. Teja and N. Gupta, ‘‘Low-\(k\) polymer gate dielectric selection for organic thin-film transistors (OTFTs) using material selection methodologies,’’ J. Comput. Electron. 18, 872–881 (2019). https://doi.org/10.1007/s10825-019-01343-1

J.-H. Kwon, J.-H. Choi, H. Lee, J.-H. Bae, and J. Park, ‘‘Structural modification of poly(4-vinylphenol) insulators in pentacene transistors by using dimethyl ketone,’’ Mol. Cryst.s Liq. Cryst.s 704, 145–152 (2020). https://doi.org/10.1080/15421406.2020.1741815

G. Kim, C. Fuentes-Hernandez, X. Jia, and B. Kippelen, ‘‘Organic thin-film transistors with a bottom bilayer gate dielectric having a low operating voltage and high operational stability,’’ ACS Appl. Electron. Mater. 2, 2813–2818 (2020). https://doi.org/10.1021/acsaelm.0c00487

N. Afsharimani and B. Nysten, ‘‘Hybrid gate dielectrics: A comparative study between polyvinyl alcohol/\(\hbox{SiO}_{2}\) nanocomposite and pure polyvinyl alcohol thin-film transistors,’’ Bull. Mater. Sci. 42, 26 (2019). https://doi.org/10.1007/s12034-018-1695-y

J. Dong, Ya. Wang, T. Mori, and T. Michinobu, ‘‘Improving the air-stability of \(n\)-type organic thin-film transistors by polyacrylonitrile additive,’’ Jpn. J. Appl. Phys. 59, SDDC05 (2019). https://doi.org/10.7567/1347-4065/ab5c4b

P. Xie, T. Liu, J. Sun, J. Jiang, Yo. Yuan, Yo. Gao, J. Zhou, and J. Yang, ‘‘Solution-processed ultra-flexible C8-BTBT organic thin-film transistors with the corrected mobility over 18 cm\({}^{2}\)/(V s),’’ Sci. Bull. 65, 791–795 (2020). https://doi.org/10.1016/j.scib.2020.03.013

Yo. Song and Yo. Ha, ‘‘One-step fabricated and solution-processed hybrid gate dielectrics for low-voltage organic thin-film transistors,’’ Bull. Korean Chem. Soc. 42, 983–987 (2021). https://doi.org/10.1002/bkcs.12290

S. K. Jain, A. M. Joshi, and D. Bharti, ‘‘Performance investigation of organic thin film transistor on varying thickness of semiconductor material: An experimentally verified simulation study,’’ Semiconductors 54, 1483–1489 (2020). https://doi.org/10.1134/s106378262011010x

A. D. D. Dwivedi, S. K. Jain, R. D. Dwivedi, and Sh. Dadhich, ‘‘Numerical simulation and compact modeling of low voltage pentacene based OTFTs,’’ J. Sci.: Adv. Mater. Devices 4, 561–567 (2019). https://doi.org/10.1016/j.jsamd.2019.10.006

C. M. McCulley, X. Xu, K. Liang, X. Wang, L. Wang, and A. Dodabalapur, ‘‘Nanospike electrode designs for improved electrical performance in nanoscale organic thin-film transistors,’’ ACS Appl. Electron. Mater. 3, 4284–4290 (2021). https://doi.org/10.1021/acsaelm.1c00813

N. J. Dallaire, S. Brixi, M. Claus, S. Blawid, and B. H. Lessard, ‘‘Benchmarking contact quality in N-type organic thin film transistors through an improved virtual-source emission-diffusion model,’’ Appl. Phys. Rev. 9, 011418 (2022). https://doi.org/10.1063/5.0078907

S. Elsaegh, U. Zschieschang, J. W. Borchert, H. Klauk, H. Zappe, and Yi. Manoli, ‘‘Compact DC modeling of organic thin-film transistors including their parasitic non-linear contact effects based on a novel extraction method,’’ IEEE Trans. Electron Devices 66, 4907–4914 (2019). https://doi.org/10.1109/ted.2019.2941438

M. Zhang, C. Zhang, Ya. Yang, H. Ren, J. Zhang, X. Zhao, Ya. Tong, Q. Tang, and Yi. Liu, ‘‘Highly stable nonhydroxyl antisolvent polymer dielectric: A new strategy towards high-performance low-temperature solution-processed ultraflexible organic transistors for skin-inspired electronics,’’ Research 2021, 9897353 (2021). https://doi.org/10.34133/2021/9897353

M. Azizi, M. Baghalzadeh Shishehgarkhaneh, M. Basiri, and R. C. Moehler, ‘‘Squid game optimizer (SGO): A novel metaheuristic algorithm,’’ Sci. Rep. 13, 5373 (2023). https://doi.org/10.1038/s41598-023-32465-z

Z. Yin, M. Yin, Z. Liu, Ya. Zhang, A. P. Zhang, and Q. Zheng, ‘‘Solution-processed bilayer dielectrics for flexible low-voltage organic field-effect transistors in pressure-sensing applications,’’ Adv. Sci. 5, 1701041 (2018). https://doi.org/10.1002/advs.201701041

C.-L. Fan, H.-Y. Tsao, Y.-S. Shiah, C.-W. Yao, and P.-W. Cheng, ‘‘Performance enhancement of pentacene-based organic thin-film transistors using a high-K PVA/low-K PVP bilayer as the gate insulator,’’ Polymers 13, 3941 (2021). https://doi.org/10.3390/polym13223941

Funding

This work was supported by ongoing institutional funding. No additional grants to carry out or direct this particular research were obtained.

Author information

Authors and Affiliations

Contributions

The corresponding author claims the major contribution of the paper including formulation, analysis and editing. The co-author provides guidance to verify the analysis result and manuscript editing.

Corresponding author

Ethics declarations

The authors of this work declared that they have no conflicts of interest. We declare that we do not have any commercial or associative interest that represents a conflict of interest in connection with the work submitted.

Additional information

Publisher’s Note.

Allerton Press remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

About this article

Cite this article

Panghal, D., Yadav, R. Design and Simulation of OTFT Using Bi-Polymer Layers Based on Squid Optimization with Dielectric Medium to Enhance Electrical Characteristics. Optoelectron.Instrument.Proc. 60, 284–296 (2024). https://doi.org/10.3103/S8756699024700341

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.3103/S8756699024700341