Abstract

Physics-based two-dimensional numerical simulations are performed to analyze the device characteristics of tri-isopropylsilylethynyl (TIPS)-pentacene organic thin-film transistor (OTFT) fabricated using drop-casting technique. Further, using simulation technique enabling calibration this paper also presents the systematic study of the impact of active layer (TIPS-pentacene) thickness on device characteristics. The extracted parameters such as electric field intensity, current density, current On/Off ratio, and mobility exhibit variation with scaling down in active layer thickness from 500 to 100 nm. The study also revealed that Off current and On/Off current ratio (IOn/IOff) is highly dependent on the thickness of the semiconductor layer. Furthermore, the highest value of IOn/IOff is obtained at 100-nm thickness of TIPS-pentacene, which can be used for various fast-switching applications in digital circuits. Simulated results are not only reasonably matching with experimental results but also provide insight on charge transportation at the semiconductor-dielectric interface and in the bulk of TIPS-pentacene layer.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 INTRODUCTION

Organic semiconductors have shown great potential to replace the conventional amorphous silicon (a-Si) as the material for active matrix displays on thin-film transistors (TFTs). Organic electronic materials are superior to inorganic materials in terms of low-cost manufacturing capability. Research based on organic semiconductors has developed large-area electronic devices such as OTFT, organic light-emitting diodes (OLEDs), organic solar cells (OSC), etc. OTFTs offer a wide range of applications over the past two decades, such as low-cost displays [1], organic memories [2], key radio-frequency tags [3], polymer circuits, and sensors [4]. The performance of OTFT for real-time commercial applications depends on various parameters such as On-to-Off current ratio, mobility, current density, electric field, and the threshold voltage in the device [5]. These parameters are often affected by the combination of the various active materials, the geometry of the device, thin-film particle size, trap state, and thickness of semiconductor layers [6, 7]. To improve device performance, it is necessary to understand the behavior of semiconductor layer and semiconductor-dielectric interface because it extremely affects the charge transport in the device due to charge localization [8]. The performance of the device degrades significantly due to defects available at the interface level. Thus semiconductor layer thickness is one of the important parameters for device performance. The semiconductor layer is critical to OTFT because it can accommodate the internal transport of charge carriers, which primarily determines the performance of the device. OTFT’s can be synthesized with a variety of functional groups and variable thickness of OSC for desired electrical properties. Many researcher’s studies [9, 10] have also reported the effect of active layer thickness on parasitic access resistance. This would be resulting in changes in source and drain resistance, which affects the device performance. Various studies [11–16] have been reported for the impact of semiconductor layer thickness on the effectiveness of OTFT with a variety of organic semiconductors as P3HT [6], 4QT4 (Dibutylquaterthiophene) [9]. Most research efforts have been dedicated to describe the morphology of the active layer, interface at dielectric.

This paper covers the detailed study of electrical parameter and microscopic analysis of physics-based parameters with variation in thickness of the semiconductor layer from a deep device physics point of view. The thickness of the active layer is varied to find their effect on physical parameters such as charge density, electric field, On-to-Off current ratio, and mobility.

Due to the experimental limitations in providing evidence, there is still a lack of detailed understanding from a deep physics point of view. By doing analysis based on experimental data only, it is very difficult to know about real physics involved with the device. Two-dimensional physical numerical modeling proved to be very useful in understanding the microscopic behavior of the device. Using 2D simulation, it is also easy to study those various physical quantities which is difficult to understand with experimental data alone. Hence, the detailed analysis of physical quantities and the electrical parameters is done using two-dimensional numerical simulations. The two-dimensional device simulation would be helpful to become familiar with the basic functions of the device as well as the optimization of the device structure.

2 DEVICE SIMULATION

This section introduces the device structure under consideration and simulation parameter used for our designed OTFT and device physics involved in it.

2.1 Experimentally Verified Numerical Simulation for BGTC OTFT

A schematic diagram of TIPS-pentacene based OTFT is presented in Fig. 1.

Two-dimensional numerical simulation is performed using a device simulator named ATLAS (SILVACO), in which the finite element method is used. Simulator solves drift-diffusion equations, continuity equations, and Poisson’s equation for electrons and holes. Bottom gate top contact (BGTC) TIPS-pentacene based OTFTs as shown in Fig. 1 is simulated for validation. All structural parameters of the simulated device are given in Table 1.

The material properties of TIPS-pentacene semiconductors are listed in Table 2.

As defined in Table 2, the relative permittivity, hole affinity, and energy bandgap of TIPS-pentacene are considered as 4, 2.8, and 1.8 eV, respectively [15].

The density of states in the valence band and conduction band is taken as 2.0 × 1021 cm–3 [15]. After enabling calibration of the simulator, the same device with scaling down thickness Tosc of organic semiconducting material from 500 to 100 nm is simulated keeping all other parameters constant.

The schematic of the structure under consideration is similar to one studied experimentally by Deepak Bharti et al. [16]. For validation of simulated device characteristic, experimental data are taken from [16], where device was fabricated using drop-cast technique. In the device, the silicon oxide layer of 300 nm placed on silicon substrate worked as a gate dielectric. Next, an organic semiconductor layer of TIPS-pentacene having a thickness of 500 nm was placed on the gate dielectric. Gold contacts with a thickness of 200 nm were deposited on the top to define source/drain electrodes. The OTFT has a channel length of 237 μm and a channel width of 178 μm.

2.2 Device Physics Involved in OTFT

To explain the charge transport process in organic material like TIPS-pentacene, the Poole–Frenkel mobility model is used in ATLAS simulation. In the Poole–Frenkel model, the conduction of charge carriers occurs due to improved excitation of trapped carriers in the electric field. Poole–Frenkel mobility model [18] in mathematical form can be presented as in Eq. (1).

μ(E) is field-dependent mobility, zero-field mobility is given by μ0, ΔEa is zero field activation, β is the Poole–Frenkel factor, γ is the fitting parameter, the electric field is denoted by E, Boltzmann constant is k and T denotes temperature. Thermionic emission and Poole–Frankel barrier lowering are included in the ATLAS simulations.

The physics involved in given ATLAS simulation can be calculated by solving basic device equations simultaneously including Poisson’s equation [21], electron and hole continuity equation, charge transfer equation, and defect density of states equation. The Poisson equation [22, 23] determines the electric field intensity in the given device based on the internal movement of the carriers and the distribution of the fixed charges.

where

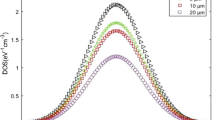

For studying the physics of density of states of organic semiconductor layers, Gaussian density of states model is used in simulations. Using the Gaussian distribution density of states G(E) containing four bands (tail bands and deep energy level bands) can be modeled [18] as given in Eqs. (2)–(6). Conduction band energy (EC), valence energy band (EV), and trap energy (E) are labelled with subscripts A, T, G, D representing the acceptor, tail, Gaussian, and donor states, respectively. nTD, nTA, wTD, wTA are conduction band edge intercept density, valance band edge intercept density, conduction band characteristic attenuation energy, and valance band characteristic attenuation energy, respectively, for exponential tails. nGA, nGD, wGD, wGA are acceptor state density, donor state density, acceptor characteristic attenuation energy, and donor characteristic attenuation energy for Gaussian distribution. EGA and EGD are peak energy for Gaussian distribution.

3 RESULTS AND DISCUSSION

In this section, the device characteristic of organic thin-film transistors (OTFTs) fabricated with TIPS-pentacene is validated with the simulated result using the finite element method for 2D numerical simulations. The device simulation includes a field-dependent mobility model including traps. Later the performance of OTFT in terms of On-to-Off ratio, electric field, and current density is examined for different active layer thickness varying from 500 to 100 nm.

The device as given in Fig. 2 is provided with a forward sweep with the step of –5 V with an incremental gate bias voltage from 0 to –25 V.

Simulated output characteristics of a TIPS-pentacene OTFT using device parameters in Table 2 are validated with experimental characteristics and almost a close matching is observed as shown in Fig. 2. Output characteristics are exhibiting the saturation nature at higher drain voltage.

Figure 3 transfer characteristic (drain current versus gate voltage) for different thicknesses of semiconductors such as 500, 300, 200, and 100 nm was simulated with the same W/L and drain voltage VDS of –30 V. It can be observed that Off current is strongly dependent on the thickness of the semiconductor layer. Off current raises with an increase in semiconductor thickness due to an increase in the bulk current but on current almost remains constant.

Figure 4 shows that the majority of the current in the device flows from the accumulation area that is near the interface of the dielectric and OSC layer. Bulk current is also associated with drain current which increases with an increase in the thickness of the TIPS-pentacene but the share of the bulk current in total drain current is much less.

The larger thickness of the active layer leads to more of the current in the OTFT due to the presence of more bulk charge. In the device, injection of current starts from source contact then passes through the semiconductor film, reaches the dielectric interface, and finally takes out from the drain contact. As shown in Fig. 5, at 100, 200, 300, and 500 nm vertical electric field magnitude have almost the same magnitude but higher electric field is generated in the thinner active layer, which forces more charge carrier to the semiconductor dielectric interface thus the charge localization increase near the surface of dielectric field.

Charge accumulation is slightly away from the surface of dielectric so that accumulated charge carriers go across less trapping due to dipoles near the surface of the insulator. This shows improved device performance for the thinner active layer. It is clear from Fig. 6 that the device with a thinner active layer has more current density due to the lesser area.

The majority of the current in the device flows from the accumulation area that is near the interface of the dielectric and OSC layer. Table 3 shows the comparison of electrical and physical parameters like electric field, current density mobility, maximum drain current, and On-to-Off current ratio at a different thicknesses of semiconductor layer keeping all other parameters constant.

The device with a thinner active layer shows better performance. Thinner active layer leads to less Off current and hence increase in On-to-Off current ratio due to almost constant On current.

4 CONCLUSIONS

In conclusion, the impact of the scaling down the semiconductor thickness (varying from 500 to 100 nm) on parameters such as electric field, current density, On-to-Off current ratio, and mobility is comparatively analyzed with the help of a field-dependent mobility model and density of defects states model in ATLAS simulation. Also the experimental and simulated characteristics of the device are reasonably matched. It has been observed that the device with a thinner active layer performs better and improves overall performance. Optimization of thickness is one of the important parameters to improve device performance and employability in real-time applications such as displays, RFID tags and practical switching applications.

REFERENCES

M. Mizukami, N. Hirohata, T. Iseki, K. Ohtawara, T. Tada, S. Yagyu, T. Abe, T. Suzuki, Y. Fujisaki, Y. Inoue, S. Tokito, and T. Kurita, IEEE Electron Dev. Lett. 27, 249 (2006).

P. Mittal, Y. S. Negi, and R. K. Singh, J. Semicond. 35, 124002 (2014).

T. Zaki, R. Rodel, F. Letzkus, H. Richter, U. Zschieschang, H. Klauk, and J. N. Burghartz, Org. Electron. 14, 1318 (2013).

S. Sharma and T. Varma, Mater. Res. Express 6, 025005 (2018).

W. Wondmagegn and R. Pieper, J. Comput. Electron. 8, 19 (2009).

P. Vimala and S. T. S. Arun, Semiconductors 54, 501 (2020).

B. C. Shekar, J. Lee, and S. Woo-Rhee, Korean J. Chem. Eng. 21, 267 (2004).

Z. Tang and C. R. Wie, Solid-State Electron. 54, 259 (2009).

M. Kano, T. Minari, K. Tsukagoshi, and H. Maeda, Appl. Phys. Lett. 98, 073307 (2011).

H. Wang, L. Li, Z. Ji, C. Lu, J. Guo, L. Wang, and M. Liu, IEEE Electron Dev. Lett. 34, 69 (2013).

C. Y. Han, Y. X. Ma, W. M. Tang, X. L. Wang, and P. T. Lai, IEEE Electron Dev. Lett. 38, 744 (2017).

S. K. Tripathi, M. S. Ansari, and A. M. Joshi, VLSI Des. 2018, 1080817 (2018).

R. Schroeder, L. Majewski, and M. Grell, Appl. Phys. Lett. 83, 3201 (2003).

A. Takshi, A. Dimopoulos, and J. D. Madden, IEEE Trans. Electron Dev. 55, 276 (2008).

D. Gupta and Y. Hong, Org. Electron. 11, 127 (2010).

D. Bharti and S. P. Tiwari, Synth. Met. 221, 186 (2016).

D. Gupta, M. Katiyar, and D. Gupta, Org. Electron. 10, 775 (2009).

ATLAS and ATHENA User’s Manual: Process and Device Simulation Software (Silvaco Int., Santa Clara, 2012).

D. Gupta, N. Jeon, and S. Yoo, Org. Electron. 9, 1026 (2008).

T.-J. Ha, D. Sparrowe, and A. Dodabalapur, Org. Electron. 12, 1846 (2011).

A. Buonomo and C. di Bello, Electron. Lett. 20, 156 (1984).

D. Hertel and H. Bässler, ChemPhysChem. 9, 666 (2008).

C. H. Shim, F. Maruoka, and R. Hattori, IEEE Trans. Electron Dev. 57, 195 (2010).

Funding

This work was supported in part by the Visvesvaraya PhD scheme/MeitY of the Government of India.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

The authors declare that they have no conflict of interest.

Rights and permissions

About this article

Cite this article

Jain, S.K., Joshi, A.M. & Bharti, D. Performance Investigation of Organic Thin Film Transistor on Varying Thickness of Semiconductor Material: An Experimentally Verified Simulation Study. Semiconductors 54, 1483–1489 (2020). https://doi.org/10.1134/S106378262011010X

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S106378262011010X