Abstract

In this paper, an online junction temperature monitoring method based on the on-state voltage under high collector current density measurements for IGBT power modules is proposed. Unlike the conventional junction temperature monitoring method, the presented method can extract the junction temperature during operation without altering the modulation strategy or topology of the converter. The proposed method is verified by simulations and the JEDEC-51 standard recommended approach. To accurately extract the on-state voltage during operation, a measurement circuit that combines the advantages of both the active MOSFET clamp and the diode clamp is designed and tested. It has been shown to have good accuracy and a rapid response time. After the calibration results are obtained, the presented method is applied to a three-phase voltage source converter controlled by a closed-loop SVPWM modulation strategy.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Junction temperature is an important design and operation parameter. It is also a key factor in terms of lifetime estimation [1,2,3], reliability evaluation [4, 5], active thermal control [6,7,8,9,10,11] and over temperature protection [12] for semiconductor power devices. Junction temperature is also very important for power module [13, 14] and power converter [15] design. Power device lifetime estimation methods predict lifetime using evaluation models, where junction temperature is the most important indicator. Other than the lifetime prediction, power module reliability evaluation focuses on module failures caused by material degradation. Figure 1 illustrates a typical multilayer structure and the relative materials in IGBT modules. Most failures occur around the semiconductor chips due to the large difference coefficients of the thermal expansion between different layers, especially bond wires, semiconductor chips and solder joints, which are the inducements of bond-wire liftoff and solder joint degradation, respectively.

More importantly, for semiconductor devices, especially MOSFETs, special attention should be paid to the negative bias temperature instability (NBTI) issue [16, 17]. NBT stress-induced threshold voltage shifts for n-channel power VDMOSFETs are presented in [18]. Once n-channel devices are exposed to a negative gate bias and the temperature is evaluated at any stage of their operation, the related instabilities can actually be more serious than those found in p-channel devices. Hence, the junction temperature needs to be monitored synchronously and accurately to evaluate reliability. This is especially true for n-channel power devices.

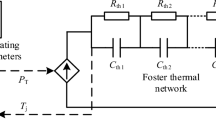

A thermal analysis of power systems reveals that some of the power semiconductor devices in the same converter can be more stressed than others [19]. Consequently, it is necessary to modify the modulation strategy according to the junction temperature as shown in Fig. 2. In addition to conventional closed loop control strategies, an additional junction temperature loop is set as a feedback to regulate thermal stress by adjusting the switching frequency and current limit.

In [20], S. Yang defined three categories of junction temperature extraction methods: electro-thermal model based junction temperature estimation methods [21, 22], sensor-based junction temperature monitoring methods [23, 24] and temperature sensitive electrical parameters (TSEPs)-based methods [25,26,27]. C. Sintamarean estimated the junction temperature rise of an IGBT module using a power device losses model and a thermal impedance network in [21]. However, it does not take the materials degradation into account. An adaptive method to update the thermal impedance model was proposed to calibrate the error caused by aging effects [22]. Nevertheless, it is hard to extract an accurate thermal impedance network under different operation conditions. Therefore, an electro-thermal model-based method is not appropriate for online junction temperature monitoring.

Other commonly used approaches to monitor junction temperature are the sensor-based methods, which include physical and optical measurement methods. Optical methods, such as infrared cameras and optical fibers, have high measurement accuracy. However, they are prevented by power module packaging and dielectric gel. Physics-based junction temperature monitoring methods are widely used in commercial power modules. Thermal sensitive resistors and thermocouples are installed on the surface of a substrate, which is the nearest available location to chips. Due to the thermal impedance between the semiconductor chip and the substrate, there exists a non-negligible error between measured temperature and real junction temperature. Although thermal test chips (TTC) [23] can be applied to extract the online junction temperature by the polysilicon sensors set in the metallization layer of a semiconductor chip, it is only a local measurement and the peak of the chip temperature caused by the void of solder is hard to obtain. More importantly, sensors are installed through power loops which means special attentions need to be paid to insulation problems and electro-magnetic interference (EMI) problems.

Using the TSEPs of a chip is a feasible approach to monitor junction temperature accurately without modifying the active surface of a device. In [24], Z. Zhang presented a junction temperature monitoring method based on turn-off delay time td_off measurement, and applied it to a half-bridge invertor. To obtain td_off accurately, the turn-off gate resistor was enlarged to 300 Ω which increases the additional turn-off losses. H. Chen analyzed the temperature variation of threshold voltage Vth and proposed a junction temperature measurement method based on it in [25]. However, the chosen gate resistor is 265 kΩ to ensure the accuracy. More importantly, the threshold voltage is hard to measure during operation.

Z. Xu used short-circuit current ISC as a TSEP and applied it to dc–dc and dc–ac converter applications in [26]. Although, it has good linearity, an additional pass-by IGBT is required to generate short-circuit conditions, which increases total power losses of a converter. In [27], D. Bergogne proposed a saturation current Isat based IGBT junction temperature measurement method. The foremost problem is that the saturation current rises exponentially with junction temperature increases. In addition, hundreds of milliamps of saturation currents are difficult to measure.

In [28], Y. Zhu used an on-state voltage drop under a low current as a TSEP and applied it to a H-bridge invertor. The foremost problem is that a very low measurement current can be easily interfered with. Moreover, an additional current source is required in parallel with the device under test. Each TSEP has its advantages and disadvantages in terms of sensitivity, linearity, complexity of additional circuits and possibility of online measurements. Among these assessment criteria, special attention should be paid to the sensitivity of the TSEPs. A method of comparing the accuracy of different TSEPs was proposed in [29] using the relative thermal sensitivity factor:

where s and val max are the temperature sensitive and maximum measured values of the TSEP, respectively. A comparisons of TSEPs for online temperature monitoring are listed in Table 1.

This paper aims at developing an accurate and compact online junction temperature monitoring method for IGBT power modules that are the most widely used in industry applications. On-state voltage at a high current is chosen as a TSEP due to its good linearity, freedom from converter normal operation interference, and measurement under the conduction state, which is extremely appropriate for over temperature protection applications. Existing Vce(HC)-based IGBT junction temperature monitoring methods [30,31,32,33] are mostly empirical. They do not analyze the relationship between the on-state voltage drop Vce(HC), the collector current Ic, the gate driver voltage Vge and the junction temperature Tj in principle. More importantly, these methods are mainly applied to thermal impedance tests under the steady state. They are seldom used in a converter under operating condition. Additionally, for high-power semiconductor devices with high blocking voltages, special attention need to be paid to the on-state voltage measurement circuits. Compared with the method proposed in [30], this paper presents a faster and more accurate on-state voltage measurement circuit. The relationships between the on-state voltage drop Vce(HC), the collector current Ic, the gate driver voltage Vge and the junction temperature Tj are analyzed in principle and simulated in MATLAB. More importantly, the temperature monitoring method is verified under both offline and online conditions.

2 Sensitivity analysis of on-state voltage under a high current

In [34] and [35], a compact model that can be used to simulate the on-state characteristic of an IGBT consists of a PiN rectifier connected in series with a MOSFET operating in its linear region as shown in Fig. 3. The PiN rectifier part of the IGBT model can be simplified as a one-dimensional structure thanks to the uniform distribution of the current flowing through the N-region.

The IGBT on-state voltage consists of two parts: PiN rectifier part voltage and MOSFET part voltage, as can be seen in (2).

where k is the Boltzmann constant, T is the junction temperature, q is the unit charge, JC is the collector current density, WN is drift region width of the IGBT, Da is the ambipolar diffusivity, ni is the intrinsic carriers concentration, La is the ambipolar diffusivity length, p is the cell pitch, LCH is the channel length, μni is the channel mobility, Cox is the oxide capacitance, and VG and VTH are gate voltage and threshold voltage, respectively.

When the on-state collector current density is low, the first term in the above equation becomes dominant. In this regime of operation, the collector current increases exponentially with an increasing on-state voltage. When the collector current density is larger, the second term becomes significant, which adds a resistance in series with the PiN rectifier voltage drop [36]. Therefore, the knee voltage can be observed in output characteristics curves as depicted in Fig. 4.

Due to different manufacturing processes, it is extremely difficult to obtain accuracy values of the semiconductor parameters of an IGBT chip, such as the cell pitch p and the channel length LCH. To analyze the sensitivity of the proposed TSEP, these unmeasurable parameters are listed hypothetically in Table 2.

For a certain IGBT chip, the cell pitch, channel length and oxide capacitance are constants, and the channel mobility and threshold voltage are temperature relative parameters and can be described in (4) and (5), respectively.

The value of the threshold voltage VTH decreases with an increase of the junction temperature due to changes of intrinsic carrier concentration. To extract KT and VTH0, the VTH of a Starpower GD400FFT65P3H IGBT module is measured offline under different junction temperatures from 50 to 125 ℃. The results are illustrated in Fig. 5. The threshold voltage at room temperature and the slope of this linear fitting equation are 6.4 V and − 0.0242 V/℃, respectively.

With all of the above parameters and equations, the on-state voltage under a high current Vce(HC) is calculated under different junction temperatures T and collector current densities JC as shown in Fig. 6.

As illustrated in Fig. 6, the IGBT on-state voltage has a positive linear correlation with junction temperature under certain gate driver conditions and collector current densities. It should be noticed that sensitivity increases with the collector current density, which shows great potential in power electronics device junction temperature monitoring applications.

With the converter operating, both the power module and driver circuit are heated. Since the parasitic parameters in gate loop and components on driver circuit vary with junction temperature, the gate voltage experiences a tiny change after long operating time. Supposing the variation range of the gate voltage is ± 0.1 V, the on-state voltage under different junction temperatures can be seen in Fig. 7. The maximum voltage deviation is around 12 mV which leads to a measurement error of less than than 5℃.

3 Formatting Vce measurement method implementation

To monitor the junction temperature based on Vce measurements, a simultaneously on-state voltage extraction circuit with a high measurement accuracy (Mv range), a high blocking capability (kV range) and a fast dynamic response (us range) are demanded. Unlike power device current measurement solutions, it is extremely difficult to obtain the on-state voltage directly using a conventional oscilloscope due to the limits of its measurement resolution. As an example, the blocking voltage is set to 800 V and a conventional 12-bit Tektronix MSO44 oscilloscope [37] is employed as measurement equipment. Consequently, the minimum significant measurement value corresponds to 800/212 ≈ 195 mV, which is nearly one tenth of the on-state voltage of a typical IGBT. In this case, the voltage waveform captured by the oscilloscope is difficult to analyze, as shown in Fig. 8.

The three most commonly used on-state voltage measurement circuits are depicted in Fig. 9 [38], Fig. 10 [39] and Fig. 11 [40], respectively. The on-state voltage measurement circuit illustrated in Fig. 9 uses the active MOSFET S1 to block DC link voltage during the DUT off-state. When the DUT is under the conducting state, the output of the measurement circuit can be calculated as (6). Due to the extremely low on-state resistance, the measurement value of output voltage Vo,1 is almost equal to the on-state voltage of the DUT.

Regarding the transition between the on and off states, an active control strategy is adopted and applied to clamp MOSFET S1, which increases the complexity of this measurement circuit. More importantly, the clamp MOSFET should be selected as a power MOSFET and a complex gate driver circuit must be integrated into the on-state voltage measurement circuit.

As shown in Fig. 10, a high-voltage diode D1 is chosen as the clamp component. During the DUT off-state, the clamp diode D1 blocks the DC link voltage and protects the measurement circuit. When the DUT is conducting, the measurement value is shown as (7).

where VD1 is the on-state voltage of the clamp diode, which is relevant to the diode junction temperature and the forward bias current generate by V1. When compared to a clamp MOSFET, this clamp circuit is more compact. However, the output value involves a temperature dependent variable VD1 that makes it difficult to extract the real on-state voltage of the DUT.

Another approach to blocking DC link voltage is the use of an R–D clamp circuit, as depicted in Fig. 11. A high-voltage resistor accompanied by a zener diode ZD is employed to clamp the voltage during the DUT off-state, and D2 is used to prevent discharge of the Zener diode junction capacitance. However, this measurement circuit cannot be used under high frequency conditions due to the frequency limitation of the zener diode ZD.

In [41], S. Beczkowski presented an IGBT on-state voltage measurement circuit (OVMC). However, it cannot work well especially during IGBT switching transients. Firstly, the bias current IBias is generated by a voltage regulator. During the IGBT off-state, the DC voltage is blocked by D1 and D2 equally. Hence, the input voltage of the amplifier exceeds its power supply voltage which destroys the amplifier. Second, during the IGBT off-state, the output of the voltage regulator induces invalid measurement data, which reduces the resolution of the measurement circuit.

To measure the on-state voltage of IGBT modules simultaneously and accurately, a clamp diode-based voltage measurement circuit is proposed as shown in Fig. 12 and Fig. 13.

D1, D2 and D3 are fast recovery diodes (MA4P7470F-1072 T) with an 800 V blocking voltage. D1 and D2 are used to block the DC link voltage. To eliminate the measurement error, D2 (which is the same as D1) is set in series with D1 and the output of amplifier OPA320 can be described as (8). The anti-parallel diode D3 is set to eliminate the reverse voltage of D2 to protect the amplifier. A 3-Terminal adjustable voltage regulator LM317 is chosen to generate the bias current for D1 and D2. A signal MOSFET CSD16413Q5A is adopt to filter invalid measurement data during the DUT off-state and to provide a discharge loop for IBias.

To validate the accuracy of the proposed on-state voltage measurement circuit, a single-pulse test platform was built as shown in Fig. 14. DUT S1 is in the conducting state, while S2 is driven by a single pulse. During the off-state of S2, the DC link voltage is blocked only by S2, and the voltage across S1 is almost 0. Hence, the on-state voltage of the DUT can be directly detected by an oscilloscope and the results are depicted in Fig. 15.

Apart from measurement accuracy, another indicator that needs to be concentrated on is the response time of the measurement circuit. As shown in Fig. 16, due to a rise of the gate voltage, the IGBT module is operated from its linear region to its saturation region. Consequently, there exists a voltage overshoot at the beginning of the measurement circuit operation, and it can be restrained by increasing the value of the driver resistance of S1. The results are illustrated in Fig. 17.

The response time can be defined as the delay time between the effective input and output of the measurement circuit. At the moment t1, the gate voltage rises to its positive steady-state value. Because the voltage overshoot occurred in the turn-on transient, the on-state voltage measured by the proposed method is not stable until t2. Hence, the response time can be described as the time interval between t1 and t2. When compared to the switching period under PWM modulation, the on-state voltage measurement circuit has a fast response speed.

4 Offline verification using V ce under a low current density

Thanks to good linearity and temperature sensitivity, the on-state voltage under a low collector current density Vce(LC) is recommended for an IGBT module thermal impedance test by the Electronic Industries Association (EIA) and Joint Electron Device Engineering Council (JEDEC). To verify the accuracy of the presented method, the junction temperatures monitored by measuring the on-state voltage under a low current density Vce(LC) and a high current density Vce(HC) are compared and analyzed.

4.1 Calibration implementation

Before using a TSEP, it is necessary to make a preliminary calibration to find the relationship between the TSEP and the junction temperature. The on-state voltage under a low current density Vce(LC) is related to the gate voltage, collector current and junction temperature. For a GD400FFT65P3H IGBT module, the Vce(LC) values with different junction temperatures are illustrated as Fig. 18. The gate voltage and injection collector current are 15 V and 145 mA, respectively.

Similarly, the on-state voltage under a high current density Vce(HC) is a function of the gate voltage, collector current and junction temperature. The calibration circuit for Vce(HC) is shown as Fig. 19. To avoid the measurement error caused by the chip self-heating effect, a single pulse generated by a pulse generator based on a Schmitt trigger and a 555 Timer within 10 μs is used to drive the DUT. The Vce(HC) with different collector currents are shown in Fig. 20. The gate voltage is chosen as 15 V, which is the same as the value used in the Vce(LC) calibration experiment.

4.2 Experimental verification

To verify the measurement accuracy of the presented method, the junction temperature monitoring results using Vce(HC) and Vce(LC) are compared, and the test circuit is illustrated in Fig. 21. First, a constant heating current IH is applied to the DUT to heat up the device until the thermal steady state is reached. Since the DUT is in contact with the heat sink, the heating time can be selected at around 100 s in most cases.

When the thermal steady state is reached, a 145 mA measurement current IM is injected into the device while the heating current IH is cut off. By a comparison of the junction temperature extraction results under high and low collector current densities, the accuracy of the proposed method can be validated. When compared to the heating current, the value of the measurement current is small and the power losses caused by this current can be neglected. The higher the power step between the heating and measurement processes, the higher the signal to noise ratio of the measurement and the more accurately the junction temperature can be monitored.

More importantly, electrical disturbances occur at the moment the heating current is cut off, which renders the signal insignificant for the beginning time. To eliminate the effect caused by electrical disturbances, an offset correction process is required.

For a homogeneous semi-infinite plate, when the heating power density of the material surface is a constant, the temperature rise of the plate is a linear function with the square root of the heating time during the cutting off transient as shown in (9) and (10).

where c, ρ and λ are the thermal capacity, density and thermal conductivity of the material, respectively. In addition, ktherm is a constant for a certain material. Hence, for a given heating power density, electrical disturbances can be eliminated by reversely extending the temperature rise curve to the cut off moment under the coordinate of the square root time, as depicted in Fig. 22. The on-state voltage under high and low collector currents is measured and the offline junction temperature monitoring results after offset correction are listed in Table 3.

5 Online temperature monitoring during converter operation

In this section, the proposed junction temperature monitoring method is applied to a three-phase voltage source converter. The DUT is chosen as a GD400FFT650P3H IGBT module from Starpower, and it is modulated by the closed-loop space vector pulse width modulation (SVPWM) strategy with a 5 kHz switching frequency. A three-phase water cooling R–L load is used as shown in Fig. 23.

Figure 24 shows experimental waveforms during the junction temperature monitoring circuit operation. The voltage measurement circuit obtains the on-state voltage and blocks the DC link voltage. The phase current is measured as the DUT collector current Ic during a transient in which the phase current is positive. When the phase current is negative, the anti-parallel diode of the DUT is conducting and the output of the on-state measurement circuit is 0.

To demonstrate the proposed IGBT junction temperature monitoring method, the on-state voltage is measured under 200A and 250A with a 15.4 V gate voltage. The obtained results are shown in Figs. 25 and 26, respectively.

The high-frequency noises in these waveforms are filtered by a digital filter. Due to the mutual inductances in each of the phases, there exists a tiny voltage overshoot in on-state voltage circuit output during current conversion transients. Hence, the sampling point is set in the middle of two current conversions to avoid measurement errors. The on-state voltage under 200A and 250A with a 15.4 V gate driver voltage indicates junction temperatures of 87.5 ℃ and 103.7 ℃ according to the calibration results.

To verify the junction temperature monitoring results, simulations are implemented in the finite element analysis (FEA) simulation tool. The geometry structure of the proposed IGBT module is created by SolidWorks, and the thermal simulations are generated by ANSYS Icepak. The effective values of the chips heating power dissipations are calculated by the integrating on-state voltage drop and conducting current. For each of the IGBT chips, heating power dissipations under 200A and 250A are 22.22 W and 30.55 W, respectively. Similarly, the dissipations are 19.83 W and 26.66 W for each of the diode chips. The obtained simulation results are illustrated in Figs. 27 and 28. The results under 200A (89.6703 ℃ and 89.5045 ℃) and 250A (112.794 ℃ and 112.928 ℃) agree well with the measurement results, which verifies the effectiveness of the proposed method.

6 Conclusion

This paper proposes an online junction temperature monitoring method based on Vce(HC) measurement for an IGBT power module. By calculating the on-state voltage with different collector current densities, the method is shown to be feasible. To accurately extract on-state voltage during operation, a measurement circuit that combines the advantages of both active MOSFET clamps and diode clamps is designed and tested with an acceptable measurement error and a few microseconds response time. The present method is verified by the JEDEC-51 standard recommended approach and applied to a three-phase voltage source converter controlled by the closed-loop SVPWM modulation strategy. In addition, an Icepak-based thermal simulation is implemented and the obtained results match well with the experimental results. In addition, the IGBT degradation model will be added to the calibration model for more accurate junction temperature measurement in future research.

Abbreviations

- \(C_{{{\rm OX}}}\) :

-

Oxide capacitance (nF)

- \(D_{{\text{a}}}\) :

-

Ambipolar diffusivity (cm2 /s)

- \(J_{{\text{C}}}\) :

-

Collector current density (A/cm2)

- \({\text{k}}\) :

-

Boltzmann constant (J/K)

- \(K_{{\rm T}}\) :

-

Threshold voltage temperature coefficient (V/K)

- \(L_{a}\) :

-

Ambipolar diffusivity length (μm)

- \(L_{{{\rm CH}}}\) :

-

Channel length (μm)

- \({\text{n}}_{{\text{i}}}\) :

-

Intrinsic carrier concentration (cm−3)

- \(p_{{}}\) :

-

Cell pitch (μm)

- \(q\) :

-

Unit charge (c)

- \(S\) :

-

Relative thermal sensitivity factor (%/℃).

- \(T\) :

-

Temperature (K)

- \(T_{{0}}\) :

-

Room temperature (K)

- \({\text{t}}_{{{{\rm d}\_{\rm off}}}}\) :

-

Turn-off delay time (ns)

- \(\mu_{{{\rm ni}}}\) :

-

Channel mobility (cm/s)

- \(V_{{{\rm ce(LC)}}}\) :

-

On-state voltage under a low current (mV)

- \(V_{{{\rm ce(HC)}}}\) :

-

On-state voltage under a high current (mV)

- \({\text{V}}_{{\rm G}}\) :

-

Gate–emitter voltage (V)

- \({\text{V}}_{{{\rm TH}}}\) :

-

Threshold voltage of an elemental MOSFET (V)

- \({\text{V}}_{{{\rm TH0}}}\) :

-

Threshold voltage at room temperature (V)

- \(W_{{\rm N}}\) :

-

Drift region width of an IGBT (um)

References

Yang, X., Lin, Z., Ding, J., Long, Z.: Lifetime prediction of IGBT modules in suspension choppers of medium/low-speed maglev train using an energy-based approach. IEEE Trans. Power Electron. 34(1), 738–747 (2019)

Senturk. O. S., Nielsn. S. M., Teodorescu. R., Helle. L., Rodriguez. P.: Electro-thermal modeling for junction temperature cycling-based lifetime prediction of a press-pack IGBT 3L-NPC-VSC applied to large wind turbines. In Proc. IEEE Energy Conversion Congress and Exposition, 17–22 (2011)

Zhang. Y., Wang. H., Wang. Z., Yang. Y., Blaabjerg. F.: Impact of lifetime model selections on the reliability prediction of IGBT modules in modular multilevel converters. In Proc. IEEE Energy Conversion Congress and Exposition, 1–5 (2017)

Slawinski. M, Sahan. B., Jansen. U.: Evaluation of a NPC1 phase leg built from three standard IGBT modules for 1500 VDC photovoltaic central inverters up to 800 kVA. In Proc. IEEE Energy Con-version Congress and Exposition, 5–9 (2016)

Mehrotra. V., He. H., Dadkhah. M. S., Rugg. K., Shaw. M. C.: Wirebond reliability in IGBT-power modules: application of high resolution strain and temperature mapping. In Proc. IEEE Power Electronics Specialists Conference, 23–27 (2016)

Murdock, D., Torres, J., Connors, J., Lorenz, R.D.: Active thermal control of power electronic modules. IEEE Trans. Ind. Appl. 42(2), 552–558 (2006)

Weckert. M., Roth-Stielow. J.: Lifetime as a control variable in power electronic systems. In Proc. Emobility - Electrical Power Train, 1–6 (2010)

Marwali, M.N., Jung, J.W., Keyhani, A.: Control of distributed generation systems—part II: load sharing control. IEEE Trans. Power Electron. 19(6), 1551–1561 (2004)

Ma, K., Liserre, M., Blaabjerg, F.: Reactive power influence on the thermal cycling of MW wind power inverter. IEEE Trans. Ind. Appl. 49(2), 922–930 (2013)

Ma. K., Liserre. M., Blaabjerg. F.: Reactive power control methods for improved reliability of wind power inverters under wind speed variations. In Proc. IEEE Energy Conversion Congress and Exposition, 3105–3112 (2012)

Wu. T., Castellazzi. A: A. Temperature adaptive IGBT gate-driver design. In Proc. European Conference Power Electronics Applications, 1–6 (2011)

JeHwan. L., HanGuean. H., SangChul. S., Kiyoung. J., JinHwan. J.: Over temperature protection in power module for hybrid and electric vehicle. In Proc. Transportation Electrification Conference and Expo, Asia-Pacific, 432–435 (2011)

Ning, P., Yuan, T., Kang, Y., Cao, H., Li, L.: Review of Si IGBT and SiC MOSFET based on hybrid switch. Chin J Electr Eng 5(3), 20–29 (2019)

Jiang, D., Ning, P., Lai, R., Fang, Z., Wang, F.: Modular design method for motor drives. Chin. J. Electr. Eng. 4(1), 1–10 (2018)

Jiang, F., Li, Y., Tu, C., Guo, Q., Li, H.: A review of series voltage source converter with fault current limiting function. Chin J Electr Eng 4(1), 36–44 (2018)

Danković, D., Mitrović, N., Prijić, Z., Stojadinović, N.D.: Modeling of NBTS effects in P-channel power VDMOSFETs. IEEE T Device Mat Re. 20(1), 204–213 (2020)

Mahapatra, S., Parihar, N.: Modeling of NBTI Using BAT framework: DC–AC stress-recovery kinetics, material, and process dependence. IEEE T Device Mat Re. 20(1), 4–23 (2020)

Danković, D., Manic, I., Davidović, V., Djorić-Veljković, S., Golubović, S., Stojadinović, N.: Negative bias temperature instability in n-channel power VDMOSFETs. Microelectron Reliab. 48(8), 1313–1317 (2008)

Baker, N., Liserre, M., Dupont, L., Avenas, Y.: Improved reliability of power modules: a re-view of online junction temperature measurement methods. IEEE Ind. Electron. M. 8(3), 17–27 (2014)

Yang, S., Bryant, A., Mawby, P., Xiang, D., Ran, L., Tavner, P.: An Industry-based survey of reliability in power electronic converters. IEEE T Ind. Appl. 47(3), 1441–1451 (2011)

Sintamarean. C., Blaabjerg. F., Wang. H.: A novel electro-thermal model for wide bandgap semi-conductor based devices. In Proc. European Conference on Power Electronics and Applications (EPE), 1–10 (2013)

Chen. H., Ji. B., Pickert. V., Cao. W.: Real-Time Temperature estimation for power MOSFETs considering thermal aging effects. In IEEE T Device Mat Re. 14(1), 220–228 (2014)

Motto. E. R., Donlon. J. F.: IGBT module with user accessible on-chip current and tempera-ture sensors. In Proc. Annual IEEE Applied Power Electronics Conference and Exposition, 176–181(2012)

Zhang, Z., Dyer, J., Wu, X., Wang, F., Costinett, D., Tolbert, L.M., Blalock, B.J.: Online junction temperature monitoring using intelligent gate drive for SiC power devices. IEEE Trans. Power Electron. 34(8), 7922–7932 (2018)

Chen. H., Pickert. V., Atkinson. D. J, Pritchard. L. S.: On-line monitoring of the MOSFET device junction temperature by computation of the threshold voltage. In Proc. IET International Conference on Power Electronics, Machines and Drives, 440–444 (2006)

Xu, Z., Xu, F., Wang, F.: Junction temperature measurement of igbts using short-circuit current as a temperature-sensitive electrical parameter for converter prototype evaluation. IEEE Trans. Ind. Appl. 62(6), 3419–3429 (2014)

Bergogne. D., Allard. H., Morel. H.: An estimation method of the channel temperature of power MOS devices. In Proc. IEEE 31st annual power electronics specialists conference, 1594–1599 (2000)

Zhu, Y., Ma, K., Cai, X.: Thermal characterization method of power semiconductors based on H-bridge testing circuit. IEEE Trans. Power Electron. 34(9), 8268–8273 (2019)

Avenas, Y., Dupont, L., Khatir, Z.: Temperature measurement of power semiconductor de-vices by thermo-sensitive electrical parameters—a review. IEEE Trans. Power Electron. 27(6), 3081–3092 (2012)

Cao. H., Ning. P., Yuan. T., Wen. X.: Online monitoring of IGBT junction temperature based on Vce measurement. In Proc. International Conference on Electrical Machines and Systems, 11–14 (2019)

Dupont. L., Avenas. Y.: Evaluation of thermo-sensitive electrical parameters based on the forward voltage for on-line chip temperature measurements of IGBT devices. In Proc. IEEE Energy Conversion Congress and Exposition, 4028–4035 (2014)

Alonso. L., Brandelero. J., Ewanchuk. J., Mollov. S.: Indirect on-state voltage estimation using a voltage sensitive electrical parameter through the gate driver. In Proc. International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 1085–1090 (2019)

Frankeser. S., Hiller. S., Wachsmuth. G., Lutz. J.: Using the on-state-Vbesat-voltage for temperature estimation of SiC-BJTs during normal operation. In Proc. International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 132–139(2015)

Cao. H, Ning. P., Wen. X., Yuan. T., Li. H. (2020): An Electrothermal model for IGBT based on finite differential method. IEEE J. Em. Sel. Top P 8(1):673–684

Cao, H., Ning, P., Wen, X., Yuan, T.: Practical SPICE model for IGBT and PiN diode based on finite differential method. J Power Electron. 19(6), 1591–1600 (2019)

Baliga. B. J.: Fundamentals of power semiconductor devices. Chap. 9. Springer (2008)

Guacci, M., Bortis, D., Kolar, J.: On-state voltage measurement of fast switching power semiconductors. CPSS Trans Power Electron Appl 3(2), 163–176 (2018)

Carsten. B.: clipping pre-amplifier for accurate scope measurement of high voltage switching transistor and diode conduction voltages. In Proc. International Power Conversion Electronics conference and Exhibit, 335–342 (1995)

Wagenitz. D., Laeuschner. C., Thewes. R., Dieckerhoff. S.: Design and evaluation of a sensor for measuring the IGBT on-state saturation voltage. In Proc. International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 835–839 (2015)

Bęczkowski. S., Ghimre. P., Ruiz de Vega. A., Munk-Nielsen. S., Rannestad. B., Thøgersen. P.: Online Vce measurement method for wear-out monitoring of high power IGBT modules. In Proc. 2013 15th European Conference on Power Electronics and Applications (EPE), 2–6 (2013)

Acknowledgements

This work is supported by The National key research and development program of China (2016YFB0100600), the Key Program of Bureau of Frontier Sciences and Education, Chinese Academy of Sciences (QYZDBSSW-JSC044).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Cao, H., Ning, P., Chai, X. et al. Online monitoring of IGBT junction temperature based on Vce measurement. J. Power Electron. 21, 451–463 (2021). https://doi.org/10.1007/s43236-020-00178-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s43236-020-00178-5