Abstract

The system-on-chip (SoC) is an integration of millions of electronic components, there is always a chance for faults to occur due to manufacturing defects. In order to solve this problem, it is essential to test the manufactured chips. The time spent on testing increases the testing cost which reflects on the cost of the chip. While testing the SoC, core accessibility and testing time are the main issues to be considered. In order to reduce the testing time, test scheduling has to be performed in an effective manner. In this article ACO, Modified ACO, ABC, Modified ABC, Firefly and Modified Firefly test scheduling algorithms were tested on two SoC benchmark circuits. Experimental results show that the Modified ABC algorithm performs better than the other algorithms used in test scheduling. When compared with ACO, Modified ACO, ABC, Firefly and Modified Firefly algorithms, the Modified ABC algorithm’s testing time has been reduced by 82%, 69%, 25%, 43% and 48% for d695 SoC and 80%, 73%, 20%, 41% and 47% for p22810 SoC benchmark circuits respectively.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

1 Introduction

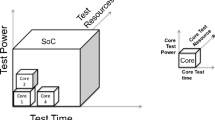

Semiconductor integrated circuits (ICs) are the basis of electronic products in the modern world. ICs are embedded in most of the systems and products. Several ICs introduced consequent to the growth in semiconductor technology are called system-on-chip (SoC). The SoC is an integration of IC that contains many transistors. The main issue in SoC testing is the IC complexity. To solve this issue the reusable core IC needs to be designed and verified. The cores may be manufactured internally or bought externally. System integrator brings these cores into the system. When the system becomes more complicated, faults need to be tested. This complication also increases the test cost. Test access mechanism (TAM) is employed to test cores individually [1, 2].

The SoC test model is used to test individual cores and inter connections. In the SoC model, the major components are a wrapper, TAM and test scheduling. The thin shell encircling the core called wrapper acts as an interface between the core and TAM. Test vectors are provided through TAM wires to the wrapper [3]. Automatic test equipment (ATE) stores the test vectors and through TAM wires, vectors are provided to the SoC. Interconnection is tested in external mode and the core is tested in internal mode. There are three modes in which testing of the SoC is done. They are bypass, soft and lower power modes. Scheduling of test is classified as partitioned, non-partitioned and pre-emptive testing. While cores are tested, the obtained response is compared with the expected response and the difference indicates the error. During the testing of interconnects, test stimuli are generated and the response is observed. All the cores need to be tested [4, 5]. The benchmark circuits d695 and p22810 are considered and the various algorithms are used for the benchmark circuits. The result is shown with regard to the test time which determines the test cost. The Modified Firefly Algorithm minimizes the test price by minimizing the total test application time. Hence, it is a better optimization technique than the other proposed algorithms.

An objective function is used to attain the tuning parameters of the system model to test under different load settings of d695 and p22810 SoC benchmark circuit. The purpose of algorithm for optimization is to reduce the test time which is the objective function stated in the following Eq. (1).

where Si and So represent the input and the output scan chain lengths and tpi represents the test pattern for core i of the benchmark circuit for optimization.

2 Literature review

Earlier works mainly focused on optimization of the TAM and wrapper design for reducing the test time for core-based systems [6] [7]. The three scheduling techniques are partitioned, non-partitioned, and preemptive techniques. All the cores must be completed at the end of the testing. Internal testing and external testing, Built in self test (BIST) and ATE are used. The SoC testing problem consists of core wrapper design, test scheduling and test access mechanism design. The test shell acts as an interface between the core and the host containing three types of I/O terminals, namely function I/O, test rail I/O, and direct test I/O. In the test wrapper approach, the bypass feature is not allowed which means only one core is served at a time [8, 9]. For 2-D bin packing problem, Simulated Annealing Algorithm minimizes the testing time [10].

In non-partitioned test scheduling until all the tests in a section are completed no new test can be started which increases the test time. In the partitioned technique, the test time is reduced by allowing the test to be scheduled as soon as possible. Pre-emptive test scheduling minimizes idle time. In order to reduce the testing time of the core-based systems earlier works mainly focused on efficient wrapper design and TAM optimization design. Wrapper design and the related algorithm are based on access requirements of core terminals like functional access.

In open shop scheduling, the shop consists of m processors, J jobs each with m tasks of length ≥ 0. For each task, no job is processed on more than a single processor. The objective of open shop scheduling is the reduction of finish time of individual processor schedules. Simulated annealing (SA) Algorithm was used to resolve the bin packing problem of two dimensions by minimizing the TAT. The wrapper design method was used to generate a sequence of rectangles using Genetic Algorithm formulation. From the set of rectangles generated for the core one rectangle has to be selected to reduce total testing time [11].

In hierarchy aware test planning method used for the optimization of TAM, the issue of hierarchical SoCs is addressed. Two practical scenarios emerge: (1) For the child cores TAM architecture and Wrappers are fixed (hard) and for a parent, cores are determined (soft). (2) TAM and Wrappers for both the parent and the child cores are soft. A multilevel TAM architecture is proposed which describes the use of flattened SoCs for multilevel TAM optimization. The new wrapper architecture having two disjoint test modes for testing parent cores and child cores is proposed. particle swarm optimization (PSO) is an optimization algorithm dependent on the flocking behavior of the bird developed by Kennedy [12]. Real ant behavior leads to Ant Colony Optimization depending on the mechanism followed by an ant in search of the shortest route for food.

3 Proposed work

3.1 Ant colony optimization

Ant colony optimization (ACO) is [13, 14], an approach based on ant population to solve computational problems. This is based on the social nature of ants for identifying the best route to the food source from the nest by indirect communication among ants using Pheromone, a chemical.

It is a metaheuristic optimization technique. Ants leave pheromone behind while moving so that the other ants smell this pheromone and follow it. In ACO artificial ants develop newer solutions using the mixture of heuristic information and artificial pheromone trail. ACO has been shown to be efficient in solving many problems.

3.2 Modified ant colony optimization

In the existing techniques even if the number of cores increases, ants’ count will remain constant. On each iteration, for the same ants’ count when the number of test cores decreases, the testing time increases which leads to inefficient output. This problem is solved in a modified ACO [15,16,17] technique. In the proposed work, whenever the number of cores decreases, ants’ count will also get reduced. This leads to a reduction in the testing time of the system. Hence more efficient output can be obtained.

3.3 Artificial bee colony (ABC) algorithm

A meta-heuristic technique based on honey bee intelligent behavior to solve numerical problems is called Artificial bee colony algorithm [18,19,20]. The steps involved in the ABC algorithm is shown as a flowchart in Fig. 1.

3.4 Modified artificial bee colony algorithm

For ABC technique among common control parameters like population size, only one control parameter is used. But when the ABC technique is used for a composite function, the convergence rate is poor. In this process perturbation frequency is a parameter that affects new solutions. The ABC technique can be modified by controlling the perturbation frequency. This is referred to as the modified artificial bee colony (MABC) algorithm [21,22,23]. In general, ABC algorithm frequency is constant. When a newer solution is produced through only one parameter of parent solution, the issue can be overcome by MABC algorithm. The modification is done by adding a control parameter additionally.

By this modification, for every parameter Xij, a random number is generated and if it is lower than the modification rate, random variable Xij is modified. Another change in the ABC algorithm is dependent on the variance operator ratio. In ABC, the current solution is added with random perturbation at local minima to obtain a new solution. This magnitude of perturbation is controlled by the scaling factor of the new control parameter.

Step 1 | Randomly generate food sources Si. |

Step 2 | Food sources are assigned to the employed bee. For every food source fitness value f (Si) is evaluated. |

Step 3 | Initialize M = 0 and L1 = 0, L2 = 0 … LN = 0 |

M = Number of times of repeating an entire foraging process. | |

Li = Number of times of applying a neighbor operator to food source ‘i’ where i = 1… N. | |

Step 4 | Repeat foraging process |

For Employed Bee Phase | |

Each food source is employed by a neighborhood operator: Si → S. | |

If f (S) > f (Si), Si is replaced by S and Li = 0. Or else Li = Li + 1. | |

For Onlooker Bee Phase | |

Based on fitness values onlooker bee selects a source of food by means of the roulette wheel selection method. | |

If f (S) > f (Si), select Sj where Lj is the maximum of all food sources. | |

If f (S) > f (Sj), Sj is replaced by S and Lj = 0. Otherwise Li = Li + 1. | |

For Scout Bee Phase | |

If Li = Limit for each food source, applied by a neighborhood operator: Si is replaced by S. Where M = M + 1. | |

Step 5 | Stop the foraging process where M reaches Maximum Cycle. |

3.5 Firefly algorithm

A metaheuristic technique based on the flashing behavior of the firefly was proposed by Yang and came to be called Firefly Algorithm [24, 25]. This works on the attractiveness between the fireflies while the mating process is based on the firefly brightness. Figure 2 demonstrates the Firefly Algorithm flowchart giving the steps in which it proceeds.

3.6 Modified firefly algorithm

The Modified Firefly Algorithm [26,27,28] overcomes the problem of the Firefly Algorithm. It reduces the randomness of the technique and enhances the movement of Fireflies. Figure 3 illustrates the flowchart of Modified Firefly Algorithm and the steps by which it proceeds. In modified firefly Algorithm, randomization parameter α varies between \(\alpha_{0}\) and \(\alpha_{\infty }\), where \(\alpha_{0}\) and \(\alpha_{\infty }\) are initial and final values during iteration. Exploitation and exploration abilities are kept under balance. If \(\alpha\) is larger, the convergence will be better. Distance function \(r_{i}\) and movement of ith firefly are shown by the Eqs. (2) and (3).

where \(\varepsilon = rand\,-\,{\raise0.7ex\hbox{${1}$} \!\mathord{\left/ {\vphantom {{ - 1} 2}}\right.\kern-0pt} \!\lower0.7ex\hbox{$2$}}\), gbest = global best. If any local best solution does not occur in the neighborhood, ith firefly gets attracted to the best solution. Modified Firefly Algorithm reduces the randomness to minimize the probability into local optima. Hence convergence is achieved quickly and fireflies move to global optima.

Figure 3 gives the flowchart of Modified Firefly Algorithm, giving the steps by which it proceeds.

4 Results and discussion

The results are presented for two international test conference (ITC’02) benchmark circuits d695 and p22810.

4.1 d695 SoC Benchmark

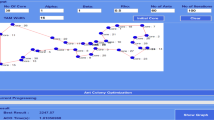

Figures 4, 5, 6, 7 and 8 show the initialization of cores for d695 SoC benchmark circuit using Ant Colony, Modified Ant Colony Algorithm, Artificial Bee Colony Algorithm, Modified Artificial Bee Colony Algorithm and Firefly Algorithm respectively. Numerous iteration parameters are taken as input. The testing time and best result point are computed.

It can be understood from Fig. 4 that the parameters alpha, beta and rho are started by the value 1, 1 and 0.5 respectively. The best result point is found as 1426.35 and the testing time is achieved as 0.120265. Similarly, for other algorithms the best result point and testing time are calculated by considering various input parameters.

4.2 p22810 SoC Benchmark

Figures 9,10,11,12 and 13 show the initialization of cores for p22810 SoC benchmark circuit using ACO, Modified ACO, ABC, Modified ABC and Firefly algorithms respectively. Numerous iteration parameters are taken as input. The testing time and the best result point are computed.

Tables 1 and 2 show the comparison of testing time obtained from ACO, Modified ACO, ABC, Modified ABC, Firefly and Modified Firefly algorithms for d695 and p22810 SoC benchmark circuits. It can be easily inferred that the Modified ABC Algorithm gives optimal test time when compared with the other proposed algorithms.

Figures 14 and 15 show the test time comparison for several algorithms proposed in a graphical format for d695 and p22810 benchmark circuits. The obtained graph explains that the various proposed algorithms show a specific quantity of reduction in the testing time compared with the ACO algorithm.

5 Conclusion and future work

In this paper, the optimization of SoC has been performed by reducing the testing time using various algorithms for d695 and p22810 benchmark circuits. The various TAM widths have been taken into consideration. The final obtained result has shown that the Modified ABC Algorithm is more efficient in reducing the test time for SoC benchmarks. When compared with ACO, MACO, ABC, Firefly and Modified Firefly Algorithms the testing time of Modified ABC Algorithm has been reduced to 82%, 69%, 25%, 43% and 48% for d695 SoC and 80%, 73%, 20%, 41% and 47% for p22810 SoC benchmark circuit respectively. Hence the objective of reducing the testing cost is achieved by minimizing the SoC testing time using the proposed algorithm.

In future, this work can be extended to mixed-signal VLSI chips contains digital circuits, and analog circuits. As more complex, mixed signal SoC designs continue to stress on verification methodologies and schedules, designers need new approaches for solving today’s test challenges.

References

Iyengar V, Chakrabarty K, Marinissen EJ (2003) Efficient test access mechanism optimization for system-on-chip. IEEE Trans Comput Aided Des Integr Circuits Syst 22(5):635–643. https://doi.org/10.1109/TCAD.2003.810737

Larsson E, Fujiwara H (2006) System-on-chip test scheduling with reconfigurable core wrappers. IEEE Trans VLSI Syst 14(3):305–309

Koranne S (2003) Design of reconfigurable access wrappers for embedded core based SoC test. IEEE Trans VLSI Syst 11(5):955–960

Larsson E, Peng Z, Chakrabarty K (2002) An integrated framework for the design and optimization of SOC test solutions. J Electron Test 21:21–36. https://doi.org/10.1007/978-1-4757-6527-4_2

Marrouche W, Farah R, Harmanani HM (2018) A strength pareto evolutionary algorithm for optimizing system-on-chip test schedules. Int J Comput Int Syst 17(02):1850010

Iyengar V, Chakrabarty K, Marinissen EJ (2002) Test wrapper and test access mechanism co-optimization for system-on-chip. J Electron Test 18(2):213–230

Başak ME, Kuntman A, Kuntman HH (2014) MOSFET Spice parameter extraction by modified genetic algorithm. Inf MIDEM 44(2):142–151

Novak F (2001) Testability issues of system-on-chip design. Inf MIDEM 2:84–87

Iyengar V, Chakrabarty K (2002) System-on-a-chip test scheduling with precedence relationships, preemption, and power constraints. IEEE Trans Comput Aided Des Integr Circuits Syst 21(9):1088–1094. https://doi.org/10.1109/TCAD.2002.801102

Olenšek J, Puhan J, Bűrmen Á, Tomažič S, Tuma T (2006) Optimization of integrated circuits by means of simulated annealing. Informacije MIDEM 36:79–84. http://www.midem-drustvo.si/Journal%20papers/MIDEM_36(2006)2p79.pdf

Srinivas N, Deb K (1994) Muiltiobjective optimization using nondominated sorting in genetic algorithms. Evol Comput 2(3):221–248

Kennedy J (2010) Particle swarm optimization. Encyclopedia of machine learning. Springer, Heidelberg, pp 760–766

Mahi M, Baykan ÖK, Kodaz H (2015) A new hybrid method based on particle swarm optimization, ant colony optimization and 3-opt algorithms for traveling salesman problem. Appl Soft Comput 30:484–490

Dorigo M, Maniezzo V, Colorni A (1996) Ant system: optimization by a colony of cooperating agents. IEEE Trans Syst Man Cybern B 26(1):29–41

Wang Z, Xing H, Li T, Yang Y, Qu R, Pan Y (2015) A modified ant colony optimization algorithm for network coding resource minimization. IEEE Trans Evol Comput 20(3):325–342

Liu J, Yang J, Liu H, Tian X, Gao M (2017) An improved ant colony algorithm for robot path planning. Soft Comput 21(19):5829–5839

Vanchinathan K, Valluvan KR (2018) A metaheuristic optimization approach for tuning of fractional-order PID controller for speed control of sensorless BLDC motor. J Circuit Syst Comput 27(08):1850123

Basturk B (2006) An artificial bee colony (ABC) algorithm for numeric function optimization. IEEE Swarm Intell Symp, USA

Karaboğa N, Cetinkaya MB (2011) A novel and efficient algorithm for adaptive filtering: artificial bee colony algorithm. Turk J Electr Eng Comput 19(1):175–190

Xue Y, Jiang J, Zhao B, Ma T (2018) A self-adaptive artificial bee colony algorithm based on global best for global optimization. Soft Comput 22(9):2935–2952

Karaboga D, Gorkemli B, Ozturk C, Karaboga N (2014) A comprehensive survey: artificial bee colony (ABC) algorithm and applications. Artif Intell Rev 42(1):21–57

Gao W, Liu S, Huang L (2012) A global best artificial bee colony algorithm for global optimization. J Comput Appl Math 236(11):2741–2753

Liang Y, Wan Z, Fang D (2017) An improved artificial bee colony algorithm for solving constrained optimization problems. Int J Mach Learn Cybern 8(3):739–754

Yang XS, Hosseini SSS, Gandomi AH (2012) Firefly algorithm for solving non-convex economic dispatch problems with valve loading effect. Appl Soft Comput 12(3):1180–1186

Fister I, Fister I Jr, Yang XS, Brest J (2013) A comprehensive review of firefly algorithms. Swarm Evol Comput 13:34–46

Niknam T, Azizipanah-Abarghooee R, Roosta A (2012) Reserve constrained dynamic economic dispatch: a new fast self-adaptive modified firefly algorithm. IEEE Syst J 6(4):635–646

Kavousi-Fard A, Samet H, Marzbani F (2014) A new hybrid modified firefly algorithm and support vector regression model for accurate short term load forecasting. Expert Syst Appl 41(13):6047–6056

Wahid F, Alsaedi AKZ, Ghazali R (2019) Using improved firefly algorithm based on genetic algorithm crossover operator for solving optimization problems. J Intell Fuzzy Syst 36(2):1547–1562

Acknowledgements

The authors extend their sincere thanks to Centre for Research of Anna University for providing us a platform to take over our research work.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Chandrasekaran, G., Periyasamy, S. & Karthikeyan, P.R. Test scheduling for system on chip using modified firefly and modified ABC algorithms. SN Appl. Sci. 1, 1079 (2019). https://doi.org/10.1007/s42452-019-1116-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-019-1116-x