Abstract

This paper investigates the effect of using the adaptive body bias technique to minimize the negative consequences of the process variability and reliability issues in CMOS RF circuits. In recent years, ongoing downsizing in transistors’ aspect ratio led to process variation error and reliability concerns that, particularly for transistors, are threshold voltage increase and electron mobility drift. The studied optimization approach is based on combining the main low noise amplifier (LNA) circuit with an adaptive body bias circuit, and both are designed for ISM band 902–928 MHz. This technique is applied to a low-power, low-voltage, variable-gain, low noise amplifier to adjust the major effects of process variation, namely threshold voltage increment and electron mobility decrement. The amount of normalized variations in noise figure, small-signal gain (S21), and minimum noise figure parameters of the circuit are examined over a wide range of voltage gain. The post-layout simulation results in the 180 nm CMOS process show that with employing this technique and under 16% threshold voltage and mobility variation, NF is decreased by a factor close to 4.87 times and 2.27 times compared to the LNA with constant DC body bias, respectively. These results show the superior performance of the proposed approach. In addition to normalized results, the Monte− Carlo simulation results are also provided to ensure the effectiveness of the proposed circuit in the corners. In order to validate the circuit performance, mathematical calculations are provided, as well.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

Process variation is the deviation from designed values for a layout structure or circuit parameter [1]. Aggressive scaling in device dimensions to provide smaller feature sizes and improve speed and functionality in the past decades has received growing attention. However, entering the nanometer regime has resulted in numerous reliability issues due to the high electric field phenomenon [2]. These reliability degradation mechanisms lead to threshold voltage increase and electron mobility decrease. These phenomena cause the MOS transistor parameters to drift from the expected values [3, 4].

Technology development in recent years revolutionized the usage of electronic devices, especially devices with RF and wireless communications applications. Therefore, this vast utilization of electronic devices in everyday life caused abundant new applications ranging from medical to aerospace [5].

Consequently, these broad usage fields show the urgency of new considerations and tradeoffs in designing circuits. Meanwhile, designers focused more on developing high-reliability performance circuits alongside the lowering power budget and the size of the devices. Using wireless electronic devices in biomedical applications and medical devices that have direct contact with human tissues shows the critical role of having reliable devices as well as the priority of this field [6, 7].

As a very first block in the receiver chain of wireless communication systems, LNA is a bottleneck in defining some critical parameters of the receiver front-end specifications [8] especially in ultra-low power receiver topologies [9] in which the main focus is on achieving less hardware to reduce power consumption [10–. Due to tradeoffs between critical design parameters of LNA, like gain, noise figure (NF), and their tradeoffs with application parameters such as power consumption, the consideration in circuit design gets complicated and more sensitive [14, 15].

Many attempts have been devoted to improving the circuit’s immunity to various reliability and variability issues and addressing these issues [16,17,18,19,20,21,22,23]. In the earlier works [18], a body biasing method is used to reduce die-to-die threshold voltage variation. Also, in the investigations [19] and [20], adaptive body bias scheme is employed for power amplifiers and low noise amplifiers to reduce reliability issues and variability. In another work, the effect of hot carriers as one of the reliability degradation mechanisms on LNA performance is investigated [21]. In the literature [22], the variations in LNA, mixer, and voltage-controlled oscillator (VCO) that are implemented with heterojunction bipolar transistors (HBT) are investigated. In the researches [23], the performance drifts for main parameters of LNA under process variation are analyzed, and to partially compensate for these effects; a variable gain scheme is used.

This paper presents a low voltage variable gain LNA and a simple yet effective body biasing technique to mitigate the effect of variations in threshold voltage and mobility. The proposed scheme can work with the low supply voltage. Due to the tunable gain capability, the proposed LNA can operate in a wide range of input power and frequency variations.

Proposed Variable Gain LNA Structure

Proposed LNA with Variable Gain Mechanism

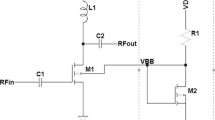

Figure 1 shows the proposed LNA circuit with adaptive body bias. The proposed LNA circuit is capable of providing variable gain through the cascade transistors by the 4-bit controlling signal that provides 15 levels of gain from module1 (0001) to module15 (1111) through disabling or enabling VC1 to VC4. So, there is a wide degree of freedom to change gain from the lowest value of 12.6 dB (mode1) to the highest value of 20.7 dB (mode15). The importance of having a variable gain LNA is due to the different power levels of the received signal in the antenna that forces the receiver gain to be adjustable. In other words, for an input signal with high power, the receiver gain should be small to avoid the receiver chain from saturation; on the other hand, for a small input signal, the gain should be large. All simulation results are given in two high gain and low gain modes.

Proposed Body Bias Scheme for Reliability and Variability

In general, the main focus in designing this LNA is to reduce the effects of the process variations in the circuit performance. Therefore, the technique followed in this paper is based on a body biasing scheme. The studied adaptive body bias scheme is presented in Fig. 2. The conventional body bias reference is shown in part (a) of Fig. 2. The proposed adaptive body bias reference is pictured in Fig. 2b, and the integration of a body bias circuit with an LNA block is depicted in Fig. 2c. However, the main LNA present in this paper is a variable gain scheme that will be investigated in the following section. The proposed adaptive body bias reference consists of a single transistor and two resistors Fig. 2b. The resistor R1 produces an appropriate voltage drop from VCC, while RB is a current-limiting resistor used to prevent signal leakage and noise coupling between VB and the body terminal of the LNA’s transistor [24]. This combination produces the voltage for biasing the body terminal of the proposed LNA’s input transistors. According to the CMOS regime, there exists a relationship between body terminal voltage and threshold voltage. As will be shown soon in Eq. 5, it seems that if the body voltage can be varied in corresponds to threshold voltage variations, it can create a compensation cycle. As mentioned before, reliability issues in the CMOS transistors indicate threshold voltage increase and electron mobility decrease.

a Conventional body bias [20] b Studied body bias c LNA with adaptive body bias

The overall flow of compensation mechanism for both the conventional and proposed body biasing circuits is as follows: Due to reliability issues that are out coming in the shape of Vth increment, the drain current (ID) is decreased; consequently, the resultant VB is increased. Increasing the body voltage of VB, in turn, decreases the threshold voltage of the body-biased input transistor, M1, due to the source body effect. Though, the whole structure configures a feedback scheme that senses the threshold voltage variation and then compensates it through feedback structure. The result is that the threshold voltage variation effects on circuit performance are mitigated [25].

As shown in Fig. 2a, the conventional adaptive body bias circuit [9] needs more voltage headroom compared to the studied circuit in Fig. 2b. Besides, the simulation results show that the circuit in Fig. 2a consumes more power than the circuit in Fig. 2b. Therefore, the studied circuit indicates boosted performance in addressing the reliability issues.

Analytical Support for Proposed Biasing Scheme

-

(1)

threshold voltage increment (fluctuation)

In this section, the threshold voltage variation in the circuit is examined, and the effect of using body bias to mitigate this variation is also formulated. As noted earlier, the defects in the reliability mechanism have two apparent effects on the circuit, increasing the threshold voltage and decreasing carrier mobility. From KVL in Fig. 2b, the following expression can be derived:

Moreover, for an NMOS in the saturation region, the following expression is valid:

where VCC is the value of supply voltage, Vthc is the threshold voltage, and \(\beta_{C} = \mu_{n} C_{OX} \left( \frac{W}{L} \right)_{C}\) is the device parameter. Substituting (2) in (1) gives the following equation for VB:

Equation 3 denotes that the value of VB varies by changing Vthc. Using (3), the deviation in VB due to the threshold voltage variations can be expressed as follows:

The threshold voltage of the CMOS transistors in terms of body terminal voltage is given by:

where Vth0 is threshold voltage with zero VSB, γb is body effect coefficient, and φf is Fermi potential. To examine the relationship between threshold voltage alternation and body voltage, the authors can derivate from (5) to get (6) as follows:

Substitute (5) into (6) gives an equation that demonstrates the relevance of changing the body bias of a transistor and the compensation cycle for threshold voltage:

Equation 7 indicates that an increase in threshold voltage of M1 (Vth0) is compensated due to Vthc, and using the body biasing scheme improves the circuit robustness against variation.

-

Mobility degradation

Another parameter that changes due to reliability issues is electron mobility. Degradation in mobility denotes with β parameter in the following equations. Using KVL in Fig. 2(b), Eq. 8 is derived:

In order to examine the fluctuation effect, the deviations of (8) are used as follows:

The electron mobility variations also cause the threshold voltage parameter to change, though the following equation can express the variation.

All of the above equations show how the compensation process is working in order to immune the circuit against process variations. The effect of total variation on the LNA’s current can be expressed as:

LNA Parameteric Analysis

In this section, the adaptive body bias circuit's effects on the major parameters of LNAs are calculated.

Noise Figure

Low noise amplifier is the first active block in almost every receiver chain, and the noise performance of this block is a dominant value in determining the noise figure of the whole receiver. This shows the importance of having a stable NF in LNA [26].

The most basic definition of noise figure came into widespread use in the 1940s when Harald Friis defined the noise figure (NF) of a two-port network to be the ratio of the signal-to-noise power ratio at the input to the signal-to-noise power ratio at the output.

Equation 14 expresses the noise factor defined in the two port network with noise sources and a noiseless circuit. The noise factor can be expressed as [20, 27]:

where \({i}_{s}\) is the noise current from the source, \({Y}_{s}\) is the source admittance, \({i}_{n}\) is the device noise current, \({e}_{n}\) is the device noise voltage, and \({Y}_{c}\) is the correlation admittance. The noise figure is the noise factor that reported the decibel.

Figure 3 shows the small-signal model of an NMOS transistor with noise sources for the studied adaptive body bias circuit at high frequency. Note that the flicker noise at high frequency is ignored. Two primary noise sources in NMOS are the thermal noise currents of drain and gate, which are formulated by the following equations.

where “k” is Boltzmann’s constant, “T” is the absolute temperature, \(\omega\) is the angular frequency, \({g}_{m1}\) is the transconductance of \({M}_{1}\), \({C}_{gs1}\) is the gate-source capacitance of \({M}_{1}\), \(\Delta f\) is the offset frequency, and \(\theta\) is the gate noise coefficient. For long-channel MOSFETs γ is equal to 2/3 in saturation and is equal to a unit in the triode region, yet for short-channel devices, its value can be larger. To calculate the noise factor and its behavior in process variations, first, the parameter in (14) is calculated. For the proposed body biasing circuit, there are two main sources of noise in the output (neglecting flicker noise). The drain noise current of \({M}_{B}\) and the noise current of drain resistor, \({R}_{1}\), as shown in Fig. 3, can be formalized as follows:

The total noise voltage in the output can be written as:

The reflected drain current noise in the body terminal of the input transistor is expressed by multiplying (19) in \({g}_{mb1}\) as follows:

Therefore, the total noise current in the drain of the input transistor (\({M}_{1}\)) consists of the noise in the body terminal and the noise in the drain. Though it can be written:

The input-referred-noise in the gate of the input transistor ( \({M}_{1}\)) can be expressed as:

The equivalent noise resistor is as (23):

The drain noise current does not solely indicate the drain noise; meanwhile, when there is no source in the circuit (open circuit condition) a noisy drain current also flows. Multiplication of equivalent input noise voltage by the input admittance gives the value of equivalent input noise current in open circuit condition [27].

The correlation between gate and drain noise is expressed by \({C}_{1}\) as follows [16]:

The total equivalent input noise current is the sum of the reflected drain noise and the induced gate noise current. The induced gate noise current itself consists of two main sections. \({i}_{ngc1}\) represents the correlated part of gate noise current with the drain noise current of M1, while the other section \({i}_{ngu1}\) is uncorrelated with the drain noise current. The correlation admittance is expressed as follows:

The gate-induced noise is again due to the thermal noise of channel but here the thermal noise is coupled capacitively to the gate and creates noise at the gate. This noise source is correlated with the channel thermal noise [28]

The correlation admittance can be rewritten as:

Using the definition of the correlation coefficient may express the induced gate noise as follows:

The uncorrelated portion of the gate noise is [27]:

The minimum noise factor can express as:

And:

In (32), the second and third terms cause a reduction in total noise factor sensitivity and compensate the effect of the variations.

Small Signal Gain

In RF circuits, S parameters are mostly used to examine the performance of the circuit. S21 is used to define the gain of two-port networks. According to equations in [20]

We examine the relevance between \({Y}_{21}\) and the transconductance alternation. For simplicity, the authors first calculated this accordance in an NMOS with no body bias, Fig. 4a.To calculate \({Y}_{21}\), the output node of the model should be tied to the ground as Fig. 4b.

Doing so, it was obtained Y21 as:

where \({V}_{1}\) refers to \({V}_{gs}\) in the input terminal (between G and S), and \({V}_{2}\) refers to \({V}_{gd}\) in the out terminal (between drain and source). To show the trans-conductance alternation effect on the \({Y}_{21}\) the following equation expressed:

Now, using the small signal model of NMOS with body terminal, Fig. 5a,

Writing KCL in body node gives:

From the above equation, the variation of \({Y}_{21}\) is a function of variation in \({g}_{m1}\) and \({g}_{mb}\) is as follows:

where

Simulation Results

The layout view of the proposed LNA structure is presented in Fig. 6. The circuit device values are summarized in Table 1. This section presents post-layout simulation results, and their agreement with mathematical analysis is confirmed. The proposed variable gain LNA is designed in TSMC 180 nm CMOS technology. The circuit operates with 0.9 V supply voltage and has a center frequency of 922 MHz. The proposed circuit consumes only 0.8 mW in its high gain mode. The effective transistors aspect ratio is tuned in a 4-bit system via enabling or disabling vc1 to vc4. Through this configuration, 15 levels of gain are available that can be varied from mode1 (0001) to mode15 (1111). So, there exist a wide variety of choices for tuning the LNA’s gain, from the lowest value of 12.6 dB (mode1) to the highest value of 20.7 dB (mode15).

In order to have a fair comparison and develop the limitations to a higher level between LNA with and without an adaptive body bias circuit, a constant DC bias is applied to the body terminal of the LNA circuit. The value of this DC bias is equal to the output voltage of the circuit shown in Fig. 2b. The bias voltage value is 103.4 Mv (Fig. 6).

Figure 7 shows the NF variations versus threshold voltage variation of the LNA in its high gain (Fig. 7a) and low gain (Fig. 7b) modes. For 16% normalized threshold voltage fluctuation, Fig. 7a illustrates that the normalized NF delicacy of the LNA for proposed, conventional, and DC constant bias circuits is 14.846%, 22.767%, and 72.2836%, respectively. Therefore, the sensitivity of the normalized NF of the proposed LNA decreases about 1.53 and 4.86 times compared to the conventional and DC-constant biased circuits, respectively. Similarly, for the lowest gain level of 12.6 dB, Fig. 7b shows that the normalized NF variation for the proposed circuit decreases about 1.75 and 4.55 times compared to the conventional and constant DC biased circuits, respectively.

The normalized NFmin variation versus threshold voltage variation is examined for the lowest gain and highest gain modes in Fig. 8a and b, respectively. These figures depict that the proposed LNA with adaptive body bias presents a lower NFmin variation compared to the conventional and DC-constant biased circuits. Another crucial parameter of LNAs is S21. Figure 9a shows the normalized S21 variation versus threshold voltage variation at the highest gain mode of the LNA, which is 23.26% for DC body-biased circuit, 8.2410% for the conventional and around 5.1% for the proposed circuit. In other words, the reduction rate compared to the DC scheme is 4.59 times compared to the conventional scheme is 1.62 times. The same analysis is conducted for S21 in the lowest gain mode. The results are shown in Fig. 9b. This figure demonstrates that the sensitivity of the normalized S21 variation for the proposed circuit is reduced 4.82 times compared to the DC body biased and 1.53 times compared to the conventional circuit.

Figures 10, 11, and 12 are pictured the NF, NFmin, and S21 parameters variations versus mobility fluctuation, respectively. As it can be noticed from these figures, the proposed circuit performance is better in all cases.

The net values of these three parameters (NF, S21, and S11) at frequency range of 700 to 1000 Mega Hertz are given in Figs. 13, 14 and 15, showing NF of 2.98 dB, the small-signal gain of 20.6 dB, and the S11 parameter better than -15 dB.respectively.

To give a better vision of the LNA performance, the variation rate reduction of NF, NFmin, and S21 for 16% variations is summarized in Table 2, for the whole studied cases. The comparative results with some other similar works are presented in Table 3.

In order to confirm the versatility improvement of the proposed adaptive body-biased LNA, the performance of three LNA circuits is investigated through Monte-Carlo analysis of their highest gain settings. The number of runs was 20. The results are shown in Fig. 16. It can be seen that the NF of the proposed structure has lower variation compared to the two other structures.

Conclusion

A low power variable gain LNA with low supply voltage and a simple body biasing circuit is presented, and its performance against process variations and aging effects is investigated. The simulation results show improved performance and robustness of the circuit. Utilizing body biasing in this architecture led to achieving high gain and low NF simultaneously while relaxed process variation and enhancing reliability. The performance of the proposed adaptive body-biased LNA with respect to reliability, threshold voltage, and electron mobility variations up to 16% is evaluated. The results are also compared with those of conventional body-biased structure and DC constant body-biased scheme, and compared to both situations; the proposed circuit indicates an improved performance. The post-layout simulation results in 180 nm CMOS indicate that for a 16% variation in threshold voltage and carrier mobility, the value of variations in both the highest gain mode and lowest gain mode is decreased considerably compared to the two other invested structures. By employing this technique and under 16% threshold voltage and mobility fluctuation, normalized NF is decreased by a factor close to 4.87 and 2.27 times compared to the structure with constant DC body bias, respectively, for high gain and low gain. The analytical equations of the proposed LNA are derived and verified by the post-layout and Monte-Carlo simulations.

References

M. Fakhfakh, H. Hsieh, L.H. Lu, Performance optimization techniques in analog. Mixed-Signal, Radio-Frequency Circuit Des. 5, 7 (2014)

C. Xin, “Radio frequency circuits for wireless receiver front-ends.” Texas A&M University, 2005.

J.-S.S. Yuan, S. Member, H. Tang, CMOS RF circuit design for reliability and variability (Springer, 2016)

S. S. Sapatnekar, “What happens when circuits grow old: Aging issues in CMOS design,” in 2013 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA), 2013, pp. 1–2.

D. Ho and S. Mirabbasi, “Low-voltage low-power low-noise amplifier for wireless sensor networks,” in 2006 Canadian Conference on Electrical and Computer Engineering, 2006, pp. 1494–1497

M. Zgaren, A. Moradi, L.F. Tanguay, M. Sawan, ISM-band 902- to 928-MHz FSK transceiver with scalable performance for medical devices. Int. J. Circuit Theory Appl. 46(12), 2266–2282 (2018)

M. Zgaren, M. Sawan, “A low-power dual-injection-locked RF receiver with FSK-to-OOK conversion for biomedical implants”,. IEEE Trans. Circuits Syst. I Regul. Pap. 62(11), 2748–2758 (2015)

A. Liscidini, M. Brandolini, D. Sanzogni, and R. Castello, “A 0.13 /spl mu/m CMOS front-end for DCS1800/UMTS/802.11b-g with multi-band positive feedback low noise amplifier,” in Digest of Technical Papers. 2005 Symposium on VLSI Circuits, 2005., 2005, pp. 406–409.

C.-J. Jeong, Y. Sun, S.-K. Han, S.-G. Lee, “A 2.2 mW, 40 dB automatic gain controllable low noise amplifier for FM receiver”, IEEE Trans. Circuits Syst. I Regul. Pap 62, 600–606 (2014)

C.L. Ampli, H. Rashtian, S. Mirabbasi, “Applications of body biasing in multistage CMOS low-noise amplifiers”,. IEEE Trans. Circuits Syst. I Regul. Pap. 61(6), 1638–1647 (2014)

B. Razavi, M. Parvizi, K. Allidina, and M. N. El-gamal, “An Ultra-Low-Power Wideband Inductorless CMOS LNA With Tunable Active Shunt-Feedback,” vol. 39, no. 9, pp. 1843–1853, 2004.

M. Parvizi, K. Allidina, M.N. El-Gamal, An Ultra-Low-Power Wideband Inductorless CMOS LNA with Tunable Active Shunt-Feedback. IEEE Trans. Microw. Theory Tech. 64(6), 1843–1853 (2016)

M. Sun et al., 3–10 GHz ultra-wideband LNA with continuously variable gain for wireless communication. Microw. Opt. Technol. Lett. 58(7), 1697–1699 (2016)

B. Razavi, “RF Microelectronics Second Edition,” 2011 Pearson Educ. Inc., 2012.

J.S. Yuan, H. Tang, S. Member, H. Tang, CMOS RF Design for Reliability Using Adaptive Gate-Source Biasing. IEEE Trans. Electron Devices 55(9), 2348–2353 (2008)

L. Fuxing et al., Study on high power microwave nonlinear effects and degradation characteristics of C-band low noise amplifier. Microelectron. Reliab. 128, 114427 (2022)

S.M. Pazos, F.L. Aguirre, F. Palumbo, F. Silveira, Hot-carrier-injection resilient RF power amplifier using adaptive bias. Microelectron. Reliab. 114, 113912 (2020)

V. Narendra, siva Antoniadis, dimitri De, “impact of using adaptive body bias to compensate die-to-die Vt variation on within-die Vt variation.” IEEE, 1999.

Y. Liu, J. Yuan, S. Member, CMOS RF power amplifier variability and reliability resilient biasing design and analysis. IEEE Trans. Electron Devices 58(2), 540–546 (2010)

Y. Liu, J.-S. Yuan, S. Member, CMOS RF low-noise amplifier design for variability and reliability. IEEE Trans. Device Mater. Reliab. 11(3), 450–457 (2011)

C.L. Amplifiers, S. Naseh, M.J. Deen, C. Chen, Effects of hot-carrier stress on the performance of CMOS low-noise amplifiers. IEEE Trans. Device Mater. Reliab. 5(3), 501–508 (2005)

S. Ighilahriz et al., “Reliability study under DC stress on mmW LNA, Mixer and VCO,” in 2012 IEEE International Reliability Physics Symposium (IRPS), 2012, p. CR-4.

J. González, J. Cruz, D. Vázquez, and A. Rueda, “Analysis of process variations’ impact on a 2.4 GHz 90 nm CMOS LNA,” in 2013 IEEE 4th Latin American Symposium on Circuits and Systems (LASCAS), 2013, pp. 1–4.

C. Hsieh, S. Wang, C. Yeh, and W. Lin, “Reliability evaluation and redesign methodology for RFCMOS transceiver frontend circuits in sub‐6‐GHz band of fifth‐generation new radio communication based on the reliability model,” Int. J. Circuit Theory Appl., 2021.

A. Khoshgoftar, T. Azadmousavi, H. Faraji Baghtash, and E. Najafi Aghdam, “Robust Low-Voltage LNA Design to Overcome Reliability and Variability Issues,” in 1St Iranian Conference on Microelectronics, 2019, no. December, pp. 1–6.

M. Rahman, R. Harjani, A 2.4-GHz, Sub-1-V, 2.8-dB NF, 475-$\mu $ W dual-path noise and nonlinearity cancelling LNA for ultra-low-power radios. IEEE J. Solid-State Circuits 53(5), 1423–1430 (2018)

R. van de Plassche and W. Huijsing, JohanPlassche, Rudy J. van de,Sansen, “Low-noise and RF power amplifiers for telecommunication,” in Analog circuit design: volt electronics; mixed-mode systems; low-noise and RF power amplifiers for telecommunication, 1999, p. 301.

H. Rashtian, “On the use of body biasing to improve the performance of CMOS RF front-end building blocks,” A THESIS Submitt. Partial FULFILLMENT Requir. DEGREE Dr. Philos. Fac. Grad. Stud., no. July, 2013.

M. B. Yelten, “Design of a tunable LNA and its variability analysis through surrogate modeling,” no. February, pp. 1–11, 2020.

M. Varonen et al., “Cryogenic W-band SiGe BiCMOS low-noise amplifier,” in 2020 IEEE/MTT-S International Microwave Symposium (IMS), 2020, pp. 185–188.

Z. Chen et al., “A 29–37 GHz BiCMOS low-noise amplifier with 28.5 dB peak gain and 3.1–4.1 dB NF,” in 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2018, pp. 288–291.

Funding

The authors declare that no funds, grants, or other support were received during the preparation of this manuscript. The authors also declare that they have no financial interests.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors have not disclosed any competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Khoshgoftar, A., Faraji Baghtash, H., Najafi Aghdam, E. et al. Design of a Low-Voltage LNA with Considering Reliability and Variability Issues. J. Inst. Eng. India Ser. B 104, 115–128 (2023). https://doi.org/10.1007/s40031-022-00839-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40031-022-00839-y