Abstract

In this work, variation in threshold voltage is optimized for tunable body biasing CMOS power amplifier (PA). A two stage tunable biasing circuit is designed and integrated with class AB PA which improves variability in threshold voltage. Three most popular materials gallium arsenide, silicon and gallium nitride with two predictive technology model of 65 and 45 nm are employed for the analysis of threshold voltage optimization. A conventional single stage of tunable body biasing class AB PA is compared with a proposed PA of two stages. This concept demonstrates that threshold voltage variation can be lowered further if body biasing circuit is employed on the subsequent higher stages. The adaptive two stage body biasing design with class AB PA is analyzed with derived analytical equations. The calculated results shows gallium arsenide offers minimum variability in threshold voltage as compared to silicon and gallium nitride. Additionally, this class AB PA topology is simulated and fabricated for silicon material using 45 nm CMOS technology. The simulation results improve the robustness of the circuit in terms of performance parameters. S-parameter analysis is done that gives good agreement between simulated and measured results.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In preceding years, a continuous miniaturization of complementary metal oxide semiconductor (CMOS) technologies in nanometer scale is facing many reliability and degradation issues. Designer needs to pay more attention towards circuit design that are reliable and insensitive to the transistor parameter degradation. The resilient biasing technique aims to design reliable circuits that are capable of post process adjustment and insensitive to the transistor parameter degradation over long term stress effect [1, 2]. Random doping fluctuation is one of the most important fluctuation sources for threshold voltage. Due to random doping profile, the fluctuation of threshold voltage is expected to be larger [3]. Threshold voltage variation is inherent to the property of CMOS. The sensitivity of the threshold voltage variations in the critical dimensions is greater due to increasing shorter channel effects as the gate length is reduced using CMOS technology. The resilient or body bias technique dynamically changes the threshold voltage by varying voltage of the body terminal which depends upon the substrate materials as well as technology scaling. In the development of different device technologies or different semiconductor materials, much research has been investigated on threshold voltage variation. It is found that one of the most popular materials that is silicon (Si) for which variation in sensitivity of \(V_{T}\) is more as compared to other materials. Gallium Arsenide (GaAS) based MOS devices has advantages over silicon [4] based devices are of its high electron mobility, larger band gap, high critical field etc. which dominates towards the sensitivity of threshold variations. Additionally, gallium nitride (GaN) material also plays vital role as compared to Si and GaAs. But GaN material based parameters are more sensitive to external bias i.e. body potential which directly affects the threshold parameter of devices. A GaAs FET power switching performance with competing silicon devices (MOSFETs, FCTs, GTOs, and bipolar transistors) indicates that the GaAs FET will have better switching efficiency at all operating frequencies [5].

In [6], authors used adaptive gate biasing scheme to compensate the drain current in MOS circuits that is less sensitive to a threshold voltage and mobility degradation for radio frequency power amplifier design for reliability. In [7], authors from Intel argue that process variation is not an “insurmountable barrier” to Moore’s Law, but is simply another challenge to be overcome. Random doping fluctuation, oxide thickness variation and line edge roughness result in significant threshold voltage variation of CMOS transistors at the 45-nm technology node and below in [8–11]. In [12], adaptive substrate biasing scheme is used for low noise amplifier to improve process variability and circuit reliability. In [13], analysis and design of CMOS RF power amplifier using resilient biasing which reduces the impact of variability and reliability when subjected to threshold voltage shift and electron mobility degradation.

In this paper, optimization of the threshold voltage variation for RF CMOS power amplifier with two stages tunable body biasing is proposed. Analytical equations are derived for analysis using three materials with scaling in technology which reduce the threshold voltage shift in preceding stages. GaAs offered prominent threshold voltage variations as compared to Si and GaN. Moreover, this class AB topology achieves power added efficiency of 45 % with output power of 14.96 dBm during simulation. The design also achieves wide bandwidth at resonant frequency of 34 GHz within frequency band of operation. Section 2 describes the analysis of threshold voltage variations. The circuit implementation at design and fabricated level is discussed on Sect. 3. The results and discussion is in Sect. 4 and conclusion is followed in Sect. 5.

2 Analysis of Threshold Voltage Variation

This section describes the analysis of threshold voltage variation using different substrate materials with scale down in CMOS technology which reduces the impact of variability of \(V_{T}\). The tunable body biasing technique is already studied in [13]. It is observed that the threshold voltage \(V_{T}\) is the major circuit performance parameter for CMOS technology and its variability depends upon the substrate materials as well as technology scaling. The numerical analysis of \(V_{T}\) variation is discussed in next sub-sections A and B respectively.

2.1 Single Stage Class AB PA with Tunable Body Biasing

Figure 1 shows the conventional design of single stage body biasing class AB PA. In Liu and Yuan [13] have designed a resilient biasing technique for PA using silicon substrate with 65 nm PTM and achieved a more stable design in terms of sensitivity of threshold voltage variation \(\delta V_{T}\). During analysis, it is found that the level of reduction in \(V_{T}\) of MOSFET is related to the body effect coefficient γ and MOSFET structure coefficient β.

The β and γ depends upon the substrate material as well as technology scaling. Using this conception, three different materials Si, GaN and GaAs with two PTM of 65 and 45 nm are employed for the analysis of \(\delta V_{T}\). The calculated node voltage \(V_{BB}\) is given in Eq. (1) [13].

Here, \(V_{body}\) is voltage of MOSFET M2, \(V_{T2}^{ }\) is threshold voltage of M2 and \(\beta_{2}\) is MOSFET structure coefficient and its expression is (\(= \mu_{n} C_{ox} \frac{W}{L}\)). From this relation (1), it is noticed that the potential \(V_{{{\text{BB}} }}\) is a function of body bias \(V_{body}\) and threshold voltage \(V_{T2}^{ }\). Here, \(V_{body}\) is assumed to be constant and is lower than the supply voltage VDD. The parameter \(V_{T1}^{ }\) of MOSFET M1 due to body effect is given in Eq. (2).

Here, \(V_{TO}\) is zero bias threshold voltage of M1, \(\gamma\) is the body coefficient of M1 whose expression (\(\gamma = \frac{{\sqrt {2q \in_{substrate} N_{substrate} } }}{{C_{ox} }}\)) and \(\emptyset_{F}\) is the Fermi Potential (\(= \left( {\frac{kT}{q}} \right){ \ln }\left( {\frac{{N_{substrate } }}{{n_{i} }}} \right)\)). Now, parameters of the chosen materials Si, GaN and GaAs are analyzed using γ expression. It is possible to reduce \(\delta V_{T1}\) if designer chooses different substrate materials other than silicon where \(V_{T}^{ }\) is a critical parameter to be considered. The overall expression of \(\delta V_{T1}\) for single stage body bias PA is stated as in (3) [13].

From (1), (2) and (3), it is concluded that the threshold voltage of M1 depends on the potential \(V_{{{\text{BB}} }}\) and \(V_{{{\text{BB}} }}\) depends on biasing \(V_{body}\). Therefore, \(V_{T1}\) of M1 can be reduced to a minimum value by choosing \(\gamma\) and varying \(V_{BB}\) accordingly. All parameters of \(\gamma\) are constant except for \(\in_{substrate}\) and \(C_{ox}\). The \(V_{BB}\) potential corresponding to M1 by tuning body voltages is further divided into \(V_{{{\text{BB}}1 }}\) and \(V_{{{\text{BB}}2 }}\) and as shown in (4) and (5) respectively.

where \(V_{body1}\) and \(V_{body2}\) represent the two different tuning body voltages. According to [13], \(\delta V_{T1}^{{\prime }}\) corresponding to two different body voltages is given as in (6).

A comparison of calculated threshold voltages with respect to tune body voltage is as shown in Figs. 2 and 3 respectively. From the graph, it can be seen that \(V_{T1}\) of M1 decreases linearly when \(V_{body}\) increases from −0.2 to 0.2 V. The amount of percentage change in \(\updelta{\text{V}}_{\text{T}} /{\text{V}}_{\text{T}}\) with respect to \(V_{body}\) is shown in Table 1. The table highlights the importance of the selection of materials as well as plays vital role by scaling in device length which improves the level of threshold voltage variation reduction. According to graphs, GaAs shows minimum variation of sensitivity in threshold voltage as compared to Silicon and GaN.

2.2 Proposed Two Stage PA with Tunable Biasing

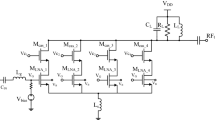

The proposed schematic of two stage body biasing class AB PA is shown in Fig. 4. For optimization of threshold voltage variation, three substrate materials (Si, GaN and GaAs) with scaling in technology are proposed for this analysis. It is found that can be possible to further reduce \(\delta V_{T1}\) of M1 with the help of one or more stage when incorporated with single body biased PA circuit. The \(V_{BB1}^{\prime}\) and \(V_{BB2}^{\prime}\) potentials are generated by tuning \(V_{body}\) and \(V^{\prime}_{body}\) voltages as shown in Eqs. (7) and (8) respectively.

Here, \({\text{V}}_{{{\text{body}}1}}^{\prime}\) and \({\text{V}}_{{{\text{body}}2}}^{\prime}\) is obtained by tuning \({\text{V}}_{\text{body}}^{\prime}\) whereas \({\text{V}}_{{{\text{body}}1}}\) and \({\text{V}}_{{{\text{body}}2}}\) by tuning \({\text{V}}_{\text{body}}\). \({\text{V}}_{{{\text{T}}3}}\) is threshold voltage of M3 which is constant. Now, two values of threshold voltage \(V_{T2}\) for M2 would be generated as \(V_{T21}\) and \(V_{T22}\) by tuning the body bias of M3 (\(V_{body}^{\prime}\)) whose expressions are given in (9) and (10).

Here, \({\text{V}}_{{{\text{T}}2{\text{O}}}}\) is zero bias threshold voltage of M2. Now putting the values of \(V_{T21}\) and \(V_{T22}\) in place of \(V_{T2}\) in Eqs. (4) and (5) and evaluate according to Eq. (6), the values for \(\delta V_{T1}\) is obtained. A complete expression is shown below which could be complicated when substituting \({\text{V}^{\prime}}_{{{\text{BB}}1 }}\) and \({\text{V}^{\prime}}_{{{\text{BB}}2 }}\) as given in (7) and (8) respectively.

Plots of the normalized value of \(V_{T1}\) with respect to \(V_{body}\) are shown in Figs. 5 and 6 respectively. The percentage change in \(\updelta{\text{V}}_{\text{T}} /{\text{V}}_{\text{T}}\) with respect to \(V_{body}\) is shown in Table 2. Here, the tabular data indicates fact that a two stage resilience network provides further reduction in \(\updelta{\text{V}}_{\text{T1}} .\) Again, GaAs shows calculated variation of \(\updelta{\text{V}}_{\text{T1}}\) from 1.80 to −1.82 % at 65 nm while 1.59 to −1.61 % at 45 nm. The proposed network can gives better performance of MOSFET because it is well known that threshold voltage is must small as much as possible.

3 Circuit Design

Figure 7 shows a 34 GHz class AB PA topology which includes two stage body biasing circuit, input matching network and output matching network. In class AB PA, matching networks is composed of C1, C2, C3, L2 and L3 with bias voltages of VGG and VDD. The biasing voltages are chosen according to [13]. The RF source is taken as 50 Ω and gets maximum power transformation when impedance matching network between source and transistor input are employed. It is possible to achieve maximum output power, gain and power added efficiency (PAE) by improving the input matching. The optimal output value is achieved by tuning the output matching network using ADS load pull instrument. The 45-nm NMOS transistors are modeled by the PTM equivalent BSIM4 model card. As discussed in above section, \(V_{T}\) is the most significant parameter and affected by body biasing of the transistors. According to [13], tunable biasing technique controls the body potential of the MOSFET which is to adjust the threshold voltage and to achieve maximum output power and PAE. So, here also two stages of tunable body biasing improve \(V_{T}\) variation of CMOS PA and after simulation achieves more output power, higher gain and best PAE. The proposed schematic design of 34 GHz PA topology is simulated using harmonic balance (HB) simulator in advanced design system (ADS) tool. Table 3. Gives design specifications of proposed power amplifier and its values. Figure 8 presents the chip photograph of the 34 GHz CMOS PA with a chip size of 0.84 × 0.95 mm2. For fabrication silicon substrate is utilized. The simulation and measured results of this design are discussed in next section.

4 Results and Discussion

The above discussed 34 GHz class AB PA topology is simulated by ADS using PTM model of 45 nm CMOS process. In the input matching, parallel inductance L1 is 1 nH and series capacitances C1 and C2 are 64 fF and 1.23 pF respectively. At the output, capacitance C3 is 1 pF where inductance value L3 is 1.2 nH. As shown in Fig. 9, at 34 GHz, output power is 14.96 dBm while input power signal is 0 dBm. It is observed that if input power is <0 dBm and with the increase of input power, output power increases but output powers stop up to a saturation point, once the input power exceeds the 0 dBm. It is seen that in Fig. 10, the maximum power added efficiency (PAE) of this circuit achieves up to 44.8 %. The PA is measured via On-wafer probing with test capability of 35 nm plate. The measurement of fabricated chip could be possible for s-parameters only. As per the simulation and measurement results, return loss is obtained at the operating frequency of 34 GHz within frequency range of 33–35 GHz which is shown in Fig. 11. It is small enough to indicate the satisfactory input matching. The best gain of 16.9 dB is achieved with the help of two stages tunable biasing body design can see in Fig. 11. A dc power dissipation of approximately 11.3 mW under 1 V power supply is utilized for this design. Table 4. Show comparison in parameters of circuit design with previous reported paper.

5 Conclusion

In this paper, two stage tunable body biasing class AB PA using three substrate materials with scaling in technology optimizes the threshold voltage variation. A single stage adaptive body biasing class AB PA is compared with two stages and it is analytically proven that the threshold voltage variation in preceding stages can be diminished if body biasing design is tunabled. A two stage tunable body biasing class AB Power amplifier with matching networks is simulated in ADS and shows that at operating frequency of 34 GHz, output power is 14.96 dBm and PAE of 44.8 %. Performance standards are met for the PA circuit. Moreover, state of the art of this work achieves S11 of −23 dB with forward gain of 16.9 dB which relaxed 50 Ω matching constraints throughout in PA circuit.

References

Kumar, S. V., Kim, C. H., & Sapatnekar, S. S. (2006). Impact of NBTI on SRAM read stability and design for reliability. In Proceedings of the 7th International symposium on quality electronic design (pp. 210–218).

Turner, T. E. (2006). Design for reliability. In Proceedings of international physics failure analysis (pp. 257–264).

Cheng, B., Roy, S., & Asenov, A. (2007). CMOS 6-T SRAM cell design subject to atomistic fluctuations. Solid State Electronics, 51, 565–571.

Atkinson, A. J. (1985). Power devices in gallium arsenide. IEEE Solid State and Electron Devices Letters, 132, 264–271.

Baliga, B. J., Adler, M. S., & Oliver, D. W. (1982). Optimum semiconductor for power field effect transistors. IEEE Electron Devices Letters, 2, 162–164.

Yuan, J. S., & Tang, H. (2008). CMOS RF design for reliability using adaptive gate–source biasing. IEEE Transactions on Electron Devices, 55, 2348–2353.

Li, Y., Hwang, C.-H., & Li, T.-Y. (2009). Random-dopant-induced variability in nano-CMOS devices and digital circuits. IEEE Transactions on Electron Devices, 56, 1588–1597.

Ye, Y., Gummalla, S., Wang, C.-C., Chakrabarti, C., & Cao, Y. (2010). Random variability modeling and its impact on scaled CMOS circuits. Journal of Computational Electronics, 9, 108–113.

Kuhn, K., Kenon, C., Kornfeld, A., Liu, M., Maheshwari, A., Shih, W.-K., et al. (2008). Managing process variation in Intel’s 45 nm CMOS technology. Intel Technology Journal, 12, 93–109.

Bhushan, M., Gattiker, A., Ketchen, M. B., & Das, K. K. (2006). Ring oscillator for CMOS process tuning and variability control. IEEE Transactions on Semiconductor Manufacturing, 19, 10–18.

Lee, K.-F., Li, Y., Li, T.-Y., Su, Z.-C., & Hwang, C.-H. (2010). Device and circuit level suppression technique for random-dopant-induced static noise margin fluctuation in 16-nm-gate SRAM cell. Microelectronics Reliability, 50, 647–651.

Liu, Y., & Yuan, J.-S. (2011). CMOS RF low-noise amplifier design for variability and reliability. IEEE Transactions on Device and Materials Reliability, 11, 450–457.

Liu, Y., & Yuan, J.-S. (2011). CMOS RF power amplifier variability and reliability resilient biasing design and analysis. IEEE Transactions on Electron Devices, 58, 540–546.

Acknowledgments

The foundry design kit and chip Implementation is done by Film electronics Pvt ltd. We would like to thanks Mr. Kamal and Mr. Ankur kumar gupta for supporting our work during the fabrication process.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kumar, S., Handa, M., Bhasin, H. et al. Optimized Threshold Voltage Variation for Tunable Body Biasing CMOS Power Amplifier. Wireless Pers Commun 91, 439–452 (2016). https://doi.org/10.1007/s11277-016-3469-4

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-016-3469-4