Abstract

A dynamic threshold voltage control strategy is presented in this paper to minimize leakage power while enhancing the speed and stability. The threshold voltage of driver and access transistor are tuned dynamically through a novel body-bias controller circuit. The word line signal level controls the action of the proposed body-bias controller. In order to reduce subthreshold leakage current, the threshold voltage of NMOS access and driver transistors are adjusted to a high value by applying a reverse body-bias. On the other hand, forward body-bias lowers the threshold voltage of NMOS access transistor thereby enabling faster read and writes operation. Simulation results shows that the proposed design is much better than conventional and other SRAM cells such as, NC SRAM, PP SRAM, WRE8T. The amount of leakage power reduction is as high as 41.071 % over conventional 6T SRAM cell when tested on (8 × 16) SRAM array. Whereas, the improvement in read and write delay is 30 and 15.81 % respectively.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Static random access memories (SRAMs) are the integral part of today’s electronic systems [1]. It plays a vital role of temporary storage in various digital devices such as, mobile phones, microprocessor, microcontrollers, personal computers and many others. System on chip (SOC) requires both low power consumption and high performance where SRAM covers a major portion of the total die area as reported in international technology roadmap semiconductor (ITRS) [2].

Supply voltage and device scaling are the most effective ways to achieve low power consumption and high speed in CMOS VLSI circuits [3]. Further, it is possible to attain minimum energy in sub-threshold region as explained in [4]. Again, MOSFET suffers from various short channel effects, which further leads to increase in sensitivity to process variation. Thus, designing in sub-threshold region is a critical design challenge in mobile SOCs [5].

We can expect reduced threshold voltage (Vt), channel length and gate oxide thickness in MOSFET devices today because of continued device scaling [6]. This has consequently led to excessive leakage power consumption. At present leakage power consumption is the dominant contributor of total power consumption in SRAM cells and many other portable digital systems.

However, scaling of supply voltages faces many obstacles such as reduction in read static noise margin (RSNM), write static noise margin (WSNM) and operating speed [7, 8]. Stability in SRAM cell is also caused by the mismatch in Vt of cross-coupled inverter pair [9]. Reduction in supply voltage also reduces SRAM cell current, which consequently decreases the speed of cell. Moreover, power density is a growing concern in today’s high performance chip which even demands for thermal-aware design [10].

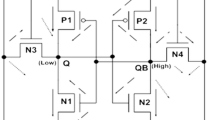

FD-SOI device has been proposed [11], to solve the static noise margin problem, but its high cost and difficulty in manufacturing limits its use. A variable threshold design of MOSFET is highly desirable in such a situation which can be solved by controlling the bulk potential of a MOSFET device. Bulk voltage in CMOS technology cannot be changed abruptly to a high or a low value because if a reverse body-bias (RBB) is applied across the bulk it may abruptly increase the leakage current in the form of band-to-band tunneling. Again if we forward body-bias (FBB) the bulk of a MOSFET abruptly, then it may cause the latch up current to increase. Consequently it may damage the transistor. So it is important to optimally control the Vt of MOSFET devices for minimum leakage, high speed and good stability. Figure 1 shows the conventional 6T SRAM cell structure which consists of four NMOS transistors and two PMOS transistors. N1, N2 are the two driver NMOS transistors and N3, N4 are the two access NMOS transistors. Whereas, P1 and P2 are the two PMOS load transistors. As indicated in the Fig. 1, maximum amount of leakage is flowing through the NMOS transistor that is from Vdd to ground (dashed line in red) and bitline to ground (dotted line in red). The dominant leakage mechanism in 6T SRAM cell are subthreshold and gate-leakage. Now a days, gate leakage is usually controlled by the use of high K metal gates [12].

As the number of NMOS transistor in SRAM cell is more, so maximum leakage saving is gained by RBB the NMOS transistor during standby mode. The speed of the cell can also be enhanced by FBB the NMOS access transistor (N3 and N4) in active mode. In RBB, Vt of a transistor becomes high and with FBB, Vt of a transistor becomes low. These two performances metric can be achieved by over-driven body-bias [13] which causes the body voltage to move further beyond the supply rail as shown in Fig. 2. High Vt transistors are usually slow and have low subthreshold leakage current. Low Vt transistors on the other hand are fast and have high subthreshold leakage current. The propagation delay (tpd) and sub threshold leakage (Ileakage) current as given in [14, 15] can be written as,

where CL is the load capacitance, Vdd is the supply voltage, IDS is the drain current in the saturation, Vt is the threshold voltage and A is constant.

where, I0 = μC ox \(\frac{W}{L}V^{2} e^{1.8}\), Vth = \(\frac{KT}{q}\) = 0.026 Vµ denotes carrier mobility, C ox is the gate oxide capacitance per unit area, Vth is thermal voltage, W is width is the Boltzmann constant, T is the absolute temperature, q is the electrical charge of conduction, n is a constant and S = nVth ln 10 is the sub threshold slope of 100 mV/decade, each 100 mV decrease in Vt will cause an order of magnitude increase in leakage current.

A typical memory organization consists of individual cells arranged in an array of horizontal rows and vertical columns [16]. Based on word line signal, a particular row of the cell is in active mode and others are in standby mode. In this paper, we propose a word-line based controller circuit to operate the SRAM cell in active and standby mode. The word line signal defines the two different body voltages for NMOS transistors in active and standby mode.

The rest of the paper is organized as follows. Section 2 presents the design of the proposed controller. Section 3 analyzes the simulation results of the proposed SRAM cell. Finally, Sect. 4 concludes the paper.

2 Related Works

In this section, we review some of the previously proposed SRAM cell architectures. Ref. [17] proposes a new architecture termed as NC SRAM cell. The main idea of this cell is the use two pass transistors, NC1 and NC2, which provide different ground levels to the memory cell in the active and idle mode as shown in Fig. 3. In active mode, the source of the driver transistor is connected to the ground. But in the idle mode, the source of the driver transistor is biased positively to raise its voltage above the ground level. This causes the subthreshold leakage current to reduce. This reduction of subthreshold current is because of increase in Vt due to body effect. Again, further reduction of leakage current is due to reduction in the drain-source voltage and consequently due to lower DIBL effect. In this cell, in order to reduce the bit-line leakage, the pass transistors (N3, N4) with higher Vt are used. While, to decrease the leakage currents of NC1 and NC2, their Vt has also been increased. Thus NC-SRAM is able to reduce static power consumption using the virtual ground level technique and increasing the Vt, but it has caused extra dynamic power consumption along with degradation in SNM and performance.

NC SRAM cell [17]

In [18], another cell called PP-SRAM is suggested which uses PMOS access transistors instead of NMOS access transistor in order to reduce gate leakages shown in Fig. 4. Since the mobility of holes is less than the mobility of electrons, so using PMOS transistor it would cause a reduction in timing performance. To compensate this performance reduction, it is necessary to use PMOS transistor whose width is wider than the NMOS transistor. As a result of which it would cause increase in capacity of parasitic capacitors and finally increase in power.

PP SRAM cell [18]

Ref. [19] proposes a write and read enhanced 8T SRAM cell (WRE8T) structure as illustrated in Fig. 5. The beauty of the architecture is that it minimizes the subthreshold leakage current by stacking four transistors (M7-M3-M1-M8). This SRAM cell basically improves the read and writes static power. Further, the read delay in this scheme is also less due to single ended read operation. This is because capacitance associated with large drivers are now removed. Write delay however, is higher than the differential SRAM cell due to single ended operation.

WRE8T SRAM [19]

3 Proposed Controller Design

This section presents the 6T SRAM cell with the proposed controller circuit. Figure 6a shows the conventional 6T SRAM cell with a provision to accommodate the control signals (marked in red and blue node). The proposed controller circuit is shown in Fig. 6b, c and is designed with a minimum number of transistors which will help in improving the speed during active mode and reduce the leakage power during standby mode.

In an array of SRAM cell, the body bias voltage of NMOS access and driver transistor will be controlled by the word line signal levels. To control the leakage power, speed and stability, different voltages levels are required at the body terminal during active and standby mode. In Fig. 6a red node indicates body bias voltage for NMOS-access transistor and blue node indicates body bias voltage for NMOS-driver transistor. In standby mode, word line signal, WL = 0 and as such WL (bar) = 1. The X-node (red node) of body bias controller in Fig. 6b transfers Vss − ΔV to the body of NMOS-access transistor. Similarly, Y node (blue node) in Fig. 6c transfers Vss − ΔVto the body of driver transistor. These body bias voltages will offer a high Vt to both NMOS driver and access transistors, which consequently reduces the leakage current. During active mode, WL = 1 and so WL (Bar) = 0, which enables X-node to transfers small FBB voltage of (+ΔV) to NMOS access transistor and enables Y-node to transfer a voltage Vss = Gnd (i.e. no body-bias) to the body of NMOS driver transistor. The NMOS-access transistor is now FBB which will now offer a low Vt and consequently it will enhance the read/write speed. On the other hand, driver transistor will get no-body bias (because of ground potential to the bulk of NMOS transistor). To avoid the stability problem we are keeping no body bias to the load and driver transistors in active mode becauseVt variation of driver transistor has the largest impact on the voltage transfer characteristic and as such W/L ratio of driver transistor is large compared to other transistors in a SRAM cell [20]. The combination of SRAM cell and controller circuit provides good operation during active and standby mode. To test the functionality of the circuit we have chosen arbitrarily a FBB of +ΔV = 0.4 V and RBB of Vss − ΔV = −0.23 V, Vss = ground and Vdd = 1 V at 65 nm technology. Depending upon the word line signal level (WL), the controller circuit transfers a voltage to the body of NMOS access transistor, Vx = 0.4 V during active mode (WL = 1) and Vss − ΔV = −0.23 V during standby mode (WL = 0). Similarly, for NMOS driver transistor, the control circuit transfers a voltage to the body terminal.

Vss = ground (0 V) during active mode and Vss − ΔV = −0.23 V during standby mode. Based on these values the simulated waveform of the control circuit is shown in Fig. 7. Array structure with the proposed controller is shown in Fig. 8. The control lines from the controller circuit are indicated in blue and red lines, which are shared by the row of cells.

4 Results and Discussion

To verify the proposed design, extensive simulations with Tanner EDA tool using a 65 nm predictive technology model (PTM) [21] were performed. The performance of the proposed SRAM cell then compared with conventional (6T), NC SRAM, PP SRAM and WRE8T SRAM cells taking 1 V as power supply.

4.1 Static Power Dissipation

Static power dissipation of the circuit is measured during standby mode (when WL = 0). In standby mode, bit line pairs are charged and word line signal level is zero which turns-OFF the access transistors. The driver and access transistors are over driven by applying a RBB of Vss − ΔV to the body of NMOS transistor. In this way Vt of the NMOS transistors (driver and access) is raised to a high value, which will reduce the leakage current in SRAM cell. Table 1, shows the simulated values of static power dissipation with a wide variation in RBB voltage which are indicated as Vx and Vy values. Form the table, it is clear that the proposed design substantially reduces the static power dissipation when Vx = Vy = Vss − ΔV = −0.45 V, which is about 41.071 % in an 8 × 16 array. The static power dissipation of proposed design is also compared with all other designs referred earlier and is represented as bar-chart in Fig. 9. From the figure, we can observe that proposed design gives better reduction than all other designs at different body bias voltages.

Static power dissipation is also a function of temperature. Comparison of static power for the proposed and conventional SRAM cell at different temperature is shown in Fig. 10. For simulation purposes, we have limited the reverse body-bias voltages up to −0.45 V. Beyond this voltage level the static power values come out to be erratic probably because of excessive tunneling which has been verified experimentally in [22]. Similarly, Fig. 11 shows the comparison of proposed and conventional SRAM cell at different process conditions.

4.2 Read and Write Delay

Read and write delay of SRAM cell is calculated when the word line signal gets activated (i.e. WL = 1). In the architecture of proposed SRAM cell as shown in Figs. 6 and 8, the control circuit transfers a small forward bias of Vx = +ΔV through X node (red node) to the body of NMOS-access transistor.

This Vx will lower the Vt of NMOS access transistor thus enhancing the read and write speed. On the other hand, Y node (blue node) is supplied with Vy = Vss (ground) to the body of NMOS driver transistor keeping the transistor in no-body bias (means body voltage to ground) state.

Read and write delay of the circuit is calculated over some range of FBB from Vx = 0.3 V to 0.5 V. Table 2 shows the result of simulation for read and write delay. It can be seen that the proposed design gives a better read and write performance over conventional 6T SRAM cell at different process corners as shown in the bar diagram of Figs. 12 and 13.

In the structure of NC SRAM cell which uses high Vt pass transistor, the voltage level of the ground increases. This causes the read and write performance to degrade. In PP-SRAM, the read and write performance is enhanced by reducing the Vt of PMOS transistor through S and Sbar signals. In case of WRE8T, write operation is single ended, so write delay is more than differential write operation. On the other hand, the single ended read operation leads to decreased in read delay. This is because capacitance related to large write drivers are removed from bit lines during read operation.

Figure 14 and 15 shows the comparison of read and write delay. Simulation shows that a better read and write performance can be obtained as we go on increasing the FBB (Vx). Further, it is seen that the proposed design could achieve a read delay reduction of 30 % and write delay reduction of 15.81 % over conventional 6T SRAM cell through the use of body bias controller.

4.3 Static Noise Margin

Static noise margin is determined by the side length of smaller square as illustrated in Fig. 16. SNM is highly dependent on the β ratio in SRAM cell. The β ratio of conventional 6T and proposed SRAM cell is taken as 1.8. So, W/L ratio of driver transistor is large compared to all other transistors in SRAM cell. The simulated butterfly curve for static noise margin (SNM) during read operation is shown in Fig. 16.

During active mode, the Vt of driver transistor remains unchanged, because Vt variation has the largest impact on voltage transfer characteristic in SRAM cell. Thus the body of driver transistor is tied to Vss (ground), hence there is no body bias.

But to reduce the read and write delay, the Vt of access transistor is decreased by applying a FBB, Vx = +ΔV. This reduction in Vt of access transistor has a negative impact on read SNM. Consequently, stability is little degraded during read operation when Vx is gradually changed. From the plot of read SNM in Fig. 16 we can observe that as we gradually increase the FBB of access transistor, the read stability decreases which can be observed from the Table 3.

Writing in SRAM cell takes place, when the bitline pairs (BL and BL bar) are set with VDD and 0 V respectively. The write operation can be carried out successfully, when access transistor and write driver win the fight with the PMOS pull-up transistor inside the cell. An improved noise margin is achieved in the proposed SRAM cell because of the reduction in Vt of accessed transistor. From Table 3 we can observe that the improvement in write margin is about 18.70 % at Vx = 0.5 V.

Butterfly curve of hold static noise margin (HSNM) of conventional 6T and proposed SRAM cell during standby mode is shown in Fig. 17. In this mode, Vt of all transistors are high, which causes less leakage current to flow, so the static noise margin is improved. As the body bias voltage Vx and Vy of proposed cell increases, voltage transfer characteristic curve is expanded and the size of the butterfly lobe increases which means a better HSNM. Table 4 shows an improvement of 29.9 % in hold static noise margin at Vx = Vy = −0.32 V as compared to conventional 6T SRAM cell.

4.4 Dynamic Power dissipation

Dynamic power is calculated during active mode, so to calculate the same, access transistors of both the conventional and proposed cell need to be turned ON. Table 5 shows the comparison of dynamic power in case of conventional 6T and proposed SRAM cell. In the proposed SRAM cell architecture, each row of SRAM cell is connected to the control circuit. Moreover, the bulk of each transistor of SRAM cell is connected to an appropriate control signal. Charging/discharging of capacitances with respect to control signals activity and variation of Vt with the proposed controller leads to increase in dynamic power dissipation of the proposed cell as compared to conventional 6T SRAM cell. Table 5 shows the dynamic power dissipation of 8 × 16 SRAM array. From the table, we can conclude that increase in dynamic power is negligibly small with the proposed design even for large arrays as compared to conventional SRAM array.

4.5 Layout

The layout of a 8 × 16 SRAM array architecture is shown in Fig. 18. The layout of proposed SRAM cell is generated using L-EDIT environment in Tanner EDA tool. Although it causes some extra area overhead due to controller circuit, but it is least concern in nanometer regime, which can be further reduced by using common controller for multiple bit SRAM cells.

5 Conclusion

Leakage power, speed and stability are the critical issues in SRAM design. In this paper, a novel controller circuit is introduced, whose functioning is based on word line signal level. This control circuit minimizes the leakage power, reducing the delay and improves the stability by controlling the Vt of NMOS driver and access transistors of SRAM cell. In standby mode, static power consumption of 8 × 16 array is reduced by about 41.07 % and the read and write delay is enhanced by 30 and 15.8 % respectively. The cell also exhibits higher HSNM and WSNM of 29.9 and 18.7 % respectively by the variation of Vt. Furthermore, with proposed design, the amount of dynamic power penalty is about 7.76 % in 8 × 16 array whereas, the penalty in read stability is about 14.2 %. This can be considered to be in acceptable range. We have also verified the effectiveness of the proposed SRAM cell, under various process, voltage and temperature variations using 65 nm technology. The results are found to be very promising.

References

Prince, B. (1991). Semiconductor memories. New York: Wiley.

International Technology Roadmap for Semiconductors. (2012). http://www.itrs.net/Links/2012ITRS/Home2012.htm.

Yamaoka, M., & Kawahara, T. (2007). Operating-margin-improved SRAM with column-at-a-time body-bias control technique. In Proceedings of the european solid-state circuits conference (ESSCIRC) (pp. 396–399).

Yang, Y., Park, J., Song, S. C., Wang, J., Yeap, G., & Jung, S. O. (2015). Single-ended 9T SRAM cell for near-threshold voltage operation with enhanced read performance in 22-nm FinFET technology. IEEE Transaction on Very Large Scale Integration, 23(11), 2748–2752.

Dreslinski, R. G., Wieckowski, M., Blaauw, D., Sylvester, D., & Mudge, T. (2010). Near-threshold computing: reclaiming Moore’s law through energy efficient integrated circuits. Proceedings IEEE, 98(2), 253–266.

Sinha, S., & Chaudhury, S. (2013). Impact of oxide thickness on gate capacitance—A comprehensive analysis on MOSFET, nanowire FET, and CNTFET devices. IEEE Transaction on Nanotechnology, 12(6), 958–965.

Seevinck, E., List, F. J., & Lohstroh, J. (1987). Static noise margin analysis of MOS SRAM cells. IEEE Journal of Solid State Circuits, 22(5), 748–754.

Takeda, K., Ikeda, H., Hagihara, Y., Nomura, M., & Kobatake, H. (2006). Redefinition of write margin for next-generation SRAM and write-margin monitoring circuit. In Proceedings international solid-state circuits conference (pp. 630–631).

Calhoun, B. H., & Chandrakasan, A. (2005). Analysing static noise margin for sub-threshold SRAM in 65 nm CMOS. In Proceedings ESSCIRC (pp. 363–366).

Chaudhury, S., Sistla, K. T., & Chattopadhyay, S. (2009). Genetic algorithm based FSM synthesis with area and power trade-offs. Proceedings Integration the VLSI Journal, Elsevier, 42(3), 376–384.

Yamaoka, M., Maeda, N., Shinozaki, Y., Shimazaki, Y., Nii, K., & Shimada, S., et al. (2005). Low-power embedded SRAM modules with expanded margins for writing. In Proceedings ISSCC (pp. 480–611).

Nho, H., Kolar, P., Hamzaoglu, F., Wang, Y., Karl, E., & Ng, Y. G., et al. (2010). A 32 nm high-k metal gate SRAM with adaptive dynamic stability enhancement for low-voltage operation. In Proceedings IEEE international solid-state circuits conference (ISSCC) (pp. 346–347).

Ananthan, H., Kim, C. H., & Roy, K. (2004). Larger than—Vdd forward body bias in sub-0.5v nanoscale CMOS. In Proceedings ISLPED (pp. 8–13).

Kao, J. T., & Chandrakasen, A. (2000). Dual-threshold voltage techniques for low-power digital circuits. IEEE Journal of Solid State Circuits, 7(35), 1009–1018.

Kao, J., Chandrakasan, A., & Antoniadis, D. (1997). Transistor sizing issues and tool for multi-threshold CMOS technology. In Proceedings of design automation conference (pp. 409–414).

Kang, S., & Leblebici, Y. (2003). CMOS digital integrated circuits. New York: Mc-Graw hill.

Elakkumanan, P., Thondapu, C., & Sridhar, R. (2004). A gate leakage reduction strategy for sub-70 nm memory circuit in implementation of high performance circuits. In Proceedings of the IEEE dallas/CAS workshop (pp. 145–148) Texas.

Razavipour, G., Afzali-Kusha, A., & Pedram, M. (2009). Design and analysis of two low-power SRAM cell structures. IEEE Transactions on Very Large Scale Integration Systems, 10(17), 1551–1555.

Pasendiand, G., & Fakhraie, S. M. (2014). An 8T low voltage and low leakage half selection disturb free SRAM using Bulk-CMOS and FinFETs. IEEE Transactions Electron Devices, 7(61), 2357–2363.

Pavlov, A., Sachdev, M., & Pineda de Gyvez, J. (2004). An SRAM weak cell fault model and a DFT technique with a programmable detection threshold. In Proceedings of ITC international test conference (pp. 1006–1015).

Srivastava, A., & Zang, C. (2008). An adaptive body bias generator for low voltage CMOS VLSI circuits. International Journal of Distributed Sensor Networks, 4, 213–222.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lorenzo, R., Chaudhury, S. A Novel SRAM Cell Design with a Body-Bias Controller Circuit for Low Leakage, High Speed and Improved Stability. Wireless Pers Commun 94, 3513–3529 (2017). https://doi.org/10.1007/s11277-016-3788-5

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-016-3788-5