Abstract

In this work, the characteristics of the CdS/Si structure produced by plasma-induced bonding technique were studied. The produced structure was an asymmetric heterojunction consisting of n-type CdS on a p-type silicon substrate. The Si substrate and CdS sample were bonded by subjecting them to the plasma formed between two electrodes. The measurements included the structural and electrical characteristics. The typical spectral responsivity within the range 400–800 nm and the maximum value is at 577 nm. With dark current of 6 μA, maximum reverse bias current of 670 μA and ideality factor of 3.5, the results explained better characteristics than those of the same heterojunction produced by other deposition techniques.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Direct bonding means the joining of two smooth and clean surfaces at room temperature (Zhou et al. 2000). No constraint on lattice matching exists and after joining the two surfaces, the bonded pairs are annealed at a high temperature to ensure the formation of strong bonding (Mathine 1997). With proper procedure the bonded interface can achieve bulk strength (Stengl et al. 1988).

If two solids with clean and flat surfaces are brought into close proximity at room temperature, attractive forces pulls the two bodies together into intimate contact so that bonds can form across the interface (Widdershoven et al. 1990). The phenomenon was given rather little attention until in the last decades when semiconductors bonding found several applications in mircomechanics, microelectronics and optoelectronics (Gösele et al. 1995).

There are many factors governing the bonding behavior of two surfaces. First, the surfaces must be flat and smooth (Takagi et al. 1996). Usually it is argued that surfaces can make contact only at some asperities. However, the success of bonding technique has followed the development of modern semiconductor chemical–mechanical polishing (CMP) technology (Gösele et al. 1995). The semiconductor polishing technology has reached such a level of maturity that, nowadays, commercial silicon wafers have surface roughness in the order of 10−10m. The second parameter governing the ability for bonding is the surface chemical state and surface termination (Berthold et al. 1998). For most semiconductors, surface preparation and cleaning techniques are well-developed and characterized. However, in silicon technology the surface chemical treatments are more standardized and established processes, as compared to, for example, compound semiconductors (Tong et al. 1998).

One of the great potentials of the bonding approach is the integration of dissimilar materials (Krauter et al. 1997). Integration of dissimilar semiconductor by heteroepitaxial growth is hampered by the difference in lattice constants. Particularly, combining compounds semiconductors with highly developed silicon circuits has been pursued in recent years with the goal to incorporate photonic and high-speed devices with advanced silicon technology (Levine et al. 1999).

When the solids are bonded together at room temperature, usually the interaction, or bonding energy, is relatively weak (Black et al. 1997). Therefore, a heat treatment is performed to increase the bond-strength. The annealing enhances out-diffusion of interface trapped molecules and desorption of chemisorbed surface atoms, such as hydrogen (Wada et al. 1999). At the same time the annealing activates formation of covalent bonds between the bonded surfaces, like solid-to-solid bonding in the case of hydrophobic bonding. The thermal treatment used to increase the bond-strength can, unfortunately, also cause severe problems in bonding technique. For instance, when bonding dissimilar materials, the thermal mismatch induced high stresses in the material (Kikuchi and Adachi 2000). High temperature annealing also restricts the use of metal patterns and can cause diffusion of dopants (Zazzera and Moulder 1989).

Chemically reactive plasma discharges are widely used to modify the surface properties. The relative importance of a specific discharge depends on input power, gases, reactor volume and geometry, gas flows, etc. For instance, plasma discharges are employed for etching, deposition or surface cleaning (Kish et al. 1995). The gas-chemistry and the plasma parameters (effect, applied voltage, pressure, plasma density, etc.) that are being used govern the plasma/surface interactions (Gösele et al. 1995). A variety of gases are such as Ar, O2, SF6, Cl2 and CHF3 are used for this purpose.

Wafer bonded p-n hetrojunction characteristics are heavily affected by the non-ideal interface. However, a substantial improvement of wafer bonded p-n heterojunctions characteristics is usually obtained by shifting the p-n transition away from the bonded interface, either by high temperature annealing or by implantation (Kopperschmidt et al. 1997; Hawkins et al. 1996).

In this work, the use of plasma activation of the surfaces before bonding has been examined to achieve a low-temperature bonding of cadmium sulfide and silicon samples to form a heterojunction for photodetection applications.

2 Experimental work

High purity (99.999) (100)-oriented p-type silicon wafers of 500 μm thickness and 3 Ω cm resistivity were used in this work. Also, high purity (99.999) cadmium sulfide (CdS) was used to form 350 μm-thick samples. Both samples, Si and CdS, were washed with distilled water then rinsed in ethanol and subjected to ultrasonic waves for 10 min, then dried by hot air. The silicon samples were then cleaned with HF for 5 min to remove any residual oxides which have existed on their surfaces. Both samples were softly grinded and polished to obtain flat surfaces. Then, these samples were rinsed in ethanol to remove acids then dried to be ready for processing. More details can be found in previous works of the author (Hamadi 2007, 2008).

The Si and CdS samples were mounted inside the homemade plasma system, which is working under vacuum of (10−10 mbar) at room temperature. The silicon substrate was mounted on a holder made of stainless steel at a specified distance from the anode and the CdS sample was placed on the Si substrate. The samples were placed at a position that the plasma is entirely surrounding the sample. Discharge voltage and current are 15 kVDC and 3 A, respectively. Argon gas at a pressure of (1 mbar) was used to generate the discharge plasma. The sample was maintained inside the operated system for 10 min before being removed and tested.

Before bonding, the native oxide is removed from the surfaces to have a solid-to-solid bonding (Kikuchi and Adachi 2000). However, the bonding is very weak at room temperature and after low-temperature annealing because of the hydrogen-terminated surface. A high-temperature annealing above 520 °C is necessary to desorb hydrogen from surface and enable a covalent bonding.

Electrical measurements were carried out using a Farnell DC power supply and Keithley-616 digital electrometer while the C-V measurements were performed using hp/4192 ALF LCZ device. The samples were subjected heating up to 600 °C within 5 min then left to return to its initial temperature within the same period of time. The nanoscale structure of the treated samples was introduced using Hitachi S-4800 FE-SEM instrument.

Five samples were prepared to introduce the repeatability of this technique. Along 5 days, a sample was daily prepared and processed at the same conditions and the presented results are the average of these samples. Therefore, this technique has very good repeatability as the preparation and processing conditions are kept stable as possible. The experimental preparation and processing conditions mentioned above can be considered as the optimum to obtain the best results in this work.

3 Results and discussion

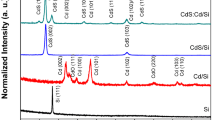

If two identical solids with the same orientation are bonded together without misalignment and without interface contamination, they should merge into one. However, there are always deviations from the ideal case. In the bonding technique, there is always an unavoidable misalignment between the bonded solids and therefore misfit dislocations appear. Misfit dislocations will also appear at the bonded interface if two solids of different orientation or different lattices are bonded. The presence of native oxides, adsorbed surface contaminants and interface bubbles (voids), also inhibit a perfect solid-to-solid transition region. Figure 1 explains the nanostructure of the bonded CdS/Si samples.

Defect-etching techniques were found to be more suited for investigations of bulk material defect introduced by the bonding technique, arising mainly from thermal mismatch stress. Defect-etching uses etch selectivity to reveal crystal imperfection such as dislocation. The dislocation appears as pits on CdS/Si bonding interface, as shown in Fig. 1.

A generalized theory for bonding technique may be difficult to achieve since the electrical properties of the bonded interface depends on many parameters. The electrical properties vary between different reports and it is likely that such deviations are linked to variations in bonding procedures. The disordered interface being composed of misfit dislocation acts as gettering and segregation site in the same way as grain boundaries in polycrystalline semiconductors.

The p-n heterojunction formed under ultra-high vacuum (UHV) conditions and low-temperature results in an ideality factor no more than 2 and indicates low recombination at the interface. Bonding p-n heterojunction in ambient air and subsequent high temperature annealing was seen to yield high recombination near the bonded interface. Figure 2 shows the I–V characteristics of bonded n-p CdS/Si heterojunction. The dark current is about 6 μA and the forward current is uniformly linear while photocurrent up to 670 μA was measured at illumination level of 10 mW. The fabricated heterojunctions exhibit an average ideality factor of 3.5.

The bonded interface is often avoided in the electrically active region of the electronic device. However, the recombination centers of the defective bonded interface are used to control the minority carrier lifetime in power devices.

The spectral responsivity of the CdS/Si heterojunction was determined as a function of wavelength as shown in Fig. 3. This heterojunction responds in the 550–600 nm range much more than in the range below 550 nm and beyond 600 nm while the maximum responsivity is observed at 577 nm. Another peak of responsivity can be observed at 707 nm. This cheap technique presents an advantage to produce good photodetectors for the wavelengths within 500–600 nm.

Integration of CdS and Si has attracted much interest since the unique properties in each material can be combined in devices or systems, such as CdS-based piezoelectric devices and optoelectronics components. The epitaxial growth of CdS on Si substrate is hampered by the difference between the lattice constants of the materials. However, using bonding for the integration, the lattice-mismatch becomes no obstacle.

In each material system, nature has imposed a set of physical properties, such as mobility, optical absorption, resistivity, thermal and mechanical properties. For a given application, the optimal properties may not reside in a single material but in a variety of dissimilar materials. A specific case is to combine compound semiconductor that have direct band gap and high mobility with Si that is extensively used in microelectronic applications.

For lattice-matched materials systems, the material integration is extensively and routinely realized using heteroepitaxy. However, for material systems that are largely lattice-mismatched, heteroepitaxial growth has not been able to produce the high quality material needed in optoelectronics (Yamaguchi et al. 1995; Pasquariello and Hjort 2000; Fontcuberta i Morral et al. 2003).

4 Conclusions

A CdS/Si heterojunction was produced by plasma-induced bonding techniques. The structural characteristics explained the good bonding interface between the CdS and Si samples. Electrical measurements showed reasonable enhancement in the heterojunction characteristics compared to that produced by another techniques. Despite the complexity imposed by the plasma processing system, production of heterojunctions with such enhanced characteristics has advantages of low cost and large size devices.

References

Berthold, A., Jakoby, B., Vellekoop, M.J.: Wafer-to-wafer fusion bonding of oxidized silicon to silicon at low temperatures. Sens. Actuators A68, 410–413 (1998)

Black, A., Hawkins, A.R., Margalit, N.M., Babic, D.I., Holmes, A.L., Chang, Y.-L., Abraham, P., Bowers, J.E., Hu, E.L.: Wafer fusion: materials issues and device results. IEEE J. Sel. Top. Quantum Electron. 3, 943–951 (1997)

Fontcuberta i Morral, A., Zahler, J.M., Atwater, H.A.: InGaAs/InP double heterostructures on InP/Si templates fabricated by wafer bonding and hydrogen-induced exfoliation. Appl. Phys. Lett. 83(26), 5413–5415 (2003)

Gösele, U., Steinnkirchner, J., Martini, T., Reiche, M., Kästner, G.: Silicon wafer bonding via designed monolayers. Adv. Mater. 7(7), 662–665 (1995a)

Gösele, U., Stenzel, H., Martini, T., Steinkirchner, J., Conrad, D., Scheerschmidt, K.: Self-propagating room-temperature silicon wafer bonding in ultrahigh vacuum. Appl. Phys. Lett. 67, 3614–3616 (1995b)

Gösele, U., Stenzel, H., Martini, T., Steinkirchner, J., Conrad, D., Scheerschmidt, K.: Self-propagating room-temperature silicon wafer bonding in ultrahigh vacuum. Appl. Phys. Lett. 67(24), 3614–3616 (1995c)

Hamadi, O.A.: Characteristics of CdO–Si heterostructure produced by plasma-induced bonding technique. Proc. Inst. Mech. Eng. Part L J. Mater. Des. Appl. 222, 65–71 (2007). doi:10.1243/14644207JMDA56

Hamadi, O.A.: Effect of annealing on the electrical characteristics of CdO–Si heterostructure produced by plasma-induced bonding technique. Iraqi J. Appl. Phys. 4(3), 33–37 (2008). http://iasj.net/iasj?func=fulltext&aId=61821

Hawkins, A., Wu, W., Abraham, P., Streubel, K., Bowers, J.E.: High gain-bandwidth-product silicon heterointerface photodetector. Appl. Phys. Lett. 70, 303–305 (1996)

Kikuchi, D., Adachi, S.C.: Chemically cleaned InP(100) surfaces in aqueous HF solutions. Mater. Sci. Eng. B 76, 133–138 (2000)

Kish, F.A., Vanderwater, D.A., Peansky, M.J., Ludowise, M.J., Hummel, S.G., Rosner, S.J.: Low-resistance ohmic conduction across compound semiconductor wafer-bonded interfaces. Appl. Phys. Lett. 67, 2060–2062 (1995)

Kopperschmidt, P., Kästner, G., Hesse, D., Zakharov, N.D., Gösele, U.: High bond energy and thermomechanical stress in silicon on sapphire wafer bonding. Appl. Phys. Lett. 70(22), 2972–2974 (1997)

Krauter, G., Schumacher, A., Gösele, U., Jaworek, T., Wagner, G.: Room temperature silicon wafer bonding with ultra-thin polymer films. Adv. Mater. 9, 417–420 (1997)

Levine, B., Pinzone, C.J., Hui, S., King, C.A., Leibenguth, R.E., Zolnowski, D.R., Lang, D.V., Krautter, H.W., Geva, M.: Ultralow-dark-current wafer-bonded Si/InGaAs photodetectors. Appl. Phys. Lett. 75, 2141–2143 (1999)

Mathine, D.L.: The integration of III-V optoelectronics with silicon circuitry. IEEE J. Sel. Top. Quantum Electron. 3, 952–959 (1997)

Pasquariello, D., Hjort, K.: Mesa-Spacers: enabling non-destructive measurements of surface energy in room temperature wafer bonding. J. Electrochem. Soc. 147, 2343–2346 (2000)

Stengl, R., Ahn, K.-Y., Gösele, U.: Bubble-free silicon wafer bonding in a non-cleanroom environment. Jpn. J. Appl. Phys. 27, L2364–L2366 (1988)

Takagi, H., Kikuchi, K., Maeda, R., Chung, T.R., Suga, T.: Surface activated bonding of silicon wafers at room temperature. Appl. Phys. Lett. 68, 2222–2224 (1996)

Tong, Q.-Y., Kim, W.J., Lee, T.-H., Gösele, U.: Low vacuum wafer bonding. Electrochem. Solid State Lett. 1, 52–53 (1998)

Wada, H., Sasaki, H., Kamijoh, T.: Wafer bonding technology for optoelectronic integrated devices. Solid Stat. Electron. 43, 1655–1663 (1999)

Widdershoven, F.P., Haisma, J., Naus, J.: Boron contamination and antimony segregation at the interface of directly bonded silicon wafers. J. Appl. Phys. 68, 6253–6358 (1990)

Yamaguchi, H., Fujino, S., Hattori, T., Hamakawa, Y.A.: Superjunction by wafer direct bonding. Jpn. J. Appl. Phys. 34, L199–L202 (1995)

Zazzera, L.A., Moulder, J.F.: XPS and SIMS study of anhydrous HF and UV/ozone-modified silicon (100) surfaces. J. Electrochem. Soc. 136, 484–491 (1989)

Zhou, Y., Zhu, A.H., Lo, Y.-H., Ji, C., Bashar, S.A., Allerman, A.A., Hargett, T., Sieg, R., Choquette, K.D.: Oxide-defined GaAs vertical cavity surface-emitting lasers on Si substrates. IEEE Photon. Lett. 12, 110–112 (2000)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Hammadi, O.A., Naji, N.E. Electrical and spectral characterization of CdS/Si heterojunction prepared by plasma-induced bonding. Opt Quant Electron 48, 375 (2016). https://doi.org/10.1007/s11082-016-0647-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11082-016-0647-2