Abstract

The saturation of complementary metal–oxide–semiconductor (CMOS) technology in terms of area and power efficiency has given rise to advanced research on nanodevices. Memristors and their switching properties facilitate the implementation of various combinational logics and neural networks by potential replacement of the existing CMOS technology for edge computing devices. This work presents the design, implementation, and performance evaluation of memristor-based combinational logic circuits including adders, subtractors, and decoders via MATLAB Simulink and Cadence Virtuoso. In this work, we propose an optimized design of memristor-based combinational logic circuits and conduct a comparative study with the conventional method. The proposed memristor model is thoroughly validated experimentally for a high-density Y2O3-based memristive crossbar array and shows ultralow values in device-to-device and cycle-to-cycle variability. The power calculated from these circuits is reduced by more than 90% as compared to conventional CMOS technology implemented in Cadence Virtuoso. Moreover, the number of components utilized in the memristor-based logic circuits is significantly reduced in comparison to existing CMOS technology, which makes it more area-efficient and opens new avenues for the design and implementation of complex logic circuitry in few-micrometer scale.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Many contemporary computer workloads, including artificial intelligence (AI) and scientific computing techniques, require the parallel processing of a large amount of data. Since the memory and computation units are separate, a significant amount of operational time and energy is needed for data transfer in the von Neumann architecture [1]. This serves as a basis for the majority of computer systems and is fairly inefficient for data-intensive computing [2]. Large-scale parallel designs, such as graphic processing units (GPUs), or specialized systems such as tensor processing units (TPU) have been implemented in an attempt to address this memory constraint in computing systems [3]. Currently, metal–oxide–semiconductor field-effect transistor (MOSFET) and complementary metal–oxide–semiconductor (CMOS) technology are the two main pillars providing advanced support in digital electronics and are the foundation of the mainstream computational paradigm [4].

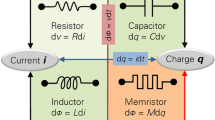

Combinational logic circuits are widely utilized in several applications including calculators, digital measuring instruments, computers, digital processing, control automation, industrial processing, and digital communications [5]. However, current CMOS technology is limited according to Moore’s law, and hence, new technology with low power and small area is being sought. A memristor is a two-terminal device which is a well-known technology, and its many advantages include electrical programmability [6], its nanoscale size [7], precise tunability [8], and ability to function as a resistive element on a variety of scales [9]. It is fully capable of performing both logic and memory operations in an efficient way [10], displaying low energy and power consumption and multibyte storage capability [11]. Additionally, memristors use pulse-based operation and adjustable resistance which are preferred for regulating the synaptic weights in neuromorphic computing processes. Memristor-aided logic (MAGIC) and material implication (IMPLY) memristor logic are the two aspects of pure memristor-based logic circuits [12]. However, due to structural complications, MAGIC cannot perform cascade connections between multiple logic gates. In IMPLY, operational time increases, as it requires multiple operation steps in the circuit [13]. Recently, to improve the logical state and reduce the power consumption, buffers are used which increase the required chip area [14]. By utilizing memristors in a circuit, one can easily address the limitations of current technology in terms of speed, energy, power and area to design efficient combinational logic gates. Several studies [13, 15, 16] have reported the implementation of “AND” and “OR” logic gates by utilizing memristor circuits or a combination of CMOS-memristor logics. In this paper, several combinational logic gates are implemented using a memristor model as proposed in Kumar et al. [17], which is inspired by the experimental results of Y2O3-based memristors and memristive crossbar arrays (MCAs) that display ultralow device-to-device (D2D) and cycle-to-cycle (C2C) variability [18]. The proposed analytical model effectively shows the digital transition between the high-resistance state (HRS) and low-resistance state (LRS) and vice versa.

This paper is organized as follows: Section 2 introduces the methodology, which includes the analytical memristor model with digital behavior in its current–voltage response, and also outlines the design procedure for various combinational logic gates. Section 3 presents the implemented combinational logic circuits and their results with logic truth tables. Section 4 describes the performance evaluation of the implemented logic circuits by considering various performance parameters such as number of components, area and utilized power. Section 5 summarizes the conclusion and future scope of the research work.

2 Analytical model

Nowadays, memristors are used in many applications such as memory [19], synapses [20], neuromorphic computing [21], deep neural networks [22], and logic gates [23]. Owing to their broad use in logic gates, the logic states “0” and “1” are represented by the switching states, i.e., HRS and LRS, of the memristor, respectively. In this work, an analytical model of a memristor is utilized in MATLAB Simulink and Cadence Virtuoso to verify its current–voltage (I–V) characteristics. The model is then integrated with other circuit components to perform logic operations with various combinational logic gates including half adder, full adder, half subtractor, full subtractor, and two-input and three-input decoders. A detailed comparison of these logic gates with existing CMOS technology is also discussed.

2.1 Memristor model

The proposed nonlinear model [17] is applicable to both unipolar and bipolar memristive systems. Here, Eq. (1) shows the relationship between current and voltage (I–V) of the memristor.

The parameters a1 and a2 show the effects of the state variable on the device current for positive and negative applied voltages, respectively. The fitting parameters b1 and b2 define the slope of conductance in I–V characteristics, α1 and α2 denote the hysteresis loop area controlling parameters, and the state variable is represented by w. The net electronic barrier of the memristive device is denoted by the parameters \(\chi\) and γ, and the applied input voltage is Vi(t).

Here, Eq. (2) defines the piecewise window function (\(f\left(w\right)\)) which ensures that w Є [0,1]. Equation (3) illustrates the state variable derivative in the time domain, with A and m denoting the effect of the input voltage on the state variable.

However, in the past several years, different memristor models have been reported [7, 24, 25] which have shown compatibility on different programming platforms. Here, Table 1 effectively shows the comparison and fundamental difference between our proposed model and other reported models [7, 24, 25]. It should be noted that the piecewise window function utilized offers better controllability over the nonlinear analytical model in terms of bipolar resistive switching, effectively applicable for a lower input voltage window, utilizes minimum parameters as a degree of freedom, and offers better tunability in device conductance which further enhances the ability of the proposed analytical model to perform both analog and digital logic operations. Furthermore, its experimental validation proves its real-time application with lower variability as added superior advantages in its novelty, as compared to the reported data in the literature [17].

2.2 Design procedure

To design and implement the various combinational circuits, the aforementioned nonlinear analytical model is used to create a memristor element on MATLAB Simulink and Cadence Virtuoso. The sinusoidal input voltage waveform is utilized to obtain the pinched hysteresis resistive switching response with perfect zero crossing at the origin. Here, it should be noted that some valid modifications have been incorporated into the parameter values to obtain the perfect digital behavior as compared to analog response, as reported previously [17] and outlined in Table 2.

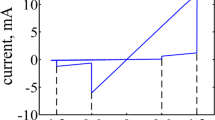

Further, to investigate the memristive behavior with digital pulse, a rectangular voltage input pulse with an amplitude of +2 and 0 V is applied. Here, the amplitude of +2 V is referred to as logic “1” and 0 V is referred to as logic “0”. Figure 1 shows the simulated output waveform for the digital logic design, and the pinched hysteresis loop (Fig. 1d) in the I–V characteristics clearly shows the abrupt transition from HRS to LRS and vice versa, which confirms the digital behavior of the memristor and makes it more suitable for digital logic design. Here, it should be noted that in the bipolar memristive behavior, the SET (“ON”) state appears at the positive voltage side while the RESET (“OFF”) state appears at the negative voltage side. The resistance values of HRS and LRS are 0.526 MΩ and 0.0527 MΩ, respectively. To design and simulate the inverter and other combinational circuits, 180-nm CMOS technology is utilized along with a memristor. Dong et al. [26] reported that using the memristor-CMOS hybrid logic circuit efficiently reduced the circuit delay.

3 Circuit implementation, results and discussion

As discussed earlier, the MATLAB Simulink tool is utilized to design and implement all the combinational logic circuits, where the memristor works as a switching device and “ON” and “OFF” according to the input voltage amplitude. The output current of the memristor is denoted by Iout. Here, Eq. (4) shows the calculation approach adopted for logic “1” and “0”.

Equations (5a) and (5b) show the Boolean expressions, while Table 3 depicts the combined truth table for a half adder and half subtractor, respectively. Figure 2 shows the designed circuit layouts in MATLAB Simulink for the half adder (Fig. 2a) and half subtractor (Fig. 2b). Here, to perform the logic operations, two different input voltages, +2 and 0 V, are applied with different duty cycles of 0.5 and 0.25 to create the input logic ({0,0}, {0,1}, {1,0}, {1,1}). The output logic combinations are presented in Table 3. Table 4 shows the design process flow during logic computation in the case of half adder. Figure 3 shows both input voltage pulses (Fig. 3a), sum and carry outputs (Fig. 3b) and difference and borrow (Fig. 3c) for a half adder and half subtractor, respectively.

To design and implement a full adder circuit, two half adders and one additional “OR” gate is utilized, where the “OR” gate is used for carry output, as depicted in Fig. 4a. Similarly, for the full subtractor, two half subtractors and one additional “OR” gate are used, as shown in Fig. 4b. Here, three different duty cycles of 0.5, 0.25, and 0.125 are imposed on the designed circuit to obtain the logic inputs ({000}, {001}, {010}, {011}, {100}, {101}, {110}, {111}). The output logic combinations are presented in Table 5. Figure 5 shows the three input voltage pulses (Fig. 5a), sum and carry outputs (Fig. 5b), and difference and borrow (Fig. 5c) for full adder and full subtractor, respectively.

For the 2:4 decoder circuit implementation, a similar input voltage scheme is applied as utilized in the half adder and half subtractor. Here, two 1-bit inputs are applied to the four memristor-based “AND” gates to perform the decoder operation according to Eqs. (7a–7d). Figure 6 shows the circuit layout implemented for the 2:4 decoder, while Fig. 7 shows the results for the 2:4 decoder. Table 6 shows the truth table for the 2:4 decoder circuit. Further, to extend the functionality, a 3:8 decoder is also implemented, as shown in Fig. 8, and the results are displayed in Fig. 9 while Table 7 shows the truth table of 3:8 decoder.

4 Performance evaluation

In this section, a performance evaluation for the implemented combinational circuits is presented. The performance evaluation is based on the various critical circuit parameters such as power utilized, circuit area, and the total number of components used in the respective circuit design. By considering the aforementioned parameters, here we discuss each one in detail.

4.1 Component comparison

Here, Table 8 shows a comparison between the number of memristors and CMOS inverters used in memristor-based combinational logic gates with conventional CMOS technology. It is observed that the memristor-based combinational logic circuits require a significantly smaller number of components than that required for only transistor-based conventional circuits.

As observed from the comparison in Table 8 the memristor-based logic shows a significant improvement in the utilized components to implement the combinational circuits. Importantly, the utilized circuit power and area are directly related to the number of utilized components in the logic circuits.

4.2 Area calculation

The area of the memristor-based combinational logic circuits has been calculated using layout calculation rules, as reported by Kang et al. [27]. Here, the area of the memristor is considered as 9 nm2 [28], while the area of MOSFET is calculated as 1.06 µm2. The total area of the memristor is much smaller than the total area covered by the MOSFET, and the memristor can be implemented on a polysilicon layer of the MOSFET. Therefore, 1000 memristors can be fabricated on the same chip-level area as occupied by a single CMOS [16, 29]. Figure 10 shows a comparison of the area of the memristor-based circuits and CMOS-based circuits, in which memristor-based circuits occupy significantly less area due to their nanometer scale as compared to CMOS.

4.3 Power comparison

The power consumption of the circuits is another important parameter when designing the circuit. For the memristor-based combinational circuits, power is calculated by integrating the product of the output voltage and the summation of the input currents of the circuit. Figure 11 shows the worst-case power comparison between memristor-based combinational logic and CMOS-based combinational logic circuits. Here, it should be noted that the CMOS-based combinational logic circuits are implemented in Cadence Virtuoso by adopting 180-nm CMOS technology. As observed from the calculation, the memristor-based logic circuits consume much less power during operation than CMOS-based logic, which further strengthens the argument for using the memristor technology for various logic applications.

5 Conclusion and future outlook

In this work, we have utilized our proposed nonlinear memristor analytical model to design and implement various combinational logic circuits via MATLAB Simulink and Cadence Virtuoso. The model is validated based on experimental demonstration using low-variance in-house-fabricated memristors and MCA. The resistive switching response obtained shows clear digital behavior, which makes it a suitable candidate for digital logic design. Moreover, the memristor-based combinational logic circuits show significantly better performance in terms of the number of components, total circuit chip area, and power utilized as compared to those for the existing CMOS-based combinational logic circuits wherein 180-nm CMOS technology has been used. Therefore, the designed circuits are highly reliable for use in future complex circuits and integrated circuits. This work can be further extended by designing complex digital circuits such as flip-flops, and counters. Furthermore, the proposed methodology and circuit design approach can be useful for implementing power- and area-efficient complex circuitry for amplifiers, oscillators, and neuromorphic networks.

Data availability

The paper has no associated data.

References

Neumann, J.V.: First draft of a report on the EDVAC. IEEE Ann. Hist. Comput. 15(4), 27–75 (1993). https://doi.org/10.1109/85.238389

Zidan, M.A., Strachan, J.P., Lu, W.D.: The future of electronics based on memristive systems. Nat. Electron. 1(1), 22–29 (2018). https://doi.org/10.1038/s41928-017-0006-8

Jouppi, N.P. et al.: In-data centre performance analysis of a tensor processing unit. In: Proceedings of the 44th Annul International Symposium on Computer Architecture (ISCA), pp. 1–12 (2017)

Nikonov, D.E., Young, I.A.: Overview of beyond-CMOS devices and a uniform methodology for their benchmarking. Proc. IEEE 101(12), 2498–2533 (2013). https://doi.org/10.1109/JPROC.2013.2252317

Nabulsi, M., Al-Husainy, M.: Using combinational circuits for control purposes. J. Comput. Sci. 5, 507 (2009). https://doi.org/10.3844/jcssp.2009.507.510

Chua, L.O.: Memristor-the missing circuit element. IEEE Trans. Circuit Theory 18(5), 507–519 (1971). https://doi.org/10.1109/TCT.1971.1083337

Strukov, D.B., Snider, G.S., Stewart, D.R., Williams, R.S.: The missing memristor found. Nature 453(7191), 80–83 (2008). https://doi.org/10.1038/nature06932

Stathopoulos, S., Khiat, A., Trapatseli, M., Cortese, S., Serb, A., Valov, I., Prodromakis, T.: Multibit memory operation of metal-oxide Bilayer memristors. Sci. Rep. 7(1), 17532 (2017). https://doi.org/10.1038/s41598-017-17785-1

Duan, S., Hu, X., Wang, L., Li, C.: Memristor-based RRAM with applications. Sci. China Inf. Sci. 55, 1446–1460 (2012). https://doi.org/10.1007/s11432-012-4572-0

Kvatinsky, S., Satat, G., Wald, N., Friedman, E.G., Kolodny, A., Weiser, U.C.: Memristor-based material implication (IMPLY) logic: design principles and methodologies. IEEE Trans. Very Large-Scale Integr. (VLSI) Syst. 22(10), 2054–2066 (2014). https://doi.org/10.1109/TVLSI.2013.2282132

Khalid, M.: Review on various memristor models, characteristics, potential applications, and future works. Trans. Electr. Electron. Mater. 20, 289 (2019). https://doi.org/10.1007/s42341-019-00116-8

Kvatinsky, S., et al.: MAGIC-memristor-aided logic. IEEE Trans. Circuits Syst. II Express Briefs 61(11), 895–899 (2014). https://doi.org/10.1109/TCSII.2014.2357292

Liu, G., Shen, S., Jin, P., Wang, G., Liang, Y.: Design of memristor-based combinational logic circuits. Circuits Syst. Signal Process. 40, 1–22 (2021). https://doi.org/10.1007/s00034-021-01770-1

Mandal, S., Sinha, J., Chakraborty, A.: Design of memristor -CMOS based logic gates and logic circuits. In: 2nd International Conference on Innovations in Electronics, Signal Processing and Communication (IESC), Shillong, India, pp. 215–220 (2019). https://doi.org/10.1109/IESPC.2019.8902355.

Gao, C., Li, T., Wang, T., Cao, X.: Memristor-based logic gate circuit. In: 2020 IEEE 3rd International Conference on Computer and Communication Engineering Technology (CCET), Beijing, China, pp. 330–333 (2020). https://doi.org/10.1109/CCET50901.2020.9213140.

Singh, T.: Hybrid Memristor-CMOS (MeMOS) based logic gates and adder circuits. arXiv [cs.ET], 1506, pp. 1–11 (2015)

Kumar, S., Agrawal, R., Das, M., Jyoti, K., Kumar, P., Mukherjee, S.: Analytical model for memristive systems for neuromorphic computation. J. Phys. D Appl. Phys. (2021). https://doi.org/10.1088/1361-6463/ac07dd

Kumar, S., Agarwal, A., Mukherjee, S.: Electrical performance of large-area Y2O3 memristive crossbar array with ultralow C2C variability. IEEE Trans. Electron Devices 69(7), 3660–3666 (2022). https://doi.org/10.1109/TED.2022.3172400

Kumar, A., Das, M., Garg, V., Sengar, B.S., Htay, M.T., Kumar, S., Kranti, A., Mukherjee, S.: “Forming-free high-endurance Al/ZnO/Al memristor fabricated by dual ion beam sputtering. Appl. Phys. Lett. 110(253509), 1–5 (2017). https://doi.org/10.1063/1.4989802

Kumar, S., Agrawal, R., Das, M., Kumar, P., Mukherjee, S.: Analytical modeling of Y2O3-based memristive system for synaptic applications. J. Phys. D Appl. Phys. 53, 305101 (2020). https://doi.org/10.1088/1361-6463/ab810e

Kumar, S., Kumbhar, D.D., Park, J.H., Kamat, R.K., Dongale, T.D., Mukherjee, S.: Y2O3-based crossbar array for analog and neuromorphic computation. IEEE Trans. Electron Devices 70(2), 473–477 (2023). https://doi.org/10.1109/TED.2022.3227890

Yi, S., Kendall, J.D., Williams, R.S.: Activity-difference training of deep neural networks using memristor crossbars. Nat. Electron. 6, 45–51 (2023). https://doi.org/10.1038/s41928-022-00869-w

Vourkas, I., Sirakoulis, G.C.: Emerging memristor-based logic circuit design approaches: a review. IEEE Circuits Syst. Mag. 16(3), 15–30 (2016). https://doi.org/10.1109/MCAS.2016.2583673

Yang, J., Pickett, M., Li, X., Ohlberg, D.A.A., Stewart, D.R., Williams, R.S.: Memristive switching mechanism for metal/oxide/metal nanodevices. Nat. Nanotechnol. 3, 429–433 (2008). https://doi.org/10.1038/nnano.2008.160

Yakopcic, C., Taha, T.M., Subramanyam, G., Pino, R.E., Rogers, S.: A memristor device model. IEEE Electron Device Lett. 32, 1436–1438 (2011). https://doi.org/10.1109/LED.2011.2163292

Dong, Z., Qi, D., He, Y., Xu, Z., Hu, X., Duan, S.: Easily cascaded memristor-CMOS hybrid circuit for high-efficiency Boolean logic implementation. IET Circuit Devices & Syst. 11(2), 123–134 (2017). https://doi.org/10.1142/S0218127418501493

Kang, S.M., Leblebici, Y.: Cmos digital integrated circuits: analysis and design”, McGraw Hill, ISBN: 978–0–07–246053–7, (1995)

Kumar, G., Datta, K.: Design of digital functional blocks using hybrid memristor structures. In: TENCON 2015–2015 IEEE Region 10 Conference, pp. 1–5 (2015). https://doi.org/10.1109/TENCON.2015.7372883.

Nawaria, M., Kumar, S., Gautam, M.K., Dhakad, N.S., Singh, R., Singhal, S., Kumar, P., Vishvakarma, S.K., Mukherjee, S.: Memristor-inspired digital logic circuits and comparison with 90-/180-nm CMOS technologies. IEEE Trans. Electron Devices (2023). https://doi.org/10.1109/TED.2023.3278625

Acknowledgements

Shruti Sandip Ghodke would like to thank Narendra Singh Dhakad for providing assistant on the Cadence Virtuoso platform to evaluate the 180-nm CMOS technology outcomes. This work is partially supported by CSIR (No. 22(0841)/20/EMR-II) and JSPS Invitational Fellowship award (ID: S23062).

Funding

The authors have not disclosed any funding.

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

Conflict of interest

The authors declare no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Ghodke, S.S., Kumar, S., Yadav, S. et al. Combinational logic circuits based on a power- and area-efficient memristor with low variability. J Comput Electron 23, 131–141 (2024). https://doi.org/10.1007/s10825-023-02117-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-023-02117-6