Abstract

Given the special place of hybrid logic circuits such as all-optical full adders in next-generation digital systems, a new kind of these structures using two-dimensional (2D) photonic crystals (2D-PC) is designed and simulated herein. The proposed structure is made of a hexagonal nanoring resonator (NRR), a coupling rod, and several waveguides. In this all-optical full adder, the mechanism of the interference effect in the PCs is used to simplify and minimize the structure. To make the structure flexible, the radius of the dielectric rod in the whole structure and the NRR are considered based on a lattice constant of 0.2a and 0.04a, respectively. The structure is operated at a wavelength of 1550 nm, considering the value of the power entering the waveguides and that exiting the Carry and Sum ports. To analyze the all-optical full adder, the plane-wave expansion method and finite-difference time-domain method are applied respectively to calculate the bandgap diagram and obtain the transmission and propagation of the optical field. In the proposed structure, the contrast ratio at the Carry and is been investigated in a unique and novel way, yielding values of 10.68 and 9.03 dB, respectively. In addition, the maximum and minimum response time for the Carry and Sum are obtained as 1.6 and 0.75 ps, respectively. The total footprint of the structure is about 183 µm2. Due to its ultracompact size, low power consumption, fast response time, and simple structure, this all-optical full adder is suitable for use in low-power optical integrated circuits.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Advances resulting from new technologies and the high speed of light are important factors affecting the development of integrated optical devices. This approach will gradually result in the replacement of classical electronic systems by new-generation optical systems. Considering the importance of this issue, the rapid transfer, receipt, storage, and processing of information and most importantly all-optical logic computations using new-generation optical devices are the most important factors contributing to the realization of photonic integration technology and thus optical integrated circuits (OICs) [1]. In this context, new photonic materials with micro–nanometer sizes such as graphene, plasmon, and photonic crystals (PC) [2,3,4], which offer unique capabilities including the modulation of photon emission and control modes, and the diffusion and distribution of light in the structure, are considered to be significantly important for the development of such technologies. Moreover, among the mentioned photonic materials, PCs with aperiodic structure have attracted particular attention due to their range of photonic bandgap (PBG) [5], which plays a critical role in directing and controlling light, as well as their unique features such as small size and the ability to process and transfer data quickly, combined with a simple design that facilitates their construction and is considered to be one of the basic requirements regarding the implementation of OICs. Accordingly, PCs can be used in the design and implementation of various optical devices, including optical waveguides [6, 7], optical filters [8, 9], optical sensors [10,11,12], multiplexer/demultiplexers [13,14,15,16,17], optical converters [18], lasers [19], optical power dividers [20], optical logic gates [21,22,23,24,25,26], etc.

One of the most important and practical types of photonic structure, namely all-optical logic gates based on PCs, being considered to be one of the basic requirements for new-generation OICs, is designed herein. When all-optical logic gates are designed, parameters such as the contrast ratio (CR) [27], the response time to the input signal, the applicability, the output power, and the bit rate (BR) [28] are evaluated and compared, and the efficiency of the gate thereby determined. Optical logic gates based on PCs can be designed using three main mechanisms, namely the nonlinear Kerr effect, the self-collimation effect, and the interference effect in PCs. Herein, to optimize these parameters, the interference effect of waves in PCs is used to facilitate the design and implementation. The proposal is for an integrated structure which is not composed of different logic gates, resulting in a very compact footprint compared with previously proposed full adders. Also, the optical power intensity required at the input ports is lower than for previously proposed structures [21, 27, 29,30,31]. This approach also leads to the construction of a smaller structure with a higher CR than when using the other two mechanisms. Using the current method, the structure operates such that, if the light waves have a phase difference of about 2nπ (n = 1, 2, 3, etc.), constructive interference will occur and the logic gate output will be 1 or ON. However, if the phase difference between the waves is about (2n + 1)π with n = 1, 2, 3, etc., destructive interference will occur and the logic gate output will be 0 or OFF. Accordingly, using the phase difference between the waves, the output waves can be controlled using the structure of PC logic gates and a desired structure designed. For the proposed structure, the response time is calculated to be 1.1 ps while the CR for the Carry and Sum ports is 10.68 and 9.03 dB, respectively.

In general, various numerical methods can be used to analyze PCs, each having its own advantages and disadvantages. Such numerical methods can be divided into two general categories, namely those carried out in the frequency and time domain. Due to its compatibility with parallel processing and data extraction over a wide range of wavelengths, the finite-difference time-domain (FDTD) method [32] is applied herein to simulate the structure and derive the output spectrum results. Moreover, the optical devices are designed and constructed using PCs based on the range of the PBG and the plane-wave expansion (PWE) method. The PWE method has been applied to separate transverse electric (TE) and transverse magnetic (TM) modes and to calculate the frequency eigenvalues and PBG of the proposed structure [33].

The rest of this manuscript was organized as follows: Sect. 2 discusses the all-optical full-adder block and the design procedure for the proposed structure, while the simulation results are presented and discussed in Sect. 3. Finally, conclusions are drawn in Sect. 4.

2 All-optical full-adder block

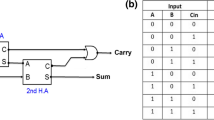

Hybrid logic circuits are currently receiving much attention in the field of digital systems. These types of logic circuit generally have different inputs and outputs and can be designed and constructed using various gates. The full adder is among these important logic circuits. The structure of a full adder includes three inputs and two outputs. The two inputs A and B of this circuit represent the two most significant bits of the whole full adder, while the third input C represents the carry bit resulting from the least significant position. The two outputs in this circuit are denoted as the Sum and Carry, where the Sum represents the value of the least significant sum and the binary output variable Carry the output carry. The truth table of the whole binary full adder with its possible inputs is presented in Table 1, according to which the different modes of 1 or ON in the Sum and Carry outputs can be expressed as follows:

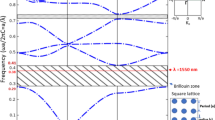

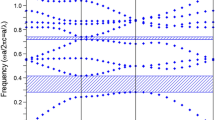

In this work, 2D PC structures are used to design and simulate an all-optical full adder for use in next-generation digital systems. For this purpose, 23 dielectric rods along the x-axis and 21 dielectric rods along the z-axis are used. For design simplicity and to use silicon technology, the dielectric rods were made of silicon with a refractive index of nr = 3.46, placed in an air background with refractive index of ns = 1. The radius of the dielectric rods used was R = 0.2a, while the lattice constant was a = 630 nm, and the hexagonal lattice constant was selected. According to the desired structural parameters, the final size of the structure is estimated to be about 183 µm2. To take advantage of the unique properties of PCs for controlling and directing light in the design and construction of optical devices, the first priority is to analyze the range of the PBG and the amount of light scattering in these structures. The PWE method is thus used to determine the range of the PBG. According to the results obtained for the amount of light scattering within the given structure, the structure has three PBG ranges for the TE and TM modes (Fig. 1). The first PBG for the TM mode lies in the range of 0.285 ≤ a/λ ≤ 0.460, and the second PBG for the TM mode lies in the range of 0.575 ≤ a/λ ≤ 0.595, being equal to 1369 nm ≤ λ ≤ 2210 nm and 1058 nm ≤ λ ≤ 1095 nm, respectively. In addition, the PBG for the TE mode lies in the range of 0.830 ≤ a/λ ≤ 0.890, which is equal to 707 nm ≤ λ ≤ 759 nm. According to the wavelength ranges obtained for the proposed structure, the first PBG for the TM mode is considered to be optimal, due to its wide bandwidth.

The basic structure of the desired all-optical full adder is designed based on the NRR and using the interference effects between the waves. The structure consists of 23 and 21 dielectric rods in the x- and z-direction, respectively. The proposed NRR is made of a 2D hexagonal lattice of silicon. The structure of the given NRR used in the design of the full adder is shown in Fig. 2. This basic structure comprises a square with diameter of 0.5 and rotation of 45° within a hexagon. The length of the sides of the hexagon is equal to a, while the diameter of the dielectric rods constituting the structure is equal to 0.08a. The length of the sides of the square is 0.353, while the radius of the dielectric rods constituting it is 0.04a.

The structure of the proposed all-optical full adder is shown in Fig. 3. In this structure, to create a full adder with three input ports (A, B, and C) and two output ports (Sum and Carry), five waveguides, four 120° bends, and a hexagonal NRR with a coupling rod are used to control and guide the light to implement the different logic states. The input Gaussian pulses enter the structure from each of the ports A, B, and C through the waveguides W1, W2, and W3, and depending on the interference between the waveguides and the hexagonal NRR, the output power in the various states of the SUM and Carry outputs exits through W4 and W5. The proposed NRR placed between the waveguides is described by parameters such as the refractive index and radius of the coupling rods, the radius of the internal rods, the relative positioning of the rods, the output wavelength range, the output power, and the quality coefficient of the output channel. The values of the main parameters and materials properties used in the simulations are presented in Table 2.

3 Results and discussion

In the proposed structure, depending on the power Pin entering waveguides W1, W2, and W3 from the input ports A, B, and C, the power exiting the Carry and Sum output ports varies between 0 and 1. When analyzing the different logic states at the outputs obtained from the simulations, powers between 0% and 30% correspond to logic state 0 while those between 70% and 100% correspond to logic state 1. Thus, according to the electromagnetic field distribution profile shown in Fig. 4a, when the power entering waveguides W1 and W2 is 0 and the power entering waveguide W3 is Pin, or in other words, A = 0, B = 0, and C = 1, the light coupled to the NRR is directed to the Sum output, and the Carry and Sum ports adopt logic state 0 and 1, respectively. In this case, the normalized power at a wavelength of 1550 nm for the Sum and Carry outputs is equal to 86% Pin and 6% Pin, respectively. These results are also shown in Fig. 4b, c.

According to Fig. 5a, when the power entering waveguides W1 and W3 is 0 but the power entering waveguide W2 is Pin, i.e., A = 0, B = 1, and C = 0, the Carry and Sum ports adopt the logic state 0 and 1, respectively, considering the presence of a single pulse coupled to the NRR. In this case, the normalized power at a wavelength of 1550 nm for the Sum and Carry output is equal to 89% Pin and 7% Pin, respectively. These results are also shown in Fig. 5b, c.

According to Fig. 6a, when the power entering waveguides W2 and W3 is Pin but the power entering waveguide W1 is 0, i.e., A = 0, B = 1, and C = 1, the Carry and Sum ports adopt logic state 1 and 0, respectively, considering the presence of two Gaussian pulses coupled simultaneously to the NRR. In this case, the normalized power at a wavelength of 1550 nm for the Sum and Carry outputs is 85% Pin and 5.5% Pin, respectively. These results are also shown in Fig. 6b, c.

According to Fig. 7a, when the power entering waveguides W2 and W3 is 0 but the power entering waveguide W1 is Pin, i.e., A = 1, B = 0, and C = 0, similar to the two first cases, the Carry and Sum ports adopt logic state 0 and 1, respectively, considering the presence of a single pulse coupled to the NRR. In this case, the normalized power at a wavelength of 1550 nm for the Sum and Carry outputs is equal to 92% Pin and 4.5% Pin, respectively. These results are also shown in Fig. 7b, c.

According to Fig. 8a, when the power entering waveguides W1 and W3 is Pin and the power entering waveguide W2 is 0, i.e., A = 1, B = 0, and C = 1, the Carry and Sum ports adopt logic state 1 and 0, respectively, considering the presence of two Gaussian pulses coupled to the NRR. In this case, the normalized power at a wavelength of 1550 nm for the Sum and Carry outputs is equal to 10.5% Pin and 85% Pin, respectively. These results are also shown in Fig. 8b, c.

According to Fig. 9a, when the power entering waveguides W1 and W2 is Pin but the power entering waveguide W3 is 0, i.e., A = 1, B = 1, and C = 0, the Carry and Sum ports adopt logic state 1 and 0, respectively, considering the presence of the two Gaussian pulses coupled to the NRR. In this case, the normalized power at a wavelength of 1550 nm for the Sum and Carry outputs is equal to 9.7% Pin and 86% Pin, respectively. These results are also shown in Fig. 9b, c.

Finally, as shown in Fig. 10a, when the power entering waveguides W1, W2, and W3 is equal to Pin, i.e., A = 1, B = 1, and C = 1, the Carry and Sum ports adopt logic state 1, considering the presence of the three Gaussian pulses coupled to the NRR. In this case, the NRR acts as a divider and the normalized power at a wavelength of 1550 nm for the Sum and Carry outputs is equal to 84.1% Pin and 82% Pin, respectively. These results are also shown in Fig. 10b, c.

Note that, if the power entering waveguides W1, W2, and W3 is 0, there will be no output power due to the lack of coupling of the optical pulse to the NRR, and the Sum and Carry ports will adopt logic state 0.

Table 3 presents the truth table describing the performance of the proposed full adder, including the various logic states, the power sent to each input and waveguide, the power received by each of the Sum and Carry outputs and their logic states, as well as the response time in each of these states. According to these results, the response time of the proposed all-optical full-adder structure varies from 0.75 to 1.6 ps. Another important parameter in the design of all-optical logic gates is the contrast ratio, so the contrast ratio of 0 and 1 is also presented for each logic level. According to the following equation, the higher the power difference level between these two logic states, the better the performance of the logic gate [27].

where Pon is the power in logic state 1 or ON state and Poff is the power in logic state 0 or OFF state. According to this equation, the CR for the Sum and Carry outputs is 9.03 and 10.68 dB, respectively, for the proposed structure.

Table 4 compares the important parameters of the proposed structure with other (full- and half-adder) logic gates presented in recent years. According to this table, the response time and output CR of the proposed logic gate are highly desirable compared with those of structures presented in recent years. Additionally, the structure proposed herein is highly applicable due to the use of the interference principle between the waveguides and NRR, its very small structural size, as well as not requiring a change in the refractive index of materials. The maximum output delay of the proposed structure is 1.1 ps, which is very good compared with structures proposed in recent years.

4 Conclusions

We propose and design an all-optical full adder using a hexagonal NRR and five waveguides. In this design, the NRR between the waveguides controls the output parameters, depending on the refractive index and radius of the internal coupling rods as well as their relative positioning. The input Gaussian pulse enters the structure through three waveguides (W1, W2, and W3), and based on the principle of interference between the waveguides and NRR, the output power exits in various states from the output ports. Additionally, the management of the power entering the waveguides W1, W2, and W3 controls the power exiting the Carry and Sum ports between 0 and 1, corresponding to the OFF and ON states. The response time of the proposed full-adder structure varies from 0.75 to 1.6 ps. The maximum output delay of the proposed structure is 1.6 ps, and the CR for the Carry and Sum ports is 10.68 and 9.03 dB, respectively. To optimize the output parameters of the proposed structure, the interference effect in the PC is used, thereby simplifying its design.

References

Razi, S., Ghasemi, F.: Tunable graphene based one dimensional photonic crystal with applications in terahertz optical integrated circuits. Physica B 566, 77–85 (2019)

Chen, Y.-T., et al.: Surface plasmons coupled two-dimensional photonic crystal biosensors for Epstein–Barr virus protein detection. Sens. Actuators B Chem. 291, 81–88 (2019)

Jalali Azizpour, M.R., et al.: All-optical ultra-fast graphene-photonic crystal switch. Crystals 9(9), 461 (2019)

Alias, M.S., et al.: Review of nanophotonics approaches using nanostructures and nanofabrication for III-nitrides ultraviolet-photonic devices. J. Nanophoton. 12(4), 043508 (2018)

Karkhanehchi, M.M., Parandin, F., Zahedi, A.: Design of an all optical half-adder based on 2D photonic crystals. Photon Netw. Commun. 33(2), 159–165 (2017)

Shu, J., Dang, S.: Slow light in a slot photonic crystal waveguide with asymmetric dielectric rods. In: 9th International Symposium on Advanced Optical Manufacturing and Testing Technologies: Micro-and Nano-Optics, Catenary Optics, and Subwavelength Electromagnetics. International Society for Optics and Photonics (2019)

Otmani, H., et al.: Simulation of magneto-optical properties of magnetic photonic crystal waveguides. J. Nanophoton. 13(2), 026002 (2019)

Seifouri, M., Fallahi, V., Olyaee, S.: Ultra-high-Q optical filter based on photonic crystal ring resonator. Photon Netw. Commun. 35(2), 225–230 (2018)

Fallahi, V., Seifouri, M., Mohammadi, M.: A new design of optical add/drop filters and multi-channel filters based on hexagonal PhCRR for WDM systems. Photon Netw. Commun. 37(1), 100–109 (2019)

Huang, T.: Highly sensitive SPR sensor based on D-shaped photonic crystal fiber coated with indium tin oxide at near-infrared wavelength. Plasmonics 12(3), 583–588 (2017)

Mohammadi, M., Seifouri, M.: Numerical investigation of photonic crystal ring resonators coupled bus waveguide as a highly sensitive platform. Photon. Nanostruct. Fundam. Appl. 34, 11–18 (2019)

Mohammadi, M., Olyaee, S., Seifouri, M.: Passive integrated optical gyroscope based on photonic crystal ring resonator for angular velocity sensing. Silicon 11(6), 2531–2538 (2019)

Palai, G., et al.: Optical MUX/DEMUX using 3D photonic crystal structure: a future application of silicon photonics. Optik 128, 224–227 (2017)

Ooka, Y., et al.: Ultrasmall in-plane photonic crystal demultiplexers fabricated with photolithography. Opt. Express 25(2), 1521–1528 (2017)

Mohammadi, M., Seifouri, M.: A new proposal for a high-performance 4-channel demultiplexer based on 2D photonic crystal using three cascaded ring resonators for applications in advanced optical systems. Opt. Quantum Electron. 51(11), 350 (2019)

Priti, R.B., Liboiron-Ladouceur, O.: A reconfigurable multimode demultiplexer/switch for mode-multiplexed silicon photonics interconnects. IEEE J. Sel. Top. Quantum Electron. 24(6), 1–10 (2018)

Fallahi, V., Mohammadi, M., Seifouri, M.: Design of two 8-channel optical demultiplexers using 2D photonic crystal homogeneous ring resonators. Fiber Integr. Opt. 38(5), 271–284 (2019)

Mehdizadeh, F., et al.: A novel proposal for all optical analog-to-digital converter based on photonic crystal structures. IEEE Photon. J. 9(2), 1–11 (2017)

Li, M., et al.: High-Q 2D lithium niobate photonic crystal slab nanoresonators. Laser Photon. Rev. 13(5), 1800228 (2019)

Sowmiya, M., et al.: Design and analysis of Wilkinson power divider using 2D photonic crystal. In: Materials Science and Engineering Conference Series (2017)

Alipour-Banaei, H., Seif-Dargahi, H.: Photonic crystal based 1-bit Full-adder optical circuit by using ring resonators in a nonlinear structure. Photon. Nanostruct. Fundam. Appl. 24, 29–34 (2017)

He, L., Zhang, W., Zhang, X.: Topological all-optical logic gates based on two-dimensional photonic crystals. Opt. Express 27(18), 25841–25859 (2019)

Lu, Q., et al.: High-speed ultra-compact all-optical NOT and AND logic gates designed by a multi-objective particle swarm optimized method. Opt. Laser Technol. 116, 322–327 (2019)

Vali-Nasab, A.-M., Mir, A., Talebzadeh, R.: Design and simulation of an all optical Full-adder based on photonic crystals. Opt. Quantum Electron. 51(5), 161 (2019)

Maleki, M.J., Soroosh, M., Mir, A.: Improving the performance of 2-to-4 optical decoders based on photonic crystal structures. Crystals 9(12), 635 (2019)

Jiang, J., et al.: Analysis of photonic logic gates based on single hexagonal-lattice photonic crystal ring resonator. J. Nanophoton. 5(1), 053519 (2011)

Swarnakar, S., Kumar, S., Sharma, S.: Performance analysis of all-optical Full-adder based on two-dimensional photonic crystals. J. Comput. Electron. 17(3), 1124–1134 (2018)

Jayabarathan, J.K., Subhalakshmi, G., Robinson, S.: Performance evaluation of two-dimensional photonic crystal based all optical AND/OR logic gates. J. Opt. Commun. (2018)

Geraili, M.R., et al.: A proposal for an all optical Full-adder using nonlinear photonic crystal ring resonators. Optik 199, 163359 (2019)

Cheraghi, F., Soroosh, M., Akbarizadeh, G.: An ultra-compact all optical Full-adder based on nonlinear photonic crystal resonant cavities. Superlattices Microstruct. 113, 359–365 (2018)

Moradi, M., Danaie, M., Orouji, A.A.: Design and analysis of an optical full-adder based on nonlinear photonic crystal ring resonators. Optik 172, 127–136 (2018)

Taflove, A., Hagness, S.C.: Computational Electrodynamics: The Finite-Difference Time-Domain Method. Artech House, Norwood (2005)

Johnson, S.G., Joannopoulos, J.D.: Block-iterative frequency-domain methods for Maxwell’s equations in a planewave basis. Opt. Express 8(3), 173–190 (2001)

Serajmohammadi, S., Alipour-Banaei, H., Mehdizadeh, F.: Proposal for realizing an all-optical half-adder based on photonic crystals. Appl. Opt. 57(7), 1617–1621 (2018)

Rahmani, A., Mehdizadeh, F.: Application of nonlinear PhCRRs in realizing all optical half-adder. Opt. Quant. Electron. 50(1), 30 (2018)

Xavier, S.C., et al.: Design of two-dimensional photonic crystal-based all-optical binary adder. Opt. Eng. 52(2), 025201 (2013)

Seifouri, M., et al.: Ultra-fast and compact all-optical half-adder using 2D photonic crystals. IET Optoelectron. 13(3), 139–143 (2019)

Neisy, M., Soroosh, M., Ansari-Asl, K.: All optical Half-adder based on photonic crystal resonant cavities. Photon Netw. Commun. 35(2), 245–250 (2018)

Acknowledgements

This work was supported by Shahid Rajaee Teacher Training University.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Mohammadi, M., Fallahi, V. & Seifouri, M. Ultracompact all-optical full adders using an interference effect based on 2D photonic crystal nanoring resonators. J Comput Electron 20, 409–418 (2021). https://doi.org/10.1007/s10825-020-01619-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01619-x