Abstract

This paper proposes a terahertz (THz) detector in a 180-nm standard CMOS process. The detector consists of a square loop antenna and an NMOS transistor. The antenna has two feed ports. One is connected to the source of the transistor and the other is grounded to provide the source a dc ground. To improve the power transfer efficiency between the antenna and the transistor, impedance matching between them is needed. It is concluded that in order to increase the voltage responsivity of the detector, impedance matching should be achieved by changing the impedance of the antenna rather than by changing the impedance of the transistor. The parasitic capacitance and inductance of the gate power supply line will affect the antenna-transistor impedance matching. An open microstrip transmission line connected to the gate is designed to eliminate this influence. Measurement results show that the detector can detect THz radiation in the frequency range of 220 to 299 GHz. At 244 GHz, the detector achieves a best voltage responsivity of 2497 V/W and a noise equivalent power (NEP) of 357 pW/Hz1/2.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Terahertz (THz) spectrum, ranging from 100 GHz to 10 THz, has a lot of potential applications, such as security check [1], radar [2], communication [3], material analysis [4], and cancer detection [5]. With the development of THz technology, the demand for small, high-speed, and high-sensitivity detectors for THz radiation operating at room temperature becomes more pressing. Thermal detectors like Golay cells [6], bolometers [7], and pyroelectric detectors [8] are sensitive. However, they have a relatively slow temporal response. In the past decade, the study of THz detectors based on field effect transistors (FETs) has gained significant attention due to their advantages of high sensitivity, high response speed, and compactness. The interest in the applications of FETs for THz detection started at the beginning of 1990s with the pioneering theoretical work of Dyakonov and Shur who demonstrated that a FET can detect THz radiation higher than its cutoff frequency [9, 10]. First detector realizations have been demonstrated in GaAs high electron mobility transistor (HEMT) technologies in [11]. InAlAs/InGaAs/InP HEMT with an asymmetric dual-grating-gate has demonstrated responsivity of 2.2 kV/W at 1 THz [12, 13]. Furthermore, in 2017, H. Qin et al. reported direct detection of incoherent THz emission from hot blackbodies by using antenna-coupled AlGaN/GaN HEMT detectors cooled at 77 K [14]. Although HEMT-based detectors exhibit high sensitivity, it is difficult to integrate such a detector and signal processing circuits on a single chip. Owing to the advantages of low cost, high yield, and easy integration, CMOS technology is emerging as an alternative to other technologies. In recent years, development of CMOS FET-based detectors has been remarkably progressing [15,16,17,18,19,20,21,22,23,24,25,26]. The first sub-THz silicon FET detector was demonstrated in 2004 by Knap et al. [15]. The first focal plane FET detectors array was reported for imaging at 650 GHz in 2009 [16]. In 2012, a 1-k-pixel THz video camera chip was reported [19]. However, it adopts a two-NMOS configuration of a loop antenna feeding two NMOS transistors. Only half of the power received by the antenna is transferred to each transistor in the two-NMOS configuration. As a result, its output is 50% less than that of the single-NMOS detector. In 2017, a fully integrated 860-GHz CMOS THz sensor with readout circuit was reported [22], which integrates a grounded patch antenna to receive the THz waves. In 2019, a 32 × 32-pixel 0.94-THz imager with pixel-parallel 12b VCO-based ADC in 180-nm CMOS was reported, which also integrates a patch antenna [25]. However, the height between the metal layers of CMOS process is low, which will result in a low antenna radiation efficiency when the metal layers are used to fabricate a patch antenna below 300 GHz. Moreover, the large area of the patch antenna also makes it unsuitable for CMOS THz detectors below 300 GHz.

This paper presents a CMOS THz detector in a 180-nm CMOS process. The detector integrates a square loop antenna feeding a single-NMOS transistor. Compared with the circle loop antenna reported in [19], the square loop antenna is easier to be implemented in the CMOS process. Moreover, the square loop antenna is more suitable for THz detectors below 300 GHz than the patch antenna. To improve the power transfer efficiency between the antenna and the transistor, impedance matching between them is needed. There are two ways to achieve impedance matching: changing the impedance of the antenna and changing the impedance of the transistor. After analyzing, we conclude that the way to increase the voltage responsivity (Rv) of the detector is to change the impedance of the antenna rather than the impedance of the transistor. In the single-NMOS configuration, the gate-source bias supply lines will influence the transistors’ impedance and result in impedance mismatching. To overcome this problem, an open microstrip transmission line connected to the gate of the transistor is designed. Measurement results show that the detector can detect THz radiation in the frequency range of 220 to 299 GHz. At 244 GHz, the detector achieves a best Rv of 2497 V/W and a noise equivalent power (NEP) of 357 pW/Hz1/2. Using the detector, a clear raster-scanning transmission image is obtained. This paper is organized as follows. Section 2 reviews the theoretical analysis of the THz transistor. Section 3 presents the detailed design of the proposed THz detector. Section 4 presents the measurement results. Section 5 concludes this paper.

2 Theory

Detection of THz radiation by plasmonic nonlinearities in a two-dimensional (2D) electron channel of the FET was originally proposed by Dyakonov and Shur in the 1990s [9, 10]. When a THz radiation, Vacosωt, is coupled to the gate and source of a FET, as shown in Fig. 1, a photoresponse appears in the form of dc voltage between the source and drain which is proportional to the THz power. The dc voltage Vout can be written as:

where Va is the amplitude of the THz radiation, VG is the gate bias, and VTH is the threshold voltage of the FET. However, the theory does not give a design guideline on how to maximize detector responsivity by optimizing the FET physical dimensions. The relationship between Va and the THz power that the FET accepts is:

where P is the THz power that the FET accepts and Zm is the source input impedance of the FET at the corresponding THz frequency [22]. Therefore, Eq. 1 can be rewritten as:

Equation 3 indicates higher|Zm|2/Re(Zm) results in a higher |Vout|. [22] has simulated the relationship between Zm and the transistor dimensions. The simulation results show that |Zm|2/Re(Zm) increases as the length and width of the FET decrease. Therefore, it concludes that the FET with the minimum physical dimension can produce a maximum responsivity. Hence, the NMOS transistor in the present design has the minimum size of 0.18 μ m in length and 0.24 μ m in width.

3 Detector Design

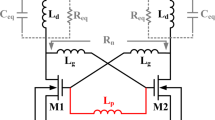

The circuit schematic of the proposed THz detector is shown in Fig. 2. It consists of an integrated on-chip square loop antenna and a source-feeding NMOS transistor with a nonbiased channel. The antenna has two feed ports. One is connected to the source of the transistor and the other is grounded to provide the source a dc ground. THz waves are received by the antenna and then coupled to the NMOS transistor, which has the minimum size of 0.18 μ m in length and 0.24 μ m in width. The gate of the transistor is biased to a constant potential VG and its drain is open. The output signal Vout is extracted from the drain. An open microstrip transmission line, TL, is designed to eliminate the influence of the gate bias supply line on the transistor’s impedance. All required low-frequency routing into the transistor is realized along the antenna midline (H-plane) in order to reduce the impact on the antenna performance.

The proposed THz detector has the following advantages. First, the detector uses a single-NMOS configuration. Compared with the two-NMOS detector configuration reported in [16, 17, 19, 24], the single-NMOS configuration offers an improved voltage responsivity. In the two-NMOS configuration, only half of the power received by the antenna is transferred to each transistor. As a result, its output is 50% less than that of the single-NMOS detector. Second, it integrates a square loop antenna, which is compatible with CMOS process design rules. Compared with the circle loop antenna reported in [19, 24], the square loop antenna is easier to be implemented in the CMOS process. Moreover, the square loop antenna is more suitable for THz detectors below 300 GHz than patch antenna [16, 21,22,23] for the patch antenna would occupy a very large area below 300 GHz. Third, one feed port of the antenna is connected to the source of the transistor and the other is grounded to provide the source a dc ground. Compared with [16, 17, 19], in which an additional bias line connected to the antenna is needed to provide the NMOS gate-source bias, the proposed structure does not require such an additional bias line, thus mitigating the system-level complexity for future array implementations. Fourth, an open microstrip transmission line is designed to improve the detector performance by eliminating the influence of the gate supply line. Finally, an NMOS transistor with a minimum size is used as the rectifying element. The analyses presented in Section 2 demonstrate that a transistor with a minimum size can produce a maximum output signal.

3.1 NMOS transistor

The length and width of the NMOS transistor are 0.18 μ m and 0.24 μ m, respectively. We used the Synopsys TCAD simulator to simulate the source input impedance of the transistor under different frequencies. The simulation result is shown in Fig. 3. To achieve the maximum power transfer from the antenna to the NMOS transistor, the source input impedance of the transistor should be the conjugation to the antenna’s impedance.

3.2 Square Loop Antenna

The square loop antenna is implemented using the top metal layer in the CMOS process and designed to provide broadband operation. The side length and the line width of the antenna are 252 μ m and 2 μ m, respectively, as shown in Fig. 2. The antenna has two feed lines. One is connected to the transistor and the other is grounded to provide the source a dc ground. Restricted by the minimum size of 2 μ m of the top metal layer, it is difficult to achieve a good impedance matching between the antenna and the transistor if the feed lines are implemented using the top metal layer. Hence, the feed lines are made of the second top metal layer. The length and width of each feed line are 125.3 μ m and 0.5 μ m, respectively.

The 3D electromagnetic solver package HFSS was used to simulate the antenna performance. Simulated results predict an antenna efficiency of 58–71% with a 1.85–4.5 dBi directivity across the 220–299-GHz band for back-side illumination through a 180-μ m-thick bulk silicon substrate. The simulated impedance of the antenna is plotted in Fig. 4.

The matching coefficient Mc, defined as the ratio of the power accepted by the NMOS transistor to the incident power from the antenna, can be expressed as follows:

where P is the THz power accepted by the NMOS transistor, Pinc is the incident THz power from the antenna, and ZANT is the antenna’s impedance. Figure 5 shows the calculated Mc as a function of frequency. Equation 3 can be rewritten as:

where η is the radiation efficiency of the antenna, Jinc is the power density incident to the antenna, and Aeff is the effective area of the antenna. Aeff can be calculated as follows:

where D is the directivity of the antenna and λ is the electromagnetic wave length in free space. The performance of a THz detector is typically expressed by means of Rv and NEP [27]. Rv is defined as the ratio between the detector output voltage and the power incident to antenna, that is:

According to the simulation results and Eq. 7, the relative Rv under different frequencies is calculated and plotted in Fig. 6.

As shown in Fig. 5, the maximum value of Mc is 0.23, which indicates that the THz power transfer between the antenna and NMOS transistor is not good. However, it is difficult to find a good matching network design to increase the impedance of the antenna without serious attenuation of its radiation efficiency. If we change the impedance of transistor to increase the Mc value, the value of \(\frac {|Z_{m}|^{2}} { \text {Re} (Z_{m})}\) would decrease. Next, we discuss an ideal condition. We assume that the perfect impedance matching is achieved at all frequencies by changing the impedance of the transistor, which means Re(Zm) = Re(ZANT) and Im(Zm) = -Im(ZANT). So, Mc = 1 and:

The relative Rv in this condition is also plotted in Fig. 6. As shown, although perfect impedance matching is achieved, the Rv is not optimized due to the low value of \(\frac {|Z_{ANT}|^{2}} { \text {Re} (Z_{ANT})}\). Therefore, we conclude that the way to increase the Rv is to change the impedance of the antenna rather than the impedance of the transistor.

3.3 Open Microstrip Transmission Line

Since the gate of the transistor should be connected to a constant potential, it is typically biased directly by an off-chip voltage supply through the bonding wire, pad, and on-chip metal line. The parasitic capacitance and inductance of these components will influence the transistor’s source input impedance. The TL (Fig. 2) is an open microstrip transmission line used to improve the detector performance by reducing the influence of the gate connections [22]. One end of it is connected to the transistor gate, and the other is floating, as shown in Fig. 7a. It is implemented in the second top metal layer, using the bottom metal layer as the ground plane. Its length and width are 135.7 μ m and 2 μ m, respectively. Figure 7 b shows its simulated impedance. Both the real and imaginary parts are less than 30 Ω in the frequency range of 220 to 299 GHz. Since the TL and the gate bias supply line are connected in parallel, the low impedance TL will reduce the influence on the transistor’s impedance.

4 Measurement Results

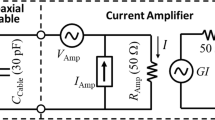

The detectors are fabricated in a 180-nm CMOS process. Figure 8 shows its die photo. The proposed detector is displayed in the middle, which is characterized using the lock-in technique. The chip is mounted on a printed circuit board (PCB). Since the chip receives THz waves from the back, we made a circular hole in the middle of the PCB to place the chip and bonded it with a polyethylene, as shown in Fig. 9a. Figure 9 b illustrates the measurement setup. Continuous-wave THz signal is radiated by a THz vector network analyzer (VNA). The frequency of the radiated THz signal is tunable. In the test, the test frequency ranges from 220 to 299 GHz. Linearly polarized THz signal is radiated through a 25-dBi diagonal horn. A mechanical chopper with a frequency of 114 Hz modulates the THz signal. A 20-dB low noise amplifier (LNA) is connected directly at the output of the detector and a lock-in amplifier is used to recover the output signal. The radiated THz power at different frequencies is measured with a power meter and plotted in Fig. 10.

The measurement results show that the detector has the best output at 244 GHz. The measured Rv and NEP of the detector as a function of the gate bias voltage at 244 GHz are shown in Fig. 11. The peak non-amplified Rv is 2497 V/W and the minimum NEP at 114-Hz modulation frequency is 357 pW/Hz1/2 for a gate bias of 0.33 V and 0.52 V, respectively. The NEP changes slowly in the gate voltage range of 0.3–0.6 V.

The maximum Rv versus frequency is plotted in Fig. 12. From 220 to 299 GHz, the Rv is between 117 and 2497 V/W. In the frequency range of 241 to 260 GHz, the Rv is higher than 1500 V/W. The simulated relative Rv based on Eq. 7 is also plotted in Fig. 12. The two curves are similar in shape but there is a difference of approximately 7 GHz in frequency. The reason for this deviation may be that in the simulation of the antenna, the dielectric constant is set according to the value given by foundry, while in fact the dielectric constant varies with the frequency. In other words, the dielectric dispersion is not considered in the simulation, which leads to the difference between simulation and measurement.

We realize a THz imaging system using the detector, as shown in Fig. 13a. A mechanical chopper with a frequency of 114 Hz modulates the radiation of a VNA with a radiation frequency of 244 GHz, and at the same time, generates a TTL signal as the reference signal for a lock-in amplifier. The THz radiation is collimated and focused on an object by two parabolic mirrors. The object is fixed on a two-dimensional stepper to realize the scanning image. The transmitted THz radiation is collimated and focused on the detector by two other parabolic mirrors. The output signal of the detector is amplified by a 20-dB LNA and the lock-in amplifier is used to capture the amplified signal. Figure 13 b shows a raster-scanning image of a knife in a paper envelope. The scanned area was 3 × 5 cm2, divided into 150 × 250 pixels. The image clearly reveals the shape of the hidden knife. A performance comparison between this work and other published THz detectors is shown in Table 1.

5 Conclusions

This paper proposes and implements a novel THz detector in a 180-nm standard CMOS process. The detector integrates a square loop antenna feeding a single-NMOS transistor with a nonbiased channel. One port of the antenna is grounded so that it does not require an additional bias line to provide a dc path for the NMOS transistor. An open microstrip transmission line, TL, is designed to improve the detector performance. Measurement results show that the detector can detect THz radiation in the frequency range of 220 to 299 GHz. At 244 GHz, the detector has the best output. The maximum Rv and minimum NEP are 2497 V/W and 357 pW/Hz1/2, respectively. Using the detector, a clear raster-scanning transmission image has been obtained. The results indicate that the proposed detector can be further used in a multi-pixel array for THz imaging.

Change history

22 September 2022

A Correction to this paper has been published: https://doi.org/10.1007/s10762-021-00782-x

References

J. F. Federici, B. Schulkin, F. Huang, D. Gary, R. Barat, F. Oliveira, and D. Zimdars, Thz imaging and sensing for security applications—explosives, weapons and drugs, Semiconductor Science and Technology, vol. 20, pp. S266–S280 (2005).

K. Cooper, R. Dengler, N. Llombart, B. Thomas, G. Chattopadhyay, and P. Siegel, THz imaging radar for standoff personnel screening, IEEE Transactions on Terahertz Science and Technology, vol. 1, pp. 169–182 (2011).

Z. Chen, X. Ma, B. Zhang, Y. Zhang, Z. Niu, N. Kuang, W. Chen, L. Li, and S. Li, A survey on terahertz communications, China Communications, pp. 1–35 (2019).

M. Tanaka, H. Hirori, and M. Nagai, THz nonlinear spectroscopy of solids, IEEE Transactions on Terahertz Science and Technology, vol. 1, pp. 301–312 (2011).

P. Doradla, C. Joseph, and R. H. Giles, Terahertz endoscopic imaging for colorectal cancer detection: current status and future perspectives, World Journal of Gastrointestinal Endoscopy, vol. 08, pp. 7–19 (2017).

http://www.tydexoptics.com/products/thz_devices/golay_cell/.

B. S. Karasik, A. V. Sergeev, and D. E. Prober, Nanobolometers for thz photon detection, IEEE Transactions on Terahertz Science and Technology, vol. 1, pp. 97–111 (2011).

W. R. Whatmore, Pyroelectric devices and materials, Reports on Progress in Physics, vol. 49, pp. 1335–1386 (1986).

M. Dyakonov and M. Shur, Shallow water analogy for a ballistic field effect transistor: new mechanism of plasma wave generation by dc current, Physical Review Letters, vol. 71, pp. 2465–2468 (1993).

M. Dyakonov and M. Shur, Detection, mixing, and frequency multiplication of terahertz radiation by two-dimensional electronic fluid, IEEE Transactions on Electron Devices, vol. 43, pp. 380–387 (1996).

H. G. Krekels, B. Schiek, and E. Menzel, Power detector with GaAs field effect transistors, in IEEE 1992 22nd European Microwave Conference, pp. 174–179 (1992).

T. Watanabe, S. B. Tombet, Y. Tanimoto, Y. Wang, H. Minamide, H. Ito, D. Fateev, V. Popov, D. Coquillat, W. Knap, Y. Meziani, and T. Otsuji, Ultrahigh sensitive plasmonic terahertz detector based on an asymmetric dual-grating gate HEMT structure, Solid State Electronics, vol. 78, pp. 109–114 (2012).

Y. Kurita, G. Ducournau, D. Coquillat, A. Satou, K. Kobayashi, S. B. Tombet, Y. M. Meziani, V. V. Popov, W. Knap, T. suemitsu, and T. Otsuji, Ultrahigh sensitive sub-terahertz detection by InP-based asymmetric dual-grating-gate high-electron-mobility transistors and their broadband characteristics, Applied Physics Letters, vol. 104, pp. 251114 (2014).

H. Qin, X. Li, J. Sun, Z. Zhang, Y. Sun, Y. Yu, X. Li, and M. Luo, Detection of incoherent broadband terahertz light using antenna-coupled high-electron-mobility field-effect transistors, Applied Physics Letters, vol. 110, pp. 171109 (2017).

W. Knap, F. Meziani, N. Dyakonova, N. Lusakowski, F. Boeuf, T. Skotnicki, D. Maude, S. Rumyantsev, and M. S. Shur, Plasma wave detection of sub-terahertz and terahertz radiation by silicon field-effect transistors, Applied Physics Letters, vol. 85, pp. 675 (2004).

E. Öjefors, U. R. Pfeiffer, A. Lisauskas, and H. G. Roskos, A 0.65 THz focal-plane array in a quarter-micron CMOS process technology, IEEE Journal of Solid-State Circuits, vol. 44, pp. 1968–1976 (2009).

R. Al Hadi, H. Sherry, J. Grzyb, N. Baktash, Y. Zhao, E. Öjefors, A. Kaiser, A. Cathelin, and U. Pfeiffer, A broadband 0.6 to 1 THz CMOS imaging detector with an integrated lens, in IEEE MTT-S International Microwave Symposium (2011).

F. Schuster, D. Coquillat, H. Videlier, M. Sakowicz, F. Teppe, L. Dussopt, B. Giffard, T Skotnicki, and W. Knap, Broadband terahertz imaging with highly sensitive silicon CMOS detectors, Optics Express, vol. 19, pp. 7827–7832 (2011).

R. Al Hadi, H. Sherry, J. Grzyb, Y. Zhao, W. Forster, H. M. Keller, A. Cathelin, A. Kaiser and U. R. Pfeiffer, A 1 k-Pixel Video Camera for 0.7-1.1 Terahertz Imaging Applications in 65-nm CMOS, IEEE Journal of Solid-State Circuits, vol. 47, pp. 2999–3012 (2012).

A. Boukhayma, A. Dupret, J. P. Rostaing, and C. Enz, A low-noise CMOS THz imager based on source modulation and an in-pixel high-Q passive switched-capacitor N-path filter, Sensors, vol. 16, Art. no. 325 (2016).

Z. Y. Liu, L. Y. Liu, Z. Zhang, J. Liu, and N. J. Wu, Terahertz detector for imaging in 180-nm standard CMOS process, Science China Information Sciences, vol. 60, pp. 082401:1–082401:9 (2017).

Z. Y. Liu, L. Y. Liu, J. Yang and N. J. Wu, A CMOS fully-integrated 860-GHz terahertz sensor, IEEE Transactions on Terahertz Science and Technology, vol. 7, pp. 455–465 (2017).

T. Fang, Z. Y. Liu, L. Y. Liu, Y. Y. Li, J. Q. Liu, J. Liu, and N. J. Wu, Detection of 3.0 THz wave with a detector in 65 nm standard CMOS process, in 2017 IEEE Asian Solid-State Circuits Conference (A-SSCC), pp. 189–192 (2017).

L. Xu, J. Guan, X. Bai, Q. Lin, and H. Mao, A novel CMOS multi-band THz detector with embedded ring antenna, Journal of Infrared, Millimeter, and Terahertz Waves, vol. 38, pp. 1189–1205 (2017).

S. Yokoyama, M. Kanazawa, T. Ikegami, P. Ambalathankandy, S. Hiramatsu, E. Sano, Y. Takida, and H. Minamide, A 32 × 32-Pixel 0.9 THz imager with pixel-parallel 12b VCO-based ADC in 0.18 μ m CMOS, in IEEE International Solid- State Circuits Conference, pp. 108–110 (2019).

P. Hillger, J. Grzyb, R. Jain, and U. R. Pfeiffer, Terahertz imaging and sensing applications with silicon-based technologies, IEEE Transactions on Terahertz Science and Technology, vol. 9, pp. 1-19 (2019).

R. Han, Y. Zhang, D. Coquillat, H. Videlier, W. Knap, E. Brown and O. Kenneth, A 280-GHz Schottky diode detector in 130-nm digital CMOS, IEEE Journal of Solid-State Circuits, vol. 46, pp. 2602–2612 (2011).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

National Natural Science Foundation of China (NSFC) (61804160, 61605235, 61801467); National Key Research and Development Program of China (2016YFC0102900); Hundred Talent Program of Chinese Academy of Sciences.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Liu, Zy., Qi, F., Wang, Yl. et al. A 220- to 299-GHz CMOS Terahertz Detector. J Infrared Milli Terahz Waves 40, 606–619 (2019). https://doi.org/10.1007/s10762-019-00592-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10762-019-00592-2