Abstract

Nowadays, wireless communications at frequencies of gigahertz have an increasing demand due to the ever-increasing number of electronic devices that uses this type of communication. However, the design of Radio Frequency (RF) circuits is difficult, time-consuming and based on designer knowledge and experience. This work proposes an interactive evolutionary approach based on genetic algorithm, implemented in the in-house iMTGSPICE optimization tool, to perform the optimization process of a Low-Power Low Noise Amplifier (LNA) dedicated to Wireless Sensor Networks (WSN), which is robust through the corner and Monte Carlo analyses and implemented in two Bulk CMOS technology nodes: 130 nm and 65 nm. Regarding each technology node, we performed two experimental studies to optimize the LNA. The first one used the conventional non-interactive approach of iMTGSPICE, which was not assisted by a designer during the optimization process. The second one used the interactive approach of iMTGSPICE, which was monitored and assisted by a beginner designer during the optimization process. The obtained results demonstrated that the interactive approach of iMTGSPICE performed the optimization process of the robust LNA from 16 to 94% faster than the non-interactive evolutionary approach. The design regarding the technology node of 130 nm took 341 min for the non-interactive and 20 min for the interactive optimization process, whereas the design in the 65 nm took 537 min for the non-interactive and 454 min for the interactive approach.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

1 Introduction

The demand for applications using wireless communication has grown significantly. Recent concepts such as Internet of Things (IoT) and Industry 4.0 are very promising due to the possibility of monitoring and controlling applications without using wire connections. In a wireless communication network, radio frequency (RF) Complementary Metal–Oxide–Semiconductor (CMOS) Integrated Circuits (ICs) are essential elements. As a front-end of wireless transceivers, RF circuits are responsible by processing the analog signal in order to ensure the integrity of information exchanges between electronic devices. Unlike digital CMOS ICs, RF circuits are traditionally designed by hand, based on circuit behavioral equations, followed by an iterative manual process using classical electrical circuit simulators. This process is often very laborious, costly and time-consuming [1], [2], [3]. Besides, the optimization processes of CMOS RFICs are performed by manual methods and need much knowledge and experience of the designers to reach the additional metrics required by this kind of ICs. Therefore, the complexity presented by CMOS RFICs complicates its automation task, and, consequently, its design has remained dependent on the expertise of RF designers.

In this scenario, evolutionary computation techniques to solve multi-objective problems in the artificial intelligence area are appropriate and have been successfully used in the optimization processes of analog and CMOS RFICs robust through corner and Monte Carlo analyses[1], [4], [5]- [8]. Despite the recent advances in tools to assist the design of analog and RF ICs, the design of these ICs has depended on the designer's experience. Thus, one of the ways to increase the effectiveness of optimization tools is to integrate the artificial and human intelligences to perform the optimization process. The artificial intelligence area that incorporates interaction between the humans and the computational tool is the interactive evolutionary computation (IEC) [9]. The IEC approach is typically applied when an analytical fitness function is very difficult or impossible to be elaborated, as for example in several areas, such as musical [10], aesthetic [9], ergonomic [11], automotive, graphic art and animation, food engineering [12], among others, in which subjective evaluations are applied. However, this technique have not been explored for the CMOS RFICs optimization. To overcome this complex and challenging issue, this work proposes the use of an in-house electronic design automation (EDA) tool to optimize CMOS RFICs, named iMTGSPICE [13], [14], [15]. It is capable of reducing the optimization cycle times of these circuits due to its heuristic processes of artificial intelligence and IEC techniques. Therefore, designers can optionally interact with the optimization process at any time to stop and change design parameters, such as bias conditions, transistors sizes, specifications to be achieved, etc., and evolutionary process parameters, which are usually the priorities of searching, sigma of the fitness functions, number of iterations, etc., inserting the designers’ expertise to reach robustness in desired specifications. It is important to highlight that iMTGSPICE is capable of producing robust solutions of analog and CMOS RFICs in hours. Moreover, it performs the corner and Monte Carlo analyses in the loop of optimization process without reducing the sample space of searching. Interestingly, by the proposed approach, the optimization cycle time is feasible, taking into account all time considered for the optimization of these types of circuits. Therefore, by using iMTGSPICE, the designers are able to meet severe specifications in a reduced optimization cycle time, while guaranteeing the robustness of analog and CMOS RFICs, taking into account the manufacturing process, supply voltage and temperature variations.

In order to demonstrate the proposed computational tool, a classical RF IC is designed: the low-noise amplifier (LNA). The LNA is the first active building-block in a reception chain [16], [17]. It is responsible for amplifying the small RF input signal from the antenna and for assuring a low noise factor for the remaining blocks of the receiver. The main metrics of the ultra-low power LNA for wireless sensor network applications [17], such as power consumption, area, impedance matching, gain and noise figure, are optimized by using the proposed design automation tool (iMTGSPICE). Two experiments are performed for the optimization process of this LNA using the GA. The first one uses the conventional non-interactive approach and the second uses the proposed interactive evolutionary approach, which is compared to the conventional non-interactive approach. These experiments are also performed considering two Bulk CMOS technology nodes: 130 nm and 65 nm. The obtained results are compared in terms of robustness, regarding the manufacturing process, supply voltage and temperature variations, and optimization cycle time.

This paper is organized as follows: Sect. 2 presents the interactive evolutionary approach proposed in this work. Next, in Sect. 3, the LNA topology used in this work is presented. The LNA specifications and configuration parameters of the optimization EDA tool and robustness analyses are provided in Sect. 4. Section 5 discusses the results obtained by the proposed approach. Finally, Sect. 6 concludes this paper.

2 Interactive evolutionary approach of the optimization tool

Fig. 1 illustrates the block diagram of the interactive evolutionary approach with the GA implemented in the optimization tool [13], [14], [15]. It is developed in C + + language and manages the Spice Opus simulator [18]. Moreover, it performs robustness analyses through corner analysis and Monte Carlo analysis in the loop of the optimization process [19].

Designers need to configure the iMTGSPICE before starting the optimization process (Block A) [14], [20]: the description of the circuit (SPICE netlist); input variables with their specified ranges, such as the transistors sizes (channel width, W, and channel length, L), bias conditions (voltage and current sources), values of passive components (resistors, capacitors and inductors); the output variables, which are the desired specifications or figures of merit (FoMs) with their respective tolerance ranges, such as the forward gain (S21), input reflection coefficient (S11), output reflection coefficient (S22), noise figure (NF), power consumption (PTOT), and total gate area of MOSFETs (AG); the GA parameters, such as population size (NP), crossover and mutation rates (PC and PM), the weight (priority) applied for each FoM of the fitness function (Wei), where i is an index that represents a FoM, the standard deviation of the Gaussian fitness functions (σ) [20], and NRob is the desired number of solutions contained in the population that fully meet the design specifications taking into account the robustness analyses, which is used as the stop criterion.

The iMTGSPICE performs the evolution process in two stages [20], [21], which are based on the procedure commonly adopted by the analog CMOS IC designer. The first stage is responsible for evolving functional constraints of the analog IC, such as the direct current (DC) bias conditions of the MOSFETs to ensure that all of them operate in the desired saturation region. The second stage is responsible for making the evolution process of the alternating current (AC) analysis of the analog CMOS IC with the aim of obtaining the final required solutions. It is important to emphasize that the DC stage is performed before the AC stage and they follow the same general block diagram illustrated in Fig. 1. The first stage (DC stage) starts generating randomly a set of potential solutions (Block B), which evolve to obtain one or more solutions, defined by the designer, that meet the functional constraints. The second stage (AC stage) also starts generating randomly a set of NP potential solutions (defined by the designer) and then one or more of them are replaced by the best solutions found in the first stage of the evolution process.

Next, in Block C, each potential solution is simulated in SPICE [20]. Then, the FoMs (desired specifications) of each potential solution (S21, S11, S22, NF, PTOT, AG) are obtained and evaluated by minimization, center value, and maximization fitness functions [20] considering a range from 0 to 100 and the value of the fitness function of a potential solution is represented by EvalSol, which is the weighted sum considering the values of the FoMs.

Afterwards, in Block D, the robustness of the best potential solutions evaluated by the fitness functions are calculated, until the evolution process find the NRob robust potential solutions. The robustness calculation regarding a potential solution is performed as follows:

-

I- The minimum and maximum performance values of each FoM are obtained through robustness analyses (corner or Monte Carlo). The deviations of the different FoMs found are determined considering their minimum and maximum values relative to the desired specifications;

-

II- The average value of the deviations found of item I (εsol) is calculated regarding the worst performance of each FoM, considering their minimum and maximum performance values [19]. Next, the value of the fitness function of each potential solution is calculated considering the value of its εsol. Afterwards, the population is reordered, giving the highest priority for the most robust potential solutions, which are identified by those that improve more the FoMs (highest εsol values).

Moreover, the relative deviations are calculated depending on the profile type of the fitness function (central value, minimization, and maximization [20]):

-

I- “central value”: as this specification is defined by the minimum, nominal, maximum values, two deviations are calculated. The first (second) one is calculated considering the maximum (minimum) FoM value subtracted from the nominal desired specification;

-

II- “maximization”: this specification is defined by only one value (value of the desired minimum specification);

-

III- “minimization”: this specification is defined by only one value (value of the desired maximum specification).

In addition, the relative deviation can be positive or negative, when the performance of the FoM is higher or lower in relation to the desired specification, respectively. Therefore, in the case of the “central value” profile of the fitness function, the relative deviation considered for the FoM (worst case) is the one that presents the smallest value between the two relative deviations found.

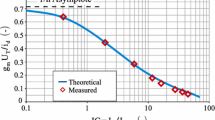

The FoMs, MOSFETs’ sizes, values of bias voltages, and values of the passive components of the most robust potential solution obtained are displayed in the screen of iMTGSPICE (Block E). Fig. 2 presents one of the screens, which monitors the EvalSol and FoMs found (S21, S11, S12, S22, NF, PTOT), taking into account the corner analysis and Monte Carlo analysis in the loop of the optimization process as a function of the number of iterations (generations).

Next, in Block F, the interactive procedure can be carried out by the designer. Then, based on the real-time monitoring of the design variables and FoMs displayed in the iMTGSPICE screen, optionally, the designer can pause the evolution process and interact with it. The interaction with the system can be performed by changing the dimensions and values ranges regarding the design variables, such as the channel width and length of the MOSFETs, bias conditions of the LNA, passive components (resistors, capacitors and inductors), as well as parameters of the evolution process.

Furthermore, in Block G, genetic operators are applied to generate a new population to be evolved. Each potential solution in iMTGSPICE is represented by a binary chromosome [21]. Each chromosome contains the design variables (transistors dimensions, bias conditions and values of resistors, capacitors and inductors), in which the length of the chromosome is calculated according to the accuracy required for the design variables [21]. The selection process of the best robust potential solutions is performed by the binary tournament. The reason for choosing this method is that it demonstrated to be faster and more effective than other methods, such as the roulette wheel in the experiments performed in this work. Afterwards, the single-point crossover is applied for the selected individuals in population to generate a new set of individuals for the next generation. The use of this type of crossover is due to the best average performance achieved in several experiments considering other types of crossover, such as two points and uniform. Finally, a bit flip mutation is applied for this new generation to further explore the search process of potential solutions [14, 21], which was chosen due to the binary chromosome representation of the GA. The stop criterion is verified in Block H. If the desired number of robust solutions (NRob) is achieved the optimization process finalizes, otherwise it continues until reaching NRob or the maximum number of iterations defined by the designer [19].

3 Topology of the LNA

Among the RF receiver building-blocks, the LNA is one of the most critical. In addition to increase the amplitude of the weak incoming signal from the antenna, this circuit needs to operate with severe targets of noise figure and linearity. Focusing in Wireless Sensor Network (WSN) applications, the power consumption of such RF circuit is also a crucial objective. For comparison reasons, the LNA proposed in this work was designed in two different technological nodes: 65 nm and 130 nm CMOS. The LNA topology used is presented in Fig. 3. It is based on an ultra-low power LNA first presented by [17]. Targeting low-power applications, topologies using active load are preferred. So, the proposed circuit presented in Fig. 3 implements a modified self-biased inverter [17]. It is composed of two stages: amplification stage and buffering stage. The amplification stage is the LNA core, designed to amplify the input signal linearly using M1 (nMOSFET), M2 (pMOSFET), inductor Lg, capacitor C1 and resistor RF. In order to improve gain and reduce noise figure, a biasing voltage Vpol1 is applied to M1 through resistor Rpol1. The buffering stage, composed by M3 (nMOSFET) and the inductor Lpk, is used for measurement purposes, in order to comply with 50 Ohms input impedance of test equipment. The required output matching (50 Ohms) is obtained thanks to the capacitive divider of Cm2 and Cm3. On the other hand, Cm1 contributes to the inter-stage impedance matching, as well as to allow the biasing of transistor M3 through Vpol2 connected to the resistor Rpol2. Two different supply voltages are presented in Fig. 3: VCC and VDD. For the LNA designed in a 65 nm technology, the VDD is reduced to 0.5 V, while the VCC is kept in the nominal voltage of 1 V. The main goal is to reduce the power consumption of the LNA core. However, for the LNA designed in a 130 nm technology, VCC and VDD are connected to the same voltage of 1.2 V. In the next section, based on the proposed LNA topology, an interactive evolutionary approach is applied in order to best define the biasing voltages and devices sizing, according to required specifications.

In addition, the input terminal is represented by in node and the output terminal by the out node. Finally, the large decoupling capacitor, Cdec, ensures AC ground at the source of M2.

4 LNA Specifications and configuration parameters of iMTGSPICE and robustness analyses

In this work, we have considered the required specifications of the LNA according Table 1.

Table 1 presents the seven different figures of merit (specification parameters) considered for the LNA design. Moreover, all MOSFETs (M1, M2 and M3) are set to operate in the saturation region (functional constraints).

Two CMOS Bulk manufacturing technologies are used to design the LNA: the 130 nm technology from the GlobalFoundries [22], which will be referred to as LNA_130, and the 65 nm technology from TSMC [23], which will be identified as LNA_65. The standard supply voltage of both technologies (GlobalFoundries and TSMC) used in this work is 1.2 V. The LNA_130 operates at 2.4 GHz and supply voltages VCC and VDD of 1.2 V. The LNA_65 operates at the same frequency, but different supply voltages VCC and VDD, which were fixed in 1 V and 0.5 V, respectively. For the LNA_130 the standard supply voltage of the technology was applied, which enabled the optimization process to achieve the desired specifications. However, for the LNA_65, supply voltages below the maximum allowed by the technology were applied due to power consumption constraints. Additionally, the nominal operating temperature of the LNAs is 27 °C.

Table 2 presents the ranges of values adopted for the design parameters (minimum, maximum, and step size values) for the evolution processes of the LNA_130 and LNA_65. Furthermore, W and L represent the channel width and channel length of the MOSFETs, respectively, and m1, m2, m3 represent the multiplicity of each transistor, that is, the number of parallel transistors regarding each MOSFET (M1, M2 and M3). It is important to mention that no expert knowledge was used to define the ranges of values adopted for the design parameters. The range of values of the parameters in Table 2 are based on the literature [17]. For instance, the minimum value of a given parameter can be adopted smaller than that of the reference and the maximum value can be adopted greater than that of the reference.

Initially, regarding both LNAs, the default values for the weights (Wei) of the fitness function of all FoMs were considered the same to perform the evolution process regarding the DC evolution process (first stage), that is, 50% for PTOT and AG. Similarly, for the AC evolution process (second stage), we considered the same weights (14.3%) for the FoMs (|S21|, |S11|, |S12|, |S22|, NF, PTOT, and AG). Moreover, the σ parameter of the Gaussian fitness function was set to 0.2 for all profiles considered (minimization and maximization) and the two evolution processes, which is related to a maximum tolerance of 25% for the desired specifications [20].

Regarding the LNA_130, the parameters related to the DC and AC evolution processes initially are set as follows: NP is set to 50, the maximum number of iterations (NIter) was set to 3,000, however, the number of iterations used in each optimization run is not fixed due to the other applied stop criterion (NRob) considered in this work, which is set to 2 (number of robust solutions to be found by the optimization process by using the corner analysis and Monte Carlo analysis), regarding the DC and AC evolution processes. For the LNA_65, the initial parameters are set as follows: NP are set to 50 and 100, regarding the DC and AC evolution processes, respectively; NIter was set to 10,000 (DC and AC evolution processes); NRob is set to 1 for the DC and AC evolution processes.

Furthermore, it is important to emphasize that after the DC optimization process is ended, the best DC potential solutions, given by NRob, are used to compose the initial population that will be used to perform the AC evolution process of the LNA. Consequently, at the end of the AC evolution process, NRob robust potential solutions are generated, which are obtained from each optimization run. The most robust potential solutions are identified by the highest average deviations regarding all deviations of each FoM in relation the desired specifications, that is, the most robust solution is the one which maximizes the desired specifications. In the iMTGSPICE implementation, PC is set to 70%, and PM is set to 3% for both (DC and AC) evolution processes and both LNAs.

It is important to highlight that all the initial values of the iMTGSPICE configuration parameters can be changed by the designer during the iMTGSPICE search process.

In the experiments carried out in this work, the robustness analyses are performed by both, the corner analysis and Monte Carlo analysis. It is important to mention that the corner analyses are performed first, and subsequently, the Monte Carlo analyses are performed only for those potential solutions that met all desired specifications found by the corner analyses. This procedure is performed to avoid waste of time in the Monte Carlo analysis when a certain potential solution is not robust by the corner analysis, considering that the aim of the optimization process is to ensure the design robustness by both analyses simultaneously (corner analysis and Monte Carlo analysis).

During the optimization process, the robustness of the LNA_130 in relation to global process variations is verified by the corner analysis. Regarding the corner analysis, we have considered the threshold voltages (Vth) and mobility of the charge carriers along the channel length (µ0) of MOSFETs. These parameters are responsible for affecting the main analog parameters of the MOSFETs, such as the transconductance (gm). The extreme global variations of Vth and µ0 were set to ± 10% and ± 6%, respectively, for the nMOSFETs, and ± 12% and ± 10%, respectively, for the pMOSFETs [24]. Therefore, the extreme operating conditions of the nMOSFETs and pMOSFETs were considered during the corner analysis. In the operating condition named Fast–Fast (FF), the nMOSFETs and pMOSFETs operate at the maximal gm. In the operating condition named Slow-Slow (SS), the nMOSFETs and pMOSFETs operate at the minimal gm. In the operating condition named Fast-Slow (FS), the nMOSFETs operate at the maximal gm and the pMOSFETs at minimal gm. Finally, in the operating condition named Slow-Fast (SF), the nMOSFETs operate at the minimal gm and the pMOSFETs at maximal gm. Moreover, the lowest value of the Vth and the highest value of µ0 define the maximal gm, and the highest value of the Vth and the lowest value of µ0 define the minimal gm referring to the nMOSFETs and pMOSFETs. Furthermore, variations of the temperature (environmental) are taken into account, i.e. 0 °C and 75 °C, respectively. The Monte Carlo analysis is also performed during the optimization process. It takes into account the local and global variations of manufacturing process parameters, besides environmental conditions. As we considered 50 global variations (NGLob = 50), 50 local variations (NLoc = 50) and two different temperatures (0 °C and 75 °C), each Monte Carlo analysis performs 5000 simulations (NGLob·NLoc·2), according to the procedure described in [20]. Moreover, the desired yield value of the potential solutions by the proposed approach is 100%, as all the Monte Carlo sample results regarding the desired specifications must be inside the tolerance ranges, which are defined by the designer. For the optimization process of the LNA_65, the corner analysis considered the same settings of the LNA_130, however, an additional environmental variation is considered. For this case, the supply voltages (VCC and VDD) are varied in ± 3%. The Monte Carlo analysis performed during the optimization process of the LNA_65 takes into account only the local and global variations of manufacturing process parameters. As we considered 25 global variations (NGLob = 25), 50 local variations (NLoc = 50), each Monte Carlo analysis performs 1250 simulations, according to the procedure described in [24].

5 Results

The iMTGSPICE was run in a 3.4 GHz IBM-PC with 24 GB RAM and Windows 10 (operating system). The optimization processes of the LNA_130 and LNA_65 in this work were performed regarding two different conditions: (1) Automatic optimization processes by using the conventional GA (non-interactive) of iMTGSPICE; (2) Interactive optimization processes by using the iMTGSPICE assisted by a beginner designer during the optimization processes. It is important to mention that, in the case of the interactive approach, the designer's experience in analog integrated circuit design is not important due to the design approach used in the experiment, which limits the designer's intervention to only a few basic optimization parameters, as will be detailed later in this work. Moreover, both experiments were performed to optimize the LNAs, considering a single run (number of times that the iMTGSPICE was run to obtain the results). Therefore, these experiments with the LNAs are just examples of application of the interactive approach using the GA instead of a statistical validation. However, these experiments are still valid by the usage history of the iMTGSPICE tool [13], which demonstrate that although different results are possible, in their average, the interactive approach of iMTGSPICE can reduce significantly the design cycle time.

The optimization processes can be severely affected by the random generation of the initial population (set of solutions) and by the behavior of the selection, crossover and mutation genetic operators, which are driven by the random generator used by the GA. Therefore, in order to perform a fair comparison between the two experiments, the random generator used by the GA in each experiment was started with the same seed, so that the same initial population is used by each experiment, that is, both experiments have the same starting point. This procedure ensures that the differences in the performance of the interactive method in relation to the non-interactive are only due to the effectiveness of the genetic operators (selection, crossover and mutation) which act with the aid of human intelligence in the interactive approach.

Regarding the second experimental condition, as the researcher is not an expert in RF design, he was oriented not to change the design parameters, which are the MOSFETs dimensions (W, L), bias voltages of the LNAs (Vpol1 and Vpol2) and values of passive components (resistors, indictors and capacitors). The interactive process allowed changes in design specifications as long as they comply with the values specified in Table 1. In addition, basic GA parameters, such as the weights of the design specifications (Wei) and the standard deviation of the Gaussian fitness functions (σ) were also allowed to be changed during the optimization processes.

Table 3 presents the design variables obtained by the non-interactive and interactive approaches for the LNA_130 and LNA_65, respectively. Table 4 presents the desired specifications (Specs.) of the figures of merit (FoMs) and the average values of the FoMs obtained by the non-interactive and interactive approaches for the LNA_130 and LNA_65, respectively.

The threshold values in Table 4, which were defined for the specifications, are required by the application of the LNAs. As the threshold values are the minimum specifications considered for the application, the minimization ( <) or maximization ( >) profile set for each specification aims to improve the respective figure of merit whenever possible. Because there are tradeoffs among the several specifications to be met simultaneously, achieve all required specifications is a very difficult task. Therefore, the criterion used to identify that one approach is better than the other is the one which is the able to improve the greatest number of specifications. We can observe in Table 4 that both non-interactive and interactive approaches of the iMTGSPICE used for the design of the LNA_130 and LNA_65 successfully achieved the specifications within the desired tolerance range. Regarding the LNA_130, the interactive approach with a non-expert designer obtained the best results for most FoMs: S21, S11, S12, PTOT, and AG with differences of 97%, 59%, 14%, 30%, and 11%, respectively. Only for two FoMs, S22 and NF, the interactive approach obtained inferior results in relation to the non-interactive, with differences of 86% and 75%, respectively. As a non-specific value was set for S22 and the NF value obtained by the interactive approach met the required specification, the designer prioritized the improvement of the other FoMs as the most positive approach. Despite the large relative difference regarding the NF, which is an important FoM for a LNA, the results obtained by both methods, interactive and non-interactive are very good, as they are considerably smaller than the required specification of 4 dB. Furthermore, considering the LNA_65, the interactive approach with a non-expert designer also obtained the best results for most FoMs: S21, S11, S22, NF, and AG (5%, 72%, 26%, 19%, and 52%). Only for two FoMs, S12 and PTOT, the interactive approach obtained worse results than the non-interactive, with differences of 7% and 41%, respectively. As the two aforementioned parameters were met by the interactive method, the designer prioritized the improvement of the largest possible number of FoMs evaluated for the LNA. It is observed that the interactive approach can be used to guide the optimization process in such a way to meet faster the required specifications and in a given direction, prioritizing certain specifications. These results demonstrate the advantage of using the interactive approach to improve the performance of the LNAs.

It is important to note some important results in Table 4 related to the LNA_130. The interactive approach achieved 32.1 dB for the forward gain (S21) of the LNA_130, whereas the non-interactive approach obtained a value of only 16.3 dB, a difference around 16 dB. As the operation frequency of the LNA is 2.4 GHz, the S21 parameter is measured in this frequency. As can be seen in Fig. 4 (a), the S21 parameter obtained by the interactive approach is better centered in the operation frequency than the non-interactive approach. This is the main reason by the huge difference in this parameter. Despite the remarkable difference, by the beginner approach of the interactive method, no expert knowledge was necessary. During the optimization process, the user observed in real time that this parameter was improving very slowly. Therefore the user increased the weight (priority) of the S21 parameter in the iMTGSPICE tool and reduced the weight of other parameters, which achieved more easily the required specifications, for example PTOT and AG. Other remarkable results are observed in Table 4 regarding both LNAs. The interactive approach improved in more than 10 dB the input reflection coefficient (S11) of the LNA_130 and LNA_65. For example, the interactive approach obtained the value of − 25.3 dB for the S11 parameter of the LNA_65, whereas the non-interactive approach obtained a value of -14.7 dB. Similarly to the previous case, as can be seen in Fig. 5 (a) and Fig. 5 (b), the S11 parameter obtained by the interactive approach is better centered in the operation frequency than the non-interactive approach. This is the main reason by the huge difference in this parameter. Again, no expert knowledge was needed to achieve such improvement. During the optimization process, the user observed that the S11 parameter, similarly to the parameter S21, was improving very slowly. Therefore the user also increased the weight (priority) of the S11 parameter in the iMTGSPICE tool and reduced the weight of other parameters, which achieved more easily the desired specifications. The weight redistribution was carried out a few times, for example, after the user observed the stagnation of the parameters aforementioned by dozens of iterations of the genetic algorithm. Fig. 4 illustrates the forward gain (S21) achieved by solutions obtained by the non-interactive and interactive approaches for the LNA_130 (a) and LNA_65 (b).

Regarding the LNA_130 in Fig. 4 (a), it is observed that the solution obtained by the interactive approach achieved a higher forward gain than the other one obtained by the non-interactive approach, which is also better centered in the operation frequency of 2.4 GHz. Analyzing the LNA_65 [Fig. 4 (b)], the interactive approach also obtained a higher forward gain in the operation frequency in relation the non-interactive method. Although both solutions of the LNA_65 are accurately tuned in the operation frequency, the solution obtained by the interactive approach better rejects frequencies out of the operation frequency, that is, it is more selective than the solution obtained by the non-interactive method.

The input reflection coefficient (S11) obtained by solutions obtained by the non-interactive and interactive approaches are illustrated in Fig. 5, regarding the LNA_130 (a) and LNA_65 (b).

Regarding the LNA_130 and LNA_65, we can observe in Fig. 5 that the solution obtained by the interactive approach achieved the best profile, that is, in the operation frequency of 2.4 GHz the S11 parameter is better minimized and better tuned than in the profile obtained by the non-interactive approach.

Fig. 6 illustrates the noise figure achieved by solutions obtained by the non-interactive and interactive approaches for the LNA_130 (a) and LNA_65 (b).

Analyzing the LNA_130 in Fig. 6 (a), we can observe that the solutions obtained by both approaches achieved similar profiles, although the non-interactive approach obtained a NF smaller (better) than the interactive approach in the operation frequency of 2.4 GHz. Regarding the LNA_65 in Fig. 6 (b), it is observed that the solutions obtained by both approaches, interactive and non-interactive, achieved proper profiles for the NF curve, that is, at frequencies around 2.4 GHz both approaches obtained similar values for the NF parameter, which comply with the required specifications.

It is important to note that, during the optimization process, the user can redistribute weights (priorities) of the specifications, assigning higher weight values for the specifications that are more difficult to achieve. This weight adjustment can be carried out several times during the search process until reaching all specifications at the same time and with robustness in relation to the manufacturing process, supply voltage and temperature variations. In addition, it was observed through Figs. 4 and 5 that this interactive process usually also improves the profile of these curves, since the user guides the optimization process for the design regions that maximize the performance of the specifications, which contributes for achieving the best profile of the curves obtained by the interactive method in relation to the conventional non-interactive.

Based on the results presented previously, we can conclude that the interactive approach with the GA was capable of significantly improving most FoMs in relation to the conventional non-interactive approach. The superiority of the interactive method is due to the combination of the human and artificial intelligences during the optimization process. A non-expert designer was able to tune the optimization process by changing weight values (priorities) of the design specifications in real time during the optimization process in the iMTGSPICE tool in order to prioritize the optimization of the parameters that have greater difficulty in meeting the required specifications.

5.1 The design optimization cycle times

The optimization cycle times for the design of the LNA_130 are: 341 min. for the non-interactive approach and 19.8 min. for the interactive approach. In addition, the optimization cycle times for the design of the LNA_65 are: 536.5 min. and 453.6 min. for non-interactive and interactive approaches, respectively. Each optimization cycle time value represent the time necessary to perform the LNA design, encompassing the time required to obtain the best robust solution in relation to the manufacturing process, supply voltage and temperature variations, considering typical and robustness analyses (corner analysis and Monte Carlo analysis). Moreover, for the interactive approach, the optimization cycle times also take into consideration the time spent by the designer.

We observed that the optimization processes regarding the interactive approach of iMTGSPICE are capable of reducing the optimization cycle times of the LNA_130 and LNA_65 designs in relation to the other ones found by using the conventional non-interactive optimization processes with the GA in 94% and 16%, respectively.

It is important to observe that the optimization times of the LNA_65 are higher than those obtained by the LNA_130 because the SPICE simulation models used by the LNA_65 are far more complex than the models used by the LNA_130. The 130 nm technology has 114 parameters (BSIM 3), whereas the 65 nm technology has 1863 parameters (BSIM 4).

Therefore, the interactive optimization process by using the iMTGSPICE might be a useful approach to help not only experts in RF design, but also non specialists in RF design to achieve the desired specifications in a very reduced design cycle time [13], [14], [15].

5.2 The LNA robustness

To perform a detailed robustness analysis regarding the solutions obtained by each approach (automatic optimization with conventional GA and interactive optimization using iMTGSPICE assisted by a non-expert designer), we performed the Monte Carlo analysis for each solution obtained by each approach of each LNA. Afterwards, we have obtained the minimum and maximum values of each FoM of the LNAs, regarding one potential solution obtained by the automatic optimization process with the conventional GA and one potential solution obtained by the non-expert designer by using the interactive optimization process with the iMTGSPICE. Next, the robustness value (ɛSol) of each potential solution was calculated. The criterion used to identify the most robust solution was the one that presented the highest maximization of the desired specifications (highest ɛSol). Table 5 presents the values of the deviations regarding the main FoMs of the LNA_130 and LNA_65 in relation to the desired specifications in Table 1 and the corresponding values of ɛSol regarding each approach considered in this study.

It is important to note that a relative deviation greater than 100% means that the FoM value obtained by the optimization process is more than twice the value of the desired specification considered. Similarly, if a FoM obtained by the optimization process were worse than the specification in Table 1, the relative deviation would result negative.

Analyzing Table 5, regarding the LNA_130 and LNA_65, respectively, we can observe that the interactive optimization processes using the iMTGSPICE assisted by a non-expert designer obtained the values ɛSol 29.9%, and 50.6% higher than those obtained by the non-interactive approach. It means that the interactive approach achieved the highest average deviations regarding the maximization (improvement) of the main FoMs after the Monte Carlo analysis, i.e. they achieved the most robust design solutions.

The higher performance of the proposed interactive evolutionary approach in relation to the non-interactive in terms of optimization cycle time and robustness is due to the consideration of a beginner designer knowledge in the optimization process. These results demonstrate that the interactive approach of the iMTGSPICE is capable of helping not only expert but also non-expert designers of RF circuits to find robust potential solutions [13], [14], [15]. However, it is necessary to emphasize that the user needs to have a basic training about the use of the iMTGSPICE to be aware of how the parameters of the genetic algorithm interfere in the search process and that the design of an analog IC has specifications that are competitive with each other (for example, voltage gain and unit voltage gain frequency), that is, it is not possible to improve all specifications at the same time. Nevertheless, this does not mean that the user of the optimization tool needs to know how the tradeoffs among the specifications work. He can acquire this knowledge by analyzing the optimization process in real time and in this way he may be able to optimize an analog IC even without being an expert.

6 Conclusion

This paper proposed an interactive approach using the genetic algorithm to optimize CMOS RFICs, which was integrated to the in-house optimization tool named iMTGSPICE. This computational tool includes corner and Monte Carlo analyses in the loop of the optimization processes. Two experiments were carried out aiming the optimization of a LNA optimized in two technology nodes (130 nm and 65 nm) in order to evaluate this innovative evolutionary optimization approach. The first optimization process used the interactive approach of the iMTGSPICE, which was assisted by a beginner designer, who has not specific knowledge in CMOS RFICs designs. The second one was performed by the conventional non-interactive approach with the GA. The experimental results demonstrated that the interactive approach with the GA was capable of remarkably reducing the optimization cycle times of the LNA design, from 16 to 94%, in relation to the conventional GA approach. Moreover, the interactive approach with the GA obtained the most robust potential solutions taking into account the manufacturing process, supply voltage and temperature variations, with improvement in their average robustness values from 30% to 51% in relation to the non-interactive approach with the GA, regarding the values of the deviations of the main FoMs of the LNA in relation to the desired specifications. These results demonstrate that the iMTGSPICE is capable of exploiting expert knowledge to obtain robust potential solutions in a reduced design cycle time.

References

Póvoa, R., Bastos, I., Lourenço, N., & Horta, N. (2016). Automatic synthesis of RF front-end blocks using multi-objective evolutionary techniques. Integration, the VLSI Journal, 52(1), 243–252.

Sabry, M. N., Omran, H., & Dessouky, M. (2018). Systematic design and optimization of operational transconductance amplifier using gm/ID design methodology. Microelectronics Journal, 75(5), 87–96.

Silveira, F., Flandre, D., & Jespers, P. G. A. (1996). A gm/ID based methodology for the design of CMOS Analog circuits and Its application to the synthesis of a silicon-on-insulator micropower OTA. IEEE Journal of Solid-State Circuits, 31(9), 1314–1319.

Martins, R., et al. (2019). Two-step RF IC block synthesis with pre-optimized inductors and full layout generation in-the-loop. IEEE Transaction on Computer-Aided Design Integrated Circuits and Systems, 38(6), 989–1002.

Liu, B., Deferm, N., Zhao, D., Reynaert, P., & Gielen, G. G. E. (2012). An efficient high-frequency linear RF amplifier synthesis method based on evolutionary computation and machine learning techniques. IEEE Transaction on Computer-Aided Design Integrated Circuits Systems, 31(7), 981–993.

Póvoa, R., Lourenço, N., Martins, R., Canelas, A., Horta, N., & Goes, J. (2020). A folded voltage-combiners biased amplifier for low voltage and high energy-efficiency applications. IEEE Transactions on Circuits and Systems II: Express Briefs, 67(2), 230–234.

Canelas, A., Póvoa, R., Martins, R., Lourenço, N., Guilherme, J., Carvalho, J. P., & Horta, N. (2020). FUZYE: A Fuzzy C-means Analog IC Yield optimization using evolutionary-based algorithms. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 39(1), 1–13.

Lourenço, N., & Horta, N. (2012). GENOM-POF: Multi-objective evolutionary synthesis of analog ICs with corners validation. Philadelphia, USA: In Genetic and Evolutionary Computation Conf.

Bush, B. J., & Sayama, H. (2011). Hyperinteractive evolutionary computation. IEEE Transaction Evolutionary Computation, 15(3), 424–433.

Yamaguchi, G., Fukumoto, M. (2019). A music recommendation system based on melody creation by interactive GA. In 20th IEEE/ACIS International Conference on Software Engineering, Artificial Intelligence, Networking and Parallel/Distributed Computing (SNPD).

Brintrup, A. M., Ramsden, J., Takagi, H., & Tiwari, A. (2008). Ergonomic chair design by fusing qualitative and quantitative criteria using interactive genetic algorithms. IEEE Transaction Evolutionary Computation, 12(3), 343–354.

Parmee, I. C. (2002). Improving problem definition through interactive evolutionary computation. Artificial Intelligence for Engineering Design, Analysis, and Manufacturing, 16(3), 185–202.

Moreto, R. A. L., Thomaz, C. E., & Gimenez, S. P. (2019a). Impact of designer knowledge in the interactive evolutionary optimisation of analogue CMOS ICs by using iMTGSPICE. Electronics Letters, 55(1), 16–18.

Moreto, R. A. L., Thomaz, C. E., Gimenez, S. P. (2018). Automatic optimization of robust analog CMOS ICs: An interactive genetic algorithm driven by human knowledge. In proc. of the SBCCI 2018, Bento Gonçalves, Rio Grande do Sul, Brazil.

Moreto, R. A. L., Rocha, D., Thomaz, C. E., Mariano, A., Gimenez, S. P. (2019). Interactive Evolutionary Approach to Reduce the Optimization Cycle Time of a Low Noise Amplifier. In proc. of the SBCCI 2019, São Paulo, São Paulo, Brazil.

Souza, M. De, Mariano, A., & Taris, Thierry (2017). Reconfigurable Inductorless Wideband CMOS LNA for Wireless Communications. IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., 64 (3), 675–685.

Taris, T., Mabrouki, A., Kraimia, H., Deval, Y., & Begueret, J. -B. (2010). Reconfigurable Ultra low power LNA for 2.4GHz wireless sensor networks. In proc. of the IEEE Int. Conf. on Electronics, Circuits and Systems, Athens, Greece.

Spice Opus (c) version 2.32. Revision: 216. Circuit Simulator. Oct. 17 (2017). University of ljubljana slovenia. Faculty of electrical engineering. Group for Computer Aided Design. Retrieved March 4 2020 http://www.spiceopus.si/.

Moreto, R. A. L., Thomaz, C. E., & Gimenez, S. P. (2019b). A customized genetic algorithm with in-loop robustness analyses to boost the optimization process of analog CMOS ICs. Microelectronics Journal, 92(10), 1–12.

Moreto, R. A. L., Thomaz, C. E., & Gimenez, S. P. (2017). Gaussian fitness functions for optimizing analog CMOS integrated circuits. Transaction Computation-Aided Design Integration Circuits System, 36(10), 1620–1632.

Moreto, R. A. L., Gimenez, S. P., Thomaz, C. E. (2013). Analysis of a new evolutionary system elitism for improving the optimization of a CMOS OTA. In Proc. of the 1st BRICS Countries Congress (BRICS-CCI), CI Applications in Industry Symposium, Recife, Pernambuco, Brazil.

MOSIS Educational Program (MEP). Retrieved March 10 2020 http://www.mosis.com/.

Taiwan Semiconductor Manufacturing Company (TSMC). Retrieved March 10 2020 https://www.tsmc.com/.

Tuma, Tadej, & Bűrmen, Árpád. (2009). Circuit simulation with SPICE OPUS theory and practice. Birkhäuser Boston.

Acknowledgments

The authors would like to thank the São Paulo Research Foundation (FAPESP) – Grant #2018/21341-4, Coordenação de Aperfeiçoamento de Pessoal de Nível Superior – Brasil (CAPES) – Finance Code 001 and Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq) – Grant #307804/2019-4 for their financial supports.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

de Lima Moreto, R.A., Mariano, A., Thomaz, C.E. et al. Optimization of a low noise amplifier with two technology nodes using an interactive evolutionary approach. Analog Integr Circ Sig Process 106, 307–319 (2021). https://doi.org/10.1007/s10470-020-01755-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01755-1