Abstract

This study focuses on 10 Gbit/s differential transimpedance amplifier. At the beginning of the work, the amplifier circuit is deeply analyzed and is optimized for the best phase linearity over the bandwidth resulted in a group delay variation less than 1 ps. The amplifier circuit is designed with 0.35 μm SiGe heterojunction bipolar transistor BICMOS process. 9 GHz bandwidth, almost 58 dBΩ transimpedance gain with less than 11.18 pA/\( \sqrt {\text{Hz}} \) averaged input-referred noise current are achieved. Electrical sensitivity is 15 μApp. Power consumption is 71 mW at 3.3 V single power supply.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Transimpedance amplifier (TIA) is the most critical part of the fiber optical front-ends and its design is the most challenging and care demanding part of the optical amplifier design, because it is located at the right after photodiode and converts electrical current to the voltage. Very high bandwidth and low-noise TIAs are needed for 10 Gbit/s and beyond data rates applications. These applications, therefore, require devices with high transition frequencies (f T). Until recent years, high-cost III–V semiconductor technologies, such as GaAs and InP, dominated the optical front-ends and receivers [1, 2] because they exhibited excellent performance in speed and noise. These technologies also have high junction break-down voltage which is not strictly necessary for TIAs, because the output swing of the fiber optical amplifiers usually lower than 1 V. Silicon based bipolar TIAs were also presented. The major demerit of the Si-bipolar TIAs was that they generally showed poor noise performance and lower sensitivity [3]. CMOS process is also becoming a low cost, low power choice for lower data rates [4]. Bipolar transistors, however, are faster than CMOS transistors for the same size and higher transconductance can be achieved. SiGe heterojunction bipolar technology (HBT) has recently provided a cost-effective alternative and higher integration levels, especially in BICMOS process, with improved sensitivity for 10 Gbit/s fiber optical front-ends and for the development of photoreceivers. One of the most important advantages of the SiGe BICMOS technology is that it enables analog and digital parts of the optical receiver to be integrated in the same chip. In that case, output drivers and output impedance matching networks are avoided. Since SiGe simultaneously enables high speed and low power consumption, it is becoming an important choice for the realization of high speed fiber optical receivers.

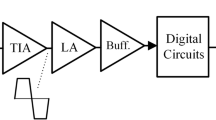

Block diagram of a typical fiber optical receiver is shown in Fig. 1. The optical signal is detected and converted to an electrical current by a photodiode. A TIA converts the electrical current to a voltage and amplifies it. This quantity of amplification is not sufficient for signal processing. Therefore, right after TIA, a main amplifier (MA), which is voltage amplifier, amplifies the signal higher amplitudes. This makes data pulses coming from fiber optics safely be detectable and processed at the subsequent stages. MA could be in the form of automatic gain control amplifier (AGC) enabling transimpedance gain of the front-end to be lowered for large input signals or in the form of limiting amplifier (LA) which limits the output signal for large input signals. If low distortion is strictly necessary, then AGC must be preferred. In other case, where distortion can be ignored, then LA is preferred because of its simplicity.

Clock and data recovery (CDR) extracts the digital data and clock information from the received signal. This is done by defining threshold voltage. The pulse is assigned to “1” when the pulse amplitude above the threshold voltage. In other case, pulse amplitude is lower than threshold voltage, the pulse is assigned to “0”. During extraction of clock data from the signal, CDR decides at the mid-point of the pulse in order to lower bit error rate (BER). The recovered data are finally demultiplexed as parallel channels having lower data rates.

In addition to low power and single supply operation, TIA must exhibit low-noise and linear phase response in order to be used for 10 Gbit/s applications. Trade-off between noise, speed, gain and supply voltage present many challenges in TIA design. Since TIA dominates noise of the overall receiver, its bandwidth should be limited to minimize noise. On the other hand, because of the limited bandwidth, TIA can produce intersymbol interference (ISI) which lowers BER. A group delay variation of the frequency response over the specified bandwidth is another important performance parameter. Typical group delay variation for 10 Gbit/s applications to minimize data-dependent jitter is \( \left| { \Updelta \tau } \right| < 10 \;{\text{ps}} \) [5, 6]. The overall sensitivity of the receiver is determined by the TIA, because TIA is the first electrical part of the receiver after photodiode. Sensitivity of an optical front-end is defined in terms of electrical and optical. As given in (1), electrical sensitivity i sens is the required minimum peak-to-peak current at the input of the receiver to achieve specified BER. Optical sensitivity P sens in Eq. (2) includes responsivity of the photodiode and is defined in terms of averaged optical power necessary to achieve minimum specified BER. In Eqs. (1) and (2), R is the responsivity of the photodiode, \( \overline{{i_{n} }} \) is the total integrated input-referred noise current of the receiver; Q is a measure of the ratio between signal and noise. Minimum required BER at 10 Gbit/s bit rate is 10−12, and Q is 7.035 at BER of 10−12 [6].

This study presents a differential, low-noise transimpedance amplifier for 10 Gbit/s fiber links using 0.35 μm SiGe HBT BICMOS process, which is well suited for 10 Gbit/s photoreceivers. In Sect. 2, theoretical basics of the proposed TIA are investigated and design is achieved. Section 3 gives the simulation results and Sect. 4 concludes the study.

2 Circuit design

As a first stage, TIA must have a very little group delay deviation from the low frequencies up to high frequencies, because time jitter caused by excessive group delay variation cannot be compensated for at the succeeding stages. In contrast, a drop in signal magnitude at higher frequencies can be improved by using MA after the TIA. For that case, lowering the group delay variation over the bandwidth was one of the major issues during the design. Since MA is differential, differential operation must be fulfilled. For single-ended output TIA, this can be done by applying reference voltage to the one input of the MA and applying TIA output to the other input [7]. This technique requires design of reference voltage generator circuit. In other case, TIA is designed in differential architecture having differential outputs. The latter makes the TIA immune to any common mode noise so in this case it is preferred over the single-ended structure. However, the input-referred noise power of the differential TIA is twice than that of the single-ended structure.

Cascode [8] and inductive peaking [9] techniques including active inductive peaking [10] were the alternative choices to reach desired bandwidth (around 8–9 GHz) for the TIA. Broadband operation, however, has been fulfilled without using these techniques since f T of the technology, which is around 70 GHz, relatively enough for 10 Gbit/s speed to achieve desired bandwidth. Common-emitter with shunt-feedback resistor is used in the design because of its good noise performance over the common-base structure.

Differential SiGe TIA schematic is shown in Fig. 2. The PIN photodiode with the intrinsic capacitance of 100 fF is assumed at the input of the front-end. Since photodiode output is single-ended, current from the photodiode is directed to the only one input of the TIA (T 1). In this case, photodiode capacitance C P is replicated at the other input (T 2) to achieve fully symmetrical operation. This can be done during chip design by placing dummy photodiode to the unused input (T 2) or by calculating the total capacitance at the input (T 1), including parasitic capacitances, and placing that total capacitance at the unused input (T 2) [11]. The dominant pole of the TIA is determined by the time constant at the input node of the TIA. Shunt-feedback resistors R F are applied around voltage amplifier to reduce input impedance, which also reduces time constant at the input nodes allowing −3 dB cut-off frequency to be higher. Emitter followers (T 3, T 4, T 5, T 6) are used for DC level shifting and as buffer to drive next stages. The outputs are isolated from the feedback networks in order to prevent transimpedance gain and bandwidth from degradation because of the loading effect of the subsequent stage. Current mirrors are used as loads in order to neglect high value resistors from the design. All diode connected transistors are needed for level shifting in order to keep V CE less than break-down voltage. Beta helper (T 8) and emitter degeneration resistors are used at the biasing circuit in order to improve current matching performance of the current mirrors.

For extracting transfer function and noise equations, half-circuit model of the differential TIA is used as shown in Fig. 3. The TIA has a voltage amplifier and a shunt-feedback resistor R F. I 3 and I 5 are the current sources representing the current mirrors. Voltage gain of the emitter follower at the last stage is assumed approximately one. T 1 and T 3 are accepted as the same transistors. Voltage amplifier is only modeled with dominant pole. With the help of [6, 12–14] transimpedance Z T is

where,

C μ is the base–collector capacitance; C cs is the collector–substrate capacitance and C t is the total capacitance at the input of the TIA. r b is the intrinsic base resistance; r π and C π base–emitter resistance and capacitance, respectively. A o is the open loop DC voltage gain. From (3), DC transimpedance gain R T is

In a second order system, the damping factor must be equal to \( \frac{\sqrt 3 }{2} \) in order to obtain Bessel response which has a maximally flat group delay in the pass band. Using \( \frac{\sqrt 3 }{2} \) in Eq. (3), bandwidth of the TIA is as follows;

This result mandates that bandwidth of the voltage amplifier must be a factor 3 larger than the unity-gain frequency of the open-loop response [12]. Since, input transistors T 1 and T 2 are biased for highest f T, R C and R f are the major design parameters to obtain maximally linear phase response. R f is also restricted by the transimpedance gain and noise parameters. Since input impedance directly affects stability of the TIA, HBT with 2 base contacts are chosen in order to make a compromise between base resistance and base parasitic capacitance. R C and R f are chosen as 900 and 150 Ω, respectively [13].

Equivalent input-referred noise current spectrum \( \overline{{i_{{n,{\text{in}}}}^{2} }} \) of the half-circuit of the proposed shunt-feedback TIA given in Fig. 2 can be written as;

where,

k is the Boltzmann constant, T is the temperature in kelvin and q is the electric charge. \( \overline{{v_{n3}^{2} }} \) and \( \overline{{v_{n5}^{2} }} \) are the equivalent input-referred noise voltage generators at the input of the T 3 and T 5, respectively. For complete circuit \( \overline{{i_{{n,{\text{in}}}}^{2} }} \) is twice that given in Eq. (11). Dominant noise sources are base and collector shot noise sources of the input transistors T 1 and T 2 [3rd and 4th terms in Eq. (11)] and thermal noise sources from R f feedback resistors and intrinsic base resistances r b [first and second terms in Eq. (11)]. Since low frequency corner of fiber communications is a couple of kHz, flicker and popcorn noise sources can be neglected. Increasing the value of R f will decrease the noise and bandwidth but also will increase the low-frequency transimpedance gain. Photodiode capacitance, C P, directly affects noise performance of the TIA as shown in Eq. (11). This is also depicted in Fig. 4. In this case, C P is swept from 50 fF to the 250 fF. As C P becomes higher, noise of the circuit increases for the same operating frequency after around 1 GHz.

3 Simulation results

Simulation is performed with the technology of 0.35 μ SiGe HBT BICMOS process whose f T is about 70 GHz. Figure 5 shows differential transimpedance gain of the SiGe TIA. Flat frequency response is obtained. Bandwidth is 9 GHz and low frequency differential transimpedance gain is 57.93 dBΩ. Figure 6 depicts group delay variation over the frequency. Less than 1 ps variation over the bandwidth is obtained.

Input-referred noise current simulation is shown in Fig. 7. Noise current is below 7 pA/\( \sqrt {\text{Hz}} \) up to 1 GHz, and it is below 11 pA/\( \sqrt {\text{Hz}} \) between 1 and 9 GHz. Total integrated input-referred noise current \( \overline{{i_{n} }} \) is calculated as 1.061 μA. 14 GHz noise bandwidth is taken into account to calculate \( \overline{{i_{n} }} \). As expected, noise is dominated by base and collector shot noise and thermal noise of the base resistance of the input transistors T 1 and T 2 (66 % of the total noise). Feedback resistors R f contribute to the noise around 22 %. Using the Eq. (1), sensitivity of the differential TIA at BER of 10−12 is calculated as 15 μApp. Maximum peak-to-peak input current of the TIA is 400 μApp. Although linearity of the signal is preserved up to 1 mApp input current levels, higher peak-to-peak currents than 400 μApp will cause V CE of the T 1 and T 2 to exceed collector–emitter junction break-down voltage.

Figure 8 shows single-ended S22 parameter of the proposed circuit. The proposed differential TIA is intended for integrated receiver compromising both TIA and MA on the same chip. If differential TIA is not implemented on the same chip with the MA, then TIA must have capability to drive 50 Ω loads. Hence, 30 Ω resistors are added to the both outputs for impedance matching. Good matching is achieved with S22 less than −15 dB over the bandwidth. Adding matching resistors causes 5 dBΩ loss to the mid-band transimpedance gain for a single-ended output.

Differential output waveform of the TIA is depicted in Fig. 9. The TIA input is driven with a NRZ data stream of 10 Gbit/s and 231−1 pseudo random bit sequence (PRBS) with the amplitude of 15 and 300 μApp. Differential output swing is 12 and 320 mVpp, respectively. Eye diagram simulations resulted in a wide eye opening shown in Fig. 10. The TIA outputs are loaded with 100 fF capacitors in the first case [15] and loaded with 50 Ω loads in the second case. In the latter, 30 Ω matching resistors are added to the both outputs. The eye openings are clear for both horizontal and vertical openings.

Eye diagrams of the differential output at 10 Gbit/s 231−1 PRBS data stream. a Input current is 15 μApp, both outputs are loaded with 100 fF capacitors. b Input current is 300 μApp, both outputs are loaded with 100 fF capacitors. c Input current is 15 μApp, both outputs are loaded with 50 Ω resistors. d Input current is 300 μApp, both outputs are loaded with 50 Ω resistors. In the case of c and d 30 Ω matching resistors are added to the both outputs

Table 1 shows simulation performance of the proposed circuit with some existing circuit and designs. III–V technologies such as GaAs and InP has recently not preferred in photoreceivers because they are power hungry devices for the same speed. They are also generally not cheap. In Refs. [16] and [17], there are not noise and sensitivity results. CMOS has lower transimpedance for the same speed. Another performance parameter of TIAs is group delay variation. The proposed circuit has very good group delay variation performance (less than 1 ps). This is shown with transient waveforms having little distortion.

4 Conclusions

The differential SiGe transimpedance amplifier and simulation results for 10 Gbit/s fiber optical receivers are presented. No inductor is used to achieve wideband operation. 0.35 μ SiGe HBT BICMOS technology enables TIA to be a cost-effective alternative and to be combined with digital blocks of the fiber optical receiver. The differential structure of the TIA makes it immune to the effect of the supply and substrate noise. Table 1 summarizes the simulation results of the proposed differential SiGe TIA. The TIA bandwidth is 9 GHz with little non-linear phase response and differential transimpedance gain is almost 58 dBΩ. The electrical sensitivity of the proposed TIA is 15 μApp. Power consumption is 71 mW and maximum differential output swing is 320 mVpp. It is shown that the differential TIA is well-suited for 10 Gbit/s data rate fiber optical receivers.

References

Jung, D. Y., Park, S. H., Lee, K. H., Chang, W. J., Nam, E. S., Lim, J. W., & Park, C. S. (2002). An InGaP/GaAs HBT transimpedance amplifier for 10 Gb/s optical communication. 3rd International Conference on Microwave and Millimeter Wave Technology, ICMMT, pp. 974–977.

Fukuyarna, H., Murata, K., Sano, K., Kitabayashi, H., Yamane, Y., Enoki, T., & Sugahara, H. (2003). Optical receiver module using an InP HEMT transimpedance amplifier for over 40 Gbit/s. IEEE Gallium Arsenide Integrated Circuit Symposium, 25th Annual Technical Digest, pp. 237–240.

Lu, Y., & El-Gamal, M. N. (2001). A 2.3 V low noise, low power, 10 GHz bandwidth Si-bipolar transimpedance preamplifier for optical receiver front-ends. IEEE International Symposium on Circuits and Systems, ISCAS, vol. 4. pp. 834–837.

Tang, W., & Plant, D. V. (2006). A low power 3.125 Gb/s/channel parallel optical receiver for very short reach applications. 23rd Biennial Symposium on Communications, pp. 35–38.

Razavi, B. (2003). Design of integrated circuits for optical communications. Los Angeles, USA: McGraw-hill.

Sackinger, E. (2005). Broadband circuits for optical fiber communication. New Jersey, USA: Wiley-Interscience.

Vatannia, S., Yeung, P., & Lu, C. (2005). A fast response 155-Mb/s burst-mode optical receiver for PON. IEEE Photonics Technology Letters, 17(5), 1067–1069.

Rieh, J.-S., Qasaimeh, O., Klotzkin, D., Lu, L.-H., Yang, K., Katehi, L. P. B., Bhattacharya, P., & Croke, E. T. (1997). Monolithically integrated SiGe/Si PIN HBT front-end transimpedance photoreceivers. IEEE/Cornell Conference on Advanced Concepts in High Speed Semiconductor Devices and Circuits, pp. 322–331.

Jin, J. D., & Hsu, S. (2008). A 75-dBΩ 10-Gb/s transimpedance amplifier in 0.18-μm CMOS technology. Photonics Technology Letters, IEEE, 20(24), 2177–2179.

Han, L., Yu, M., & Zong, L. (2010). Bandwidth ehancement for transimpedance ampilfier in CMOS process. 3rd International Conference on Biomedical Engineering and Informatics (BMEI), vol: 7, pp. 2839–2842.

Kim, H. H., Chandrasekhar, S., Burrus, C. A., & Bauman, J. (2001). A Si BiCMOS transimpedance amplifier for 1 OGb/s SONET receiver. IEEE Journal of Solid-State Circuits, SC, 6(5), 769–776.

Hermans, C., & Steyaert, M. (2007). Broadband opto electrical receivers in standard CMOS. Dordrecht, The Netherlands: Springer.

Akbey Y., & Palamutcuogulları O. (2011). 9 GHz differential SiGe transimpedance amplifier for 10 Gbit/s fiber optical front-ends. 7th International Conference on Electrical and Electronics Engineering (ELECO), pp. II-250–II-254.

EL-Diwany, M. H., Roulston, D. J., & Chamberlain S. G. (1981). Design of low-noise bipolar transimpedance preamplifiers for optical receivers. IEE Proceedings-Part G, Electronic Circuits and Systems 128 (pp. 299–305).

Samadi, M. R., Karsilayan, A. I. & Silva-Martinez, J. (2002). Design of transimpedance and limiting amplifiers for 10 Gb/s optical communication systems. 45th Midwest Symposium on Circuits and Systems, MWSCAS, vol. 3, pp. 164–167.

Fenfei H., & Jingxing D. (2008). 0.35 μm SiGe BiCMOS front-end amplifier for 10 Gb/s optical receiver. International Conference on Microwave and Millimeter Wave Technology, ICMMT, pp. 249–252.

Zhou L., Wu D., Wu J., Jin Z., & Liu X. (2012). Design of a 10 GHz bandwidth variable gain amplifier using a GaAs HBT technology. International Workshop on Microwave and Millimeter Wave Circuits and System Technology, MMWCST, pp. 1–4.

Huang T., Zhang Q., & Zhang W. (2011). A novel transimpedance amplifier for 10 Gbit/s optical communication system. IEEE 9th International Conference on ASIC, ASICON, pp. 843–846.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Akbey, Y., Palatmutcuogullari, O. A broadband, differential transimpedance amplifier in 0.35 μm SiGe BICMOS technology for 10 Gbit/s fiber optical front-ends. Analog Integr Circ Sig Process 74, 155–162 (2013). https://doi.org/10.1007/s10470-012-9949-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-012-9949-x