Abstract

The complex process of semiconductor device design requires precise models and efficient optimizers. This article puts forward an Asymmetrical Hetero-Dielectric (AHD) Triple Material Gate (TMG) n-type Junctionless Tunnel Field Effect Transistor (JL-TFET). A higher gate control is achieved by using triple material in control gate and hetero-dielectric oxide, which results in high ON current and low leakage. The surface potential based model for the proposed structure is derived by analytically solving 2-D Poisson’s equation with hetero-dielectric gate oxide. This work also adopts intelligent techniques for extraction of optimal model parameters by using the derived mathematical model for the proposed JLTFET structure. The optimization technique used in this work combines the advantage of Particle Swarm Optimization (PSO) algorithm and Differential Evolution (DE) algorithm. A comparison with the conventional design process reflects that the use of optimization technique provides a novel approach to tune the process parameters. This technique outperforms the state of art design techniques and provides best accuracy along with exceptional computational efficiency. A current ratio of 1.25 × 1010 A and Point Subthreshold Swing (SS) values of 9 mV/dec and average SS of 48 mV/dec is achieved by optimizing the proposed structure.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Tunnel field effect transistors (TFET) (Bhuwalka et al. 2005; Bhuwalka et al. 2006) with Subthreshold Slope (SS) below 60 have become the adroit candidate for low power applications. However, with shrinking device dimension, the fabrication of semiconductor based devices with abrupt junctions became increasingly complex (Pratap et al. 2016). Thus, Junctionless TFET (JL-TFET) were proposed (Ghosh and Akram 2013) with uniform doping throughout the device and no abrupt junction, thereby reducing fabrication complexity (Damrongplasit et al. 2013; Gundapaneni et al. 2012). The JLTFET combines the concept of JLFET and TFET, where an N + N+N + structure can be converted into a PIN structure by effectively controlling the polar gate work function (Ghosh and Akram 2013). This work incorporates the concept of JLTFET with triple material gate (TMG) (Bagga et al. 2015; Vanitha et al. 2015; Dewan et al. 2016) along with the use of asymmetric hetero-dielectric in a Si based structure. The proposed structure is found to improve the current ratio, SS and comparatively involves less fabrication complexity (Toh et al. 2007). The use of asymmetric dual k is known to improve the electric field across the junction (Raushan et al. 2018) and thereby increasing the ON current. Although, a number of models have been proposed for JLTFET (Ghosh and Akram 2013; Bal et al. 2014; Akram et al. 2014), but the analytical model for TMG AHD JLTFET is introduced for the first time in this work. The proposed structure is analytically solved for the expression of surface potential. The derived expression is then used as a tool to optimize the structure. The sole theory is to amalgamate the above three concept in a single device and study its impact. However, state of art techniques in semiconductor design involves rigorous process of tuning the design parameters and re-simulating the structure to achieve the specified target. Thus, these empirical techniques have become a bottleneck for semiconductor device designers. Therefore, this paper highlights the use of optimization algorithms to tune the device parameters. The surface potential model incorporates all physical effects even in downscaled devices. Thus, surface potential based model for the proposed device is derived and is used to optimize the structure. The traditional optimization approaches such as numerical based approaches (Pinnau 2007), derivative based techniques (Lian et al. 2018) are known to suffer from local optima stagnation, poor convergence and are not suitable for complex quantum model analysis. This paper uses various modern optimization approaches (Zhang et al. 2009; Talukder 2011; Kameyama 2009; Liu et al. 2014; Storn and Price 1995; Mirjalili and Lewis 2016a, b) to design the structure. However, a hybrid combination of PSO and DE i.e. DEPSO provides the best accuracy as well as computational efficiency for the proposed model. All device simulations are performed in Synopsis TCAD tool (S.I. Association 2015). The optimization algorithms are implemented in MATLAB 2015 version to achieve the target design parameters. This paper has been structured as follows: Sect. 2 describes the device architecture, Sect. 3 illustrates the optimization process, Sect. 4 explains the model derivation, Sect. 5 discusses the results and finally Sect. 6 draws the conclusion.

2 Device Structure

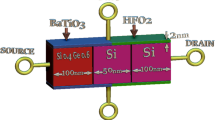

This section illustrates the proposed structure shown in Fig. 1. The structure depicts an n-type Si channel hetero-dielectric double gate Junctionless TFET. A uniform doping concentration of 1 × 1019 cm−3 is used throughout the device, thus making a Junctionless TFET easier to fabricate (Bal et al. 2014). The device structure consists of two isolated gates: Polar gate nearer to the source for generating P + region and control gate in middle to create channel.

The polar gate is biased at 0 V (Bal et al. 2014). A triple material configuration is used for controlling the gate with different metal M1 (auxiliary), M2 (control), and M3 (tunnel). Each metal gate has different work function \(\Phi_{1} ,\Phi_{2}\ and\ \Phi_{3}\) and length L1, L2 and L3. Proper tuning of control gate work function will result in better current ratio. The inclusion of spacer between two gates helps in reducing the coupling between the two gates (Akram et al. 2014). The dielectric of both polar and control gates is of two different types: high-k (HfO2) near the source and low-k (SiO2) near the drain in two different layers. The use of asymmetric HD layer across front and back gate resulted in improved current characteristics. The effective oxide thickness is calculated as in (Bentrcia et al. 2012). All simulations are performed in Synopsis TCAD tool.

3 Optimization problem formulation

The main concern associated with TFET design is to improve the current ratio and this opens to many novel device structures. A structure can provide its best performance if properly optimized. Thus, optimizing the structure plays a crucial role. This paper makes use of various evolutionary computational algorithms. The algorithms are chosen in such a way that they improve computational efficiency as well as accuracy without compromising the device inherent characteristics. This technique of device optimization requires an objective function. The model for surface potential is derived for the proposed structure. Since, the surface potential based model is quite close to physical prototype and takes into account various physical effects occurring in TFET, it is used as an objective function. Thereby, improving surface potential across the junction will help improving the electric field and, in turn, the ON current also increases. The optimization process is divided into three steps:

3.1 Preprocess

The sensitivity analysis is performed in this process so that the parameters which significantly affect device performance can be sorted. As the device model consists of a large number of parameters, it becomes difficult to handle significant amount of variables. Thus, preprocess aids in data reduction and thereby in limiting the computational complexity. The selection of design variables is divided into certain sections and is done by performing sensitivity analysis. The sensitivity analysis can facilitate understanding the impact of various parameters on the device performance. A set of parameters (say, L1, L2, and L3), are adjusted while others are fixed at certain values to assess the impact on device performance. The device parameters are divided into certain groups and the sensitivity analysis is performed. The parameters which significantly influence the device performance are then selected as design variables and the other least significant parameters are considered as constant. Tables 1 and 2 list out the various design constants and variables used in the optimization process. The choice of material and doping concentrations are kept fixed.

3.2 Parameter extraction/algorithm parameters

A number of modern optimization algorithms such as DEPSO, human behavior based particle swarm optimization (HBPSO) (Liu et al. 2014), particle swarm optimization (PSO) and Whale Optimization Algorithm (WOA) are used to optimize the structure. The effectiveness of different optimization algorithms are evaluated by performing 20 independent runs of each algorithm. This technique is used to evaluate the robustness of the algorithms by considering the best achieved value of the objective function. A comparative analysis reflects that the performance of DEPSO is superior in terms of efficiency and accuracy. The working principle of DEPSO algorithm is explained in the subsequent section.

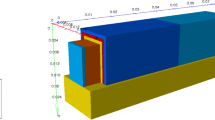

Hybrid DEPSO: The DEPSO algorithm (Zhang et al. 2009) is the hybrid version of the DE and PSO algorithm. The DE has some pros, and it includes its capacity to preserve the diversity of the population and the ability to explore local search. But the algorithm has no means to memorize the preceding process and utilize the global information regarding the search space. Therefore, there will be wastage of computing power and there is a risk for the algorithm to be trapped in local optima. The differential information can be useful for the search ability, but it also leads to instability in some solutions. To get the advantages of both PSO and DE, the hybrid DEPSO algorithm has been designed. Here the PSO algorithm is integrated into DE and thus it results in fast convergence and higher population diversity (Zhang et al. 2009). The algorithm parameters are listed in Table 3 (Fig. 2).

3.3 Post process

Post process involves the validation of the results obtained by optimization algorithm by simulating the results in TCAD simulator.

4 Mathematical Model for the proposed structure

The 2-D Poisson’s equation for potential distribution of channel can be represented as

where, \(N_{ch}\) is the channel doping concentration, \(\varepsilon_{si}\) represents the dielectric constant of Si, L represents the total length of the control gate, \(\phi (x,y)\) is the potential at any point in the channel, q is the charge of electron, and \(t_{si}\) is the thickness of the device.

A parabolic function by Young’s approximation is used to represent potential profile across the channel with \(A_{0}\) being the surface potential which is a function of x and,\(A_{1} \left( x \right),\) \(A_{2} \left( x \right)\) are arbitrary constants:

As three different metals are used M1, M2, M3, thus, the surface potential under each metal can be expressed as

For \(L_{j - 1} \le x \le L_{j}\) and \(0 \le y \le t_{si}\), where j = 1, 2, 3 for M1, M2, M3 and \(\phi_{j}\) is the corresponding potential. \(L_{0}\) is the starting point of the channel i.e. \(L_{0} = 0.\)

As three different materials were used in the gate, they will have different work function and subsequently different flat band where, \(\chi\) is the electron affinity, \(E_{g}\) is the band gap of Silicon at room temperature and \({{\Phi }}_{{\begin{array}{*{20}c} B \\ { } \\ \end{array} }}\) is the bulk potential voltage:

\({{\Phi }}_{{{\text{M}}1}} ,{{\Phi }}_{{{\text{M}}2}} ,{{\Phi }}_{{{\text{M}}3}}\) are the work function of M1, M2, M3 and \({{\Phi }}_{\text{Si }}\) is the silicon work function:

where, thermal voltage, \(V_{T} = \frac{{kT}}{q}\) and \({\text{n}}_{\text{i}}\) is the intrinsic concentration of silicon.

-

1.

In case of TMG the electric field at the front and back gate is continuous

Again for metal M1, the dielectric layer 1 consists of HfO2 and layer 2 consists of SiO2, so the equivalent capacitance can be calculated as

Similarly, for M2, the dielectric layer 1 consists of HfO2 and SiO2 and layer 2 consists of HfO2 only, so the equivalent capacitance can be calculated as

For M3, the entire dielectric layer consists of HfO2

where, \(t_{oxf }\), is the front oxide layer thickness and is equal to layer 2 thickness. Also \(\varepsilon_{{HfO_{2} }} \, and \, \varepsilon_{{SiO_{2} }}\) are permittivity of HfO2 and SiO2.

-

2.

Electric field at the back gate is also continuous at \(y = t_{si}\),

\(C_{oxb} = \frac{{\varepsilon_{{HfO_{2} }} }}{{t_{oxb} }}\), \(\phi_{B}\) is the potential along the back gate oxide, which is same as front gate potential. \(\phi_{B} \left( {x,y} \right) = \left. {\phi \left( {x,y} \right)} \right|_{{y = t_{si} }} .\)

\(\phi_{Bj} \left( {x,y} \right)\) is the corresponding back gate potential and can be expressed as

\(\phi_{j} \left( {x,y = 0} \right) = A_{0j}\), the potential of the channel is the surface potential.

-

3.

Surface potential is similar and continuous at interface

$$\begin{aligned} & \phi_{1} \left( {L_{1} ,0} \right) = \phi_{2} \left( {L_{1} ,0} \right) \\ & \phi_{2} \left( {L_{2} ,0} \right) = \phi_{3} \left( {L_{2} ,0} \right). \\ \end{aligned}$$(9) -

4.

Electric field is similar and continuous at interface

$$\begin{aligned} & \left. {\frac{{d\phi_{1} \left( {x,y} \right)}}{dy}} \right|_{{x = L_{1} }} = \left. {\frac{{d\phi_{2} \left( {x,y} \right)}}{dy}} \right|_{{x = L_{1} }} \\ & \left. {\frac{{d\phi_{2} \left( {x,y} \right)}}{dy}} \right|_{{x = L_{2} }} = \left. {\frac{{d\phi_{3} \left( {x,y} \right)}}{dy}} \right|_{{x = L_{2} }} . \\ \end{aligned}$$(10) -

5.

\(\phi _{1} \left( {0,0} \right) = V_{{bipot}} = V_{T} \ln \left( {\frac{{N_{a} N_{{ch}} }}{{n_{i}^{2} }}} \right)\), where, \({\text{V}}_{\text{bipot}}\) is the built in potential and \({\text{V}}_{\text{DS}}\) is the drain to source voltage. \({\text{N}}_{\text{a}} = {\text{N}}_{\text{d}} = {\text{N}}_{\text{ch}}\) as device is uniformly doped.

-

6.

$$\phi _{3} \left( {L_{3} ,0} \right) = V_{{bipot}} + ~V_{{DS}} = V_{T} \ln \left( {\frac{{N_{d} N_{{ch}} }}{{n_{i}^{2} }}} \right)$$(11)

Solving Eq. (3) the constants can be found and are represented below

Putting the values of the above constants in Eq. (3) and comparing with Eq. (1), we get

where, \(m_{j} = \frac{{2C_{oxb} }}{{C_{s} t_{si} }}\left( {1 + \frac{{C_{oxfj} }}{{C_{s} }} + \frac{{C_{oxfj} }}{{C_{oxb} }}} \right)\)

The surface potential under three regions

where, \(\lambda_{j } = \sqrt {m_{j} }\), j = 1, 2, 3.

The constants U, V, W, X, Y, and Z can be solved by using boundary conditions (6)–…

5 Results validation and discussion

5.1 Device characteristics

Figure 3 depicts the characteristics of the projected device. It illustrates that AHD-TMG-JLTEFT can produce higher ON current compared to conventional JLTFET (Ghosh and Akram 2013) and DMGJLTFET (Bal et al. 2014) if proper work function is chosen. Table 4 reflects the comparison among various JL-TFET.

The OFF current and SS value also shows much improvement compared to conventional device. The impact of polar gate work function variation is portrayed in Fig. 4. The transconductance is also an essential parameter to assess the analog performance of devices, which is defined as the first derivative of drain current (Ids) with respect to VGS, the formula of gm is given by Eq. (16): as shown in Fig. 5, the gm of the AHD-TMG-JLTEFT is found to be 1 × 10−3 S/µm which is much higher as compared to other reported JLTFET:

Figure 6 shows the surface potential plot of simulated and modeled surface potential. The close matching between the plots validates the accuracy of the proposed model. The deviation is little higher in the drain side due to assumption considered while deriving the model. Figure 7 depicts the comparison between the existing structures and the proposed one. The use of triple material gate improves the surface potential across the channel. The use of three gate materials resulted in the step change in surface potential at the metal interface. This increase in surface potential is due to increase in carrier velocity as well as transport efficiency.

5.2 Convergence analysis and optimization results validation

The mathematical model of the proposed structure discussed in Sect. 4 Eq. (15) is optimized using a variety of algorithms such as DEPSO, DE, PSO, HBPSO, and WOA. The main purpose is to maximize the surface potential at the tunnel junction by optimizing the variables in Table 2. All optimization algorithms are implemented in the MATLAB software for obtaining the best values for process parameters and they are listed out in Table 5. The results in Table 5 depict that DEPSO can achieve the most accurate result compared to TCAD simulated result. A comparison plot of surface potential derived from optimization of analytical model by DEPSO algorithm and TCAD simulated model is plotted in Fig. 8. The comparison plot reflects that DEPSO algorithm based optimized structure can achieve higher values of surface potential compared to the values obtained by hit and trail based optimization in TCAD. Thus, use of optimization algorithm can be useful in optimizing device parameters. Further, the convergence plot depicted Fig. 9 reflects that DEPSO algorithm amongst all has better performance with best convergence in surface potential computation. The optimized dimensions achieved via algorithmic technique can be validated by designing the proposed structure with optimized dimension in TCAD software. The small deviation between results obtained from MATLAB and TCAD simulation is due to the rounding of the parameters. The simulated device reports an ON-current of 3 × 10−4 A and OFF-current of 2.4 × 10−14 A.

6 Conclusion

This paper provides a fresh concept to accelerate the tuning process parameters and help in benefiting design process of nano-devices. Finally, the validity of the proposed analytical model is compared with numerical solution simulation data results, which are obtained by using TCAD device simulator. In this article, we have successfully used DEPSO algorithm for surface-potential-based model parameter extraction for proposed TFET structure. Comparison reflects that measured surface potential and the optimized values are quite accurate.

References

Akram MW, Ghosh B, Bal P, Mondal P (2014) P-type double gate junctionless tunnel field effect transistor. J Semicond 35(1):1–7. https://doi.org/10.1088/1674-4926/35/1/014002

Bagga N, Sarkar SK, Member S, Expression A, Potential S (2015) An analytical model for tunnel barrier modulation in triple metal double gate TFET. IEEE Trans Electron Devices 62(7):2136–2142. https://doi.org/10.1109/TED.2015.2434276

Bal P, Ghosh B, Mondal P, Ball MWA, Mani M (2014) Dual material gate junctionless tunnel field effect transistor 230–234. https://doi.org/10.1007/s10825-013-0505-4

Bentrcia T, Djeffal F, Benhaya AH (2012) Continuous analytic I–V model for GS DG MOSFETs including hot-carrier degradation effects. J Semicond. https://doi.org/10.1088/1674-4926/33/1/014001

Bhuwalka KK, Schulze J, Eisele I (2005) Scaling the vertical tunnel FET with tunnel bandgap modulation and gate workfunction engineering. IEEE Trans Electron Devices 52(5):909–917

Bhuwalka KK, Born M, Schindler M, Schmidt M, Sulima T, Eisele I (2006) P-channel tunnel field-effect transistors down to sub-50 nm channel lengths. Jpn J Appl Phys Part 1 Regul Pap Short Notes Rev Pap. https://doi.org/10.1143/jjap.45.3106

Damrongplasit N, Kim SH, Liu TJK (2013) Study of random dopant fluctuation induced variability in the raised-ge-source TFET. IEEE Electron Device Lett. https://doi.org/10.1109/LED.2012.2235404

Dewan MI, Kashem MTB, Subrina S (2016) Characteristic analysis of triple material tri-gate junctionless tunnel field effect transistor. In: 2016 9th International conference on electrical and computer engineering (ICECE), Dhaka, pp 333–336. https://doi.org/10.1109/ICECE.2016.7853924

Ghosh B, Akram MW (2013) Junctionless tunnel field effect transistor. IEEE Electron Device Lett 34(5):584–586. https://doi.org/10.1109/LED.2013.2253752

Gundapaneni S, Bajaj M, Pandey RK, Murali KVRM, Ganguly S, Kottantharayil A (2012) Effect of band-to-band tunneling on junctionless transistors. IEEE Trans Electron Devices. https://doi.org/10.1109/TED.2012.2185800

Gupta SK, Kumar S (2019) Analytical modeling of a triple material double gate TFET with hetero-dielectric gate stack. Silicon 11(3):1355–1369. https://doi.org/10.1007/s12633-018-9932-y

Kameyama K (2009) Particle swarm optimization—a survey. IEICE Trans Inf Syst E92-D(7):1354–1361. https://doi.org/10.1587/transinf.E92.D.1354

Lian X, Zhang W, Zhang C, Liu J (2018) Asynchronous decentralized parallel stochastic gradient descent. In: 35th International conference on machine learning, ICML 2018

Liu H, Xu G, Ding G, Sun Y (2014) Human behavior-based particle swarm optimization. Sci World J 2014:194706. https://doi.org/10.1155/2014/194706

Mirjalili S, Lewis A (2016a) Advances in engineering software the whale optimization algorithm. Adv Eng Softw 95:51–67. https://doi.org/10.1016/j.advengsoft.2016.01.008

Mirjalili S, Lewis A (2016b) The whale optimization algorithm. Adv Eng Softw. https://doi.org/10.1016/j.advengsoft.2016.01.008

Pinnau MHR (2007) Second-order approach to optimal semiconductor design 179–199. https://doi.org/10.1007/s10957-007-9203-3

Pratap Y, Haldar S, Gupta RS, Gupta M (2016) Gate-material-engineered junctionless nanowire transistor (JNT) with vacuum gate dielectric for enhanced hot-carrier reliability. IEEE Trans Device Mater Reliab. https://doi.org/10.1109/TDMR.2016.2583262

Raushan MA, Alam N, Siddiqui MJ (2018) Performance enhancement of junctionless tunnel field effect transistor using dual-k spacers. J Nanoelectron Optoelectron 13(6):912–920(9). https://doi.org/10.1166/jno.2018.2334

S.I. Association (2015) International technology roadmap for semiconductors (ITRS). Semiconductor Industry Association. https://www.semiconductors.org/resources/2015-international-technology-roadmap-for-semiconductors-itrs/

Storn R, Price K (1995) Differential evolution—a simple and efficient adaptive scheme for global optimization over continuous spaces

Talukder S (2011) Mathematical modelling and applications of particle swarm optimization

Toh EH, Wang GH, Lo GQ, Chan L, Samudra G, Yeo YC (2007) Performance enhancement of n-channel impact-ionization metal-oxide-semiconductor transistor by strain engineering. Appl Phys Lett. https://doi.org/10.1063/1.2430924

Vanitha P, Balamurugan NB, Priya GL (2015) Triple material surrounding gate (TMSG) nanoscale tunnel FET-analytical modeling and simulation. J Semicond Technol Sci 15(6):585–593

Zhang C, Ning J, Lu S, Ouyang D, Ding T (2009) A novel hybrid differential evolution and particle swarm optimization algorithm for unconstrained optimization. Oper Res Lett. https://doi.org/10.1016/j.orl.2008.12.008

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Choudhury, S., Baishnab, K.L., Bhowmick, B. et al. Design and optimization of asymmetrical TFET using meta-heuristic algorithms. Microsyst Technol 27, 3457–3464 (2021). https://doi.org/10.1007/s00542-020-05140-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-020-05140-w