Abstract

In this work, an optimized structure for an all-optical XOR gate with high contrast ratio and extremely compact dimension is proposed based on a photonic crystal platform. The above structure employs silicon rods in a hexagonal lattice configuration. The design works purely on linear interference effect between the incoming light signals without utilizing any non-linear materials. To study the propagation of light within the structure and to generate the bandgap diagram, the Finite Difference Time Domain technique and Plane Wave Expansion methods are utilized. After optimization of the various design parameters, a contrast ratio of 31.76 dB is attained by the proposed structure along with a response time of 0.46 ps and a footprint of 42.24 μm2. The device can be operated in the C Band with optimum performance at 1550 nm, which is the telecommunication wavelength. The operating bit rate for the proposed structure is 2.17 Tbps. The all-optical XOR gate plays a crucial role as the building blocks of various sequential and combinational logic designs suitable for application in optical computing and telecommunication systems.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Recent advance in technology calls for ultra-high-speed data transmission with low latencies to keep up with the user demands. Optical technology plays a pivotal role in dominating all areas of communication and computing due to its wide bandwidth, high speed, compactness and throughput [1]. Owing to the huge popularity of internet-based communications, the availability of bandwidth and high speed is already overwhelmed and leads to the electronic bottleneck problem. The increasing user demands require advanced technologies with ultra-high speeds and low latencies. The existing technologies cannot keep up with the increasing user demands, hence move towards all-optical communication which can provide high speeds with low latencies [2].

In a complete optical network, the various all-optical devices utilize optical logic gates as the fundamental building blocks [3]. Several combinational and sequential logic circuits for applications, such as switching, multiplexing, parity checking, encoding, filtering and so on, are constructed using logic gates [4, 5]. All these circuits can be implemented using optical logic gates without any electro-optic conversions [6,7,8,9,10]. Several methods have been utilized to implement these gates, such as using non-linear ring resonators [11], Semi-conductor Optical Amplifiers (SOA) [12], non-linear directional couplers [13], Highly Non-Linear Fibers (HNLF) [14], photonic crystals [15], plasmonic slot waveguides [16] and quantum-dot SOA (QD SOA) [17]. However, most of these designs lack chip-level integration capability due to bulky dimensions and flexibility issues [18]. SOA-based designs suffer from gain saturation and make use of high driving current resulting in low-speed operation. Non-linear fibers suffer from bulky design and sensitiveness to environmental factors despite providing better response times. PPLN (Periodically Poled Lithium Niobate)-based devices require accurate temperature control and high input powers for better operation [19]. Currently, photonic crystal platforms are gaining a lot of attention owing to their fascinating features like high integration capability with existing electro-optic as well as optical integrated circuits, flexibility in design, ultra-compact dimensions, wide operating bandwidth, high speed and low power consumption [20,21,22]. Photonic crystals possess a unique feature called bandgap which enable efficient manipulation of light in the required direction over a wide operating bandwidth [23]. Photonic crystal-based logic gates usually operate on the principles of self-collimation, Kerr non-linear effect or linear interference effect. Among these, designs based on non-linear effect require higher operating power and self-collimating effect has limitations in attaining compact dimensions [24]. Interference effect-based all-optical logic gates enable compact and power efficient designs with high compatibility for advanced optical integrated circuits.

The all-optical XOR (AO-XOR) gate or Exclusive OR gate is highly popular as it forms the primary element in the construction of all-optical logic circuits for several applications, such as optical computing, parity checking, all-optical error correction and detection, network coding, pseudorandom number generation, and so on. The AO-XOR gate forms the fundamental component for implementing complex logic circuits for these critical functionalities [25]. Several works on AO-XOR gates based on photonic crystals are already available in the literature.

A design based on a T junction and nano-resonators using two-dimensional (2D) photonic crystals possessed a footprint of 85.22 μm2 along with a contrast ratio (CR) of 43.33 dB [26]. An AO-XOR was proposed using Y-branch waveguide with a CR of 33 dB and footprint of 160.08 μm2 [27]. A simple design for AO-XOR gate in silicon on insulator with and operating wavelength of 1550 nm was proposed [28]. An implementation using silicon dielectric with square lattice with a footprint of 45.36 μm2 attained a CR of 8.29 dB at 1550 nm [29]. A linear structure of footprint 60.2 μm2 for AO-XOR operation was proposed with a CR of 14.7 dB and low response time [30]. A configurable structure working on interference effect with dimensions of 192 μm2 was designed to achieve XOR functionality with an extinction ratio (ER) of 23 dB [31]. It can be observed that photonic crystal-based designs working on interference effect having compact dimensions and high CR can be seen as potential candidates for the future optical integrated circuits (OICs). Achieving high CR without the use of any additional phase control elements leads to a compact and energy efficient design.

In this paper, an optimized AO-XOR gate on a photonic crystal platform using silicon material working on interference principle is implemented. The already proposed structure of reconfigurable AO-XOR/NOT gate [32] is taken so as to optimize the various structural parameters to achieve the maximum CR and compact dimensions with low response times. The Finite Difference Time Domain (FDTD) technique-based simulations are utilized to study the light propagation within the structure whereas the bandgap structure is simulated utilizing Plane Wave Expansion (PWE) method. Section 2 describes the mathematical analysis and principle of operation followed by optimized structure of the AO-XOR gate in Sect. 3. Section 4 covers the simulation results and analysis for the optimized design. Section 5 concludes the work followed by references.

2 Mathematical analysis and principle of operation

Photonic crystals are periodic dielectric structures with low loss that can trap light and manipulate their propagation in the desired path using bandgap engineering. The photonic bandgaps (PBG) which arise due to periodic interactions within the crystal are the frequency bands which cannot propagate in the crystal. By properly inserting suitable defects, such as line, point and surface defects within the perfect crystal, light gets localized inside and various logic functionalities can be realized [33]. The macroscopic Maxwell’s equations govern the distribution of magnetic and electric fields inside the photonic crystal. The solutions of Maxwell’s equations may be treated as the product of a plane wave in periodic function as per the Bloch’s theorem [34].

Here, \(\varphi\) (r) and k denote the periodic function and Bloch’s wave number, respectively. Based on these assumptions, the time-independent relations for the wave equations are,

where, H, E, \(\omega\) and \({\epsilon }_{r}\) represent the magnetic field, electric field, frequency and macroscopic dielectric function, respectively. These equations can be solved to determine the propagation modes within the proposed photonic crystal structure. The solution at one scale can be used to determine the solution at any other scale since the photonic crystals are scale invariant.

The beam interference effect can be utilized to determine the logic state of the gate output. The interference may be destructive or constructive depending on the phase of the arriving signals which can be controlled by changing the path length of waveguides. Constructive interference phenomena arise if the input waves have a phase difference which is an even multiple of π. This generates a higher optical intensity or a logic high output state. Destructive interference arises when the difference in phase becomes an odd multiple of π resulting in cancelation of signals leading to low output power or logic low state [35]. The proposed AO-XOR design consists of waveguides of different path lengths leading to phase difference between the input signals resulting in XOR operation without using any additional phase control mechanisms.

3 Design of modified AO-XOR gate

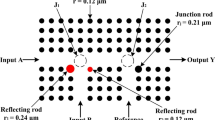

This work aims to boost the performance of the already designed AO-XOR gate [32] by proper optimization of the structural parameters. The lattice type, lattice constant, lattice dimensions and radius of rods are modified such that the CR is enhanced and the footprint of structure is decreased. The new optimized structure for the AO-XOR gate is illustrated in Fig. 1. Table 1 depicts the truth table for XOR gate. There is one output port (Y) and two input ports (A, B). The proposed AO-XOR gate is implemented on a Silicon-on-Insulator (SOI) photonic crystal platform that consists of a hexagonal lattice of Si rods embedded in air. It consists of 17 × 11 silicon rods having refractive index of 3.47. Each rod has a radius (r) of 0.21a and the lattice constant (a) value is chosen as 523 nm. Hexagonal lattice is chosen as it tends to provide larger bandgaps as compared to square lattice.

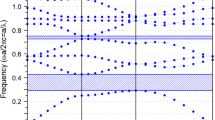

The photonic bandgap diagram for the proposed structure is given in Fig. 2. The design parameters, such as lattice constant (a), radius of dielectric rods (r) and refractive index (n), determine the range of frequencies that fall in the PBG. The desired operating wavelength should fall within the PBG for the working of the all-optical logic gate. There are two large bandgaps existing in TE mode as inferred from the diagram. These correspond to the values 1622.5–1062.9 nm in the first band and from 809.7 to 633.9 nm in the second band. It can be seen that the required operating wavelength of 1550 nm, also called the telecommunication wavelength falls in the first gap.

The two input ports have considerable isolation between them so as to prevent intermixing of signals. Some amount of signal leakage is unavoidable when using such a geometry; however, the leakage should be kept as low as possible to avoid loss of signal power leading to inaccurate results and low CR values. At the same time, providing a larger gap between the adjacent waveguides could reduce signal loss but it tends to increase the device dimensions. Considering these trade-offs, the optimum gap between the adjacent waveguides is chosen as 2a for the proposed design.

The horizontal interaction length for the top input waveguide is 8a and that for the bottom waveguide is 10a. The vertical interaction length toward output waveguide is 4a for the top input waveguide and 8a for the bottom waveguide. As it can be seen, the distance covered by the optical wave to travel toward output port Y from input A is shorter compared to the distance between port Y and port B. Hence, when both the input ports have optical signals, these traverse different path lengths giving rise to a difference in phase that is an odd multiple of π, thus canceling them out. When only one input port has an optical signal, there is no interaction occurring and the same signal arrives at the output. The detailed design parameters are tabulated in Table 2. All these parameters are chosen after proper optimization as given in the next section.

The above structure has several advantages as it is composed only of silicon material. The absence of non-linear materials leads to a less complex design with lower power consumption and the silicon-based structure increases the compatibility with existing CMOS logic system as well as with the hybrid electro-optic and future all-optical integrated circuits. The use of hexagonal lattice provides larger bandgaps and a wider bandwidth of operation. No additional control signals are used to achieve the XOR functionality. The design has ultra-compact dimensions which increase the flexibility and integration capability with other AO devices.

4 Simulation results and analysis

Simulation of the structure is performed by 2D FDTD technique utilizing Synopsys RSoft CAD software to analyze the propagation of light within the device and its various performance characteristics. The open-source software by Optiwave Systems called Opti-FDTD is utilized to generate the bandgap diagram using PWE method. To compute the optical power distribution, the absorbing boundary condition of Perfectly Matched Layers (PML) is applied. To obtain more accurate results to include dispersion effects eventually, the Lorentzian dispersion model was used along with the FDTD analysis using the above software. To check the working of the proposed gate, a Gaussian optical source generating a continuous light signal of wavelength 1550 nm is kept at each of the input ports. To measure the optical intensity arriving at the output, a line monitor is kept at output port Y. The input power PIN at ports A and B is fixed at 1 mW/μm2. The spatial grid has to be small to generate a complete simulation. This is indicated by the wavelength of the material used. For stable operation, the space time grids should follow the given condition [36],

where, \(\Delta\)t denotes the step time, c denotes the free space velocity of light, and ∆x, ∆z represents the space steps along x- and z- axis, respectively.

Table 3 shows the digital as well as optical truth table for the optimized AO-XOR gate. Here, the measured output power is expressed as a fraction of the input power PIN. To distinguish between logic 1 and logic 0 levels, the optical intensity levels of each state must be specified. In this work, power level below 0.005 PIN denotes logic 0 state and power level above 0.1 PIN denotes logic 1 state. The various performance metrics are computed to characterize the performance of the optimized design. The contrast ratio is a mathematical expression consisting of the output power levels for the two logic states [37]. i.e.,

where, Ph and Pl denote the lowest value of optical intensity in logic high state and the highest value of optical intensity in logic low state, respectively. The higher the value of CR, the easier it is to distinguish between the logic states and hence better the operation.

Another parameter that significantly affects the performance of the AO logic gate in an integrated circuit is return loss. It is calculated as the difference between the forward and reflected powers in dB. It is a measurement of the amount of light injected from the source compared to the amount of light reflected back toward the source and a high return loss value is preferred for better operation [38].

Using the above equation, Return Loss (dB) is calculated wherein PIN denotes the input power and PREF denotes the amount of light reflected back to the input port (s). Another parameter that determines the speed of the device is the bit rate [39]. The approximate operating bit rate of the device is given by the inverted value of response time. In addition, the dimensions of the device or the footprint are also of prime importance due to the need to integrate a large number of such devices onto a single chip. Lower response times and smaller dimensions are preferred for high-speed operation and easy integration with OICs.

The proposed structure has four different operating states owing to two different inputs. Depending on the interactions between the incoming light signals, the output port produces either a high-intensity signal or a low-intensity signal. In the first case, the two input ports have zero intensity or logic 0 state, i.e., A = B = 0. Then, no light propagates through the structure giving rise to zero intensity output or logic 0 state at port Y. For the second case, the first input port has zero intensity and the second port has an input light signal of PIN power i.e., A = 0, B = 1. Then, only one optical wave enters the structure and it propagates along the input waveguide toward the output Y giving rise to a logic 1 output. This is depicted in Fig. 3.

For the third case, the first input port has a light signal, while the second port has zero intensity, i.e., A = 1, B = 0. Then, only one signal travels through the structure without any interactions giving rise to logic high result. This is illustrated in Fig. 4. For the fourth case, two high-intensity waves propagate along the structure, i.e., A = B = 1. In this case, the two signals travel different path lengths and undergo a change in phase giving rise to a destructive interference effect. The signals get canceled out and very low intensity corresponding to logic 0 state reaches Y. This is depicted in Fig. 5.

For varying values of wavelengths from 1530 to 1565 nm, the normalized output powers for the four different input states are studied. This is tabulated in Table 4. For A, B = 10 and 01 cases, the output port Y has high-intensity light corresponding to logic 1 output. For A, B = 00 and 11, very low intensity or no light appears at port Y resulting in logic 0 state. Overall, the best performance is attained for 1550 nm wavelength as seen from Fig. 6 and 7. For all other values of wavelength, a lower value of CR was obtained with the least values attained for 1530 nm and 1540 nm. The plot of CR versus input wavelength is depicted in Fig. 8. A high CR value of 31.76 dB is attained by the device at 1550 nm.

The various structural parameters were chosen carefully after optimizing the design for achieving maximum CR with low response times. These metrics are directly affected by changes in radius of rods, operating wavelength, lattice constant and the material refractive index. The silicon rod radius is varied from 0.18a to 0.22a as shown in Table 5. The variation of response time and bit rate with Si rod radius is plotted in Fig. 9 and that of CR with Si rod radius in Fig. 10. The maximum CR value and the least response time is achieved for the radius value of 0.21a. Table 6 depicts the variation in lattice constant from 520 to 524 nm. The plot of response time and bit rate versus lattice constant is illustrated by Fig. 11. The highest bit rate of 2.17 Tbps and maximum CR is attained for lattice constant of 523 nm as seen from Fig. 12.

From a fabrication point of view, we have considered a ± 5 nm variation of lattice constant for further analysis. These results are shown in Table 7. Again, it can be observed that the maximum value of CR (31.76 dB) and highest bit rate (2.17 Tbps) was attained for the lattice constant value of 523 nm. With varying values of lattice constant (± 5 nm), the CR and bit rate remained above 21 dB 1.3 Tbps, respectively. Even with such large variations, the proposed structure showed reasonably good performance especially in terms of the CR which is of utmost significance with regards to logic gates.

Table 8 shows the calculated values of return loss at each of the input ports A and B for the various logic states of the proposed AO-XOR gate. It can be inferred that a significant amount of back reflection occurs which has to be taken into consideration in future works to lower the loss of power especially when coupling with other devices in an OIC. However, in spite of this backscattering, a high CR is achieved owing to larger gap in power levels for logic 1 and logic 0 states. This is highly significant in distinguishing between the two logic states especially when working with low power levels.

From the above plots, operational characteristics of the newly designed AO-XOR structure is optimized to attain the maximum CR, the highest bit rate and the least response time. Thus, the final structure has the optimized design parameters of lattice constant 523 nm, radius 0.21 × a and input wavelength 1550 nm.

The newly proposed design for AO-XOR gate has improved the already existing design and optimized the various structural parameters to attain a high CR of 31.76 dB without using any non-linear material or additional phase control elements along with a footprint of extremely low dimensions. The device is realized on wafer dimensions of 42.2 μm2. A response time of 0.46 ps and a bit rate of 2.17 Tbps is attained by the structure. The entire device is composed of only silicon material which enables easy integration with hybrid electro-optic as well as with the upcoming OICs. Table 9 shows a comparison of the performance of the improved AO-XOR gate with existing works from the literature. It can be observed that achieving a CR above 30 dB for a structure based only on linear interference effect with extremely low dimensions and low response time (< 1 ps) can be considered as a huge step toward the practical realization of a complete optical network based on integrated all-optical devices.

5 Conclusion

In this work, an optimized design of AO-XOR gate based on beam interference effect in 2D photonic crystals is proposed. The design is achieved after proper optimization of the structure parameters to attain a maximum contrast ratio of 31.76 dB. The structure possesses very low dimensions of 42.2 μm2 with an operating speed of 2.17 Tbps. The light wave propagation within the structure is studied with the help of 2D FDTD technique. This work proves to be a potential candidate to build various combinational and sequential all-optical logic circuits for applications in the areas of optical computing and telecommunications.

Availability of data and material

Not applicable.

Code availability

Not applicable.

References

K. Goswami, H. Mondal, M. Sen, A review on all-optical logic adder: heading towards next-generation processor. Opt. Commun. 483, 126668 (2021)

P. Singh et al., All-optical logic gates: designs, classification, and comparison. Adv. Opt. Technol. 1–13, 2014 (2014)

A. Mohebzadeh-Bahabady, S. Olyaee, Investigation of response time of small footprint photonic crystal AND logic gate. Optoelectron. Lett. 16(6), 477–480 (2020)

J. Crowe, Introduction to digital electronics (Elsevier, Barrie Hayes-Gill, 1998)

Z. Qiang, W. Zhou, R.A. Soref, Optical add-drop filters based on photonic crystal ring resonators. Opt. Express 15, 1823–1831 (2007)

N. Nair, S. Kaur, H. Singh, All-optical ripple carry adder based on SOA-MZI configuration at 100 Gbps. Optik 231, 166325 (2021)

M. Michael, B.E. Caroline, S.C. Xavier, M-ary DPSK coded binary to gray, BCD to gray, and octal to binary all-optical code converters based on SOA-MZI configuration at 500 Gb/s. Appl. Opt. 59(27), 8126–8135 (2020)

S. Naghizade, S. Mohammadi, H. Khoshsima, Design and simulation of an all optical 8 to 3 binary encoder based on optimized photonic crystal OR gates. J. Opt. Commun. 42(1), 31–41 (2021)

Q. Liu, Z. Ouyang, C.J. Wu, C.P. Liu, J.C. Wang, All-optical half adder based on cross structures in two-dimensional photonic crystals. Opt. Express. 16(23), 18992–19000 (2008)

D.E. Fouskidis, K.E. Zoiros, A. Hatziefremidis, Reconfigurable all-optical logic gates (AND, NOR, NOT, OR) with quantum-dot semiconductor optical amplifier and optical filter. IEEE J. Sel. Top. Quantum Electron. 27(2), 1–15 (2021)

M. Moradi, M. Danaie, A.A. Orouji, Design of all- optical XOR and XNOR logic gates based on Fano resonance in plasmonic ring resonators. Opt. Quant. Electron. (2019). https://doi.org/10.1007/s11082-019-1874-0

A. Kotb, C. Guo, 100 Gb/s all-optical multifunctional AND, NOR, XOR, OR, XNOR, and NAND logic gates in a single compact scheme based on semiconductor optical amplifiers. Opt. Laser Technol. 137, 106828 (2021)

W.B. Fraga, J.W.M. Menezes, M.G. da Silva, C.S. Sobrinho, A.S.B. Sombra, All optical logic gates based on an asymmetric nonlinear directional coupler. Opt. Commun. 262(1), 32–37 (2006)

V. Sharma, S. Singh, The design of a reconfigurable all-optical logic device based on cross-phase modulation in a highly nonlinear fiber. J. Comput. Electron. 20, 397–408 (2021)

Fu. Yulan, Hu. Xiaoyong, Q. Gong, Silicon photonic crystal all-optical logic gates. Phys. Lett. A. 377(3–4), 329–333 (2013)

Y. Fu et al., All-optical logic gates based on nanoscale plasmonic slot waveguides. Nano Lett. 12(11), 5784–5790 (2012)

K. Mukherjee, Design and analysis of all optical frequency encoded XOR and XNOR gate using quantum dot semiconductor optical amplifier-Mach Zehnder interferometer. Opt. Laser Technol. 140, 107043 (2021)

K.E. Muthu, S. Selvendran, V. Keerthana et al., Design and analysis of a reconfigurable XOR/OR logic gate using 2D photonic crystals with low latency. Opt. Quant. Electron. (2020). https://doi.org/10.1007/s11082-020-02550-y

P. Andalib, N. Granpayeh, All-optical ultra-compact photonic crystal AND gate based on nonlinear ring resonators. J. Opt. Soc. Am. B. 26, 10–16 (2009)

A. Kumar, S. Medhekar, All optical NOT and NOR gates using interference in the structures based on 2D linear photonic crystal ring resonator. Optik 179, 237–243 (2019)

G. Calò, V. Petruzzelli, Compact design of photonic crystal ring resonator 2×2 routers as building blocks for photonic networks on chip. J. Opt. Soc. Am. B. 31, 517–525 (2014)

S. Fan, P.R. Villeneuve, J.D. Joannopoulos, H.A. Haus, Channel drop filters in photonic crystals. Opt. Express 3, 4–11 (1998)

H.M. Hussein, T.A. Ali, N.H. Rafat, A review on the techniques for building all-optical photonic crystal logic gates. Opt. Laser Technol. 106, 385–397 (2018)

A. Salmanpour, S. Mohammadnejad, A. Bahrami, Photonic crystal logic gates: an overview. Opt. Quant. Electron. 47, 2249–2275 (2015)

M. Zhang, L. Wang, P. Ye, All optical XOR logic gates: technologies and experiment demonstrations. IEEE Commun. Mag. 43(5), S19–S24 (2005)

S. Olyaee et al., Realization of all-optical NOT and XOR logic gates based on interference effect with high contrast ratio and ultra-compacted size. Opt Quant Electron. 50(385), 1–12 (2018)

H. Wang, Y. Xiaoyan, X. Rong, and Xianwei Rong All-optical AND, XOR, and NOT logic gates based on Y-branch photonic crystal waveguide. Opt Eng (2015). https://doi.org/10.1117/1.OE.54.7.077101

H. Vahed, F.C. Ghadimi, Simple design of all-optical AND, OR, NOT, and XOR logic gates in silicon-on-insulator photonic crystal. Opt. Eng. (2020). https://doi.org/10.1117/1.OE.59.2.027108

D.G.S. Rao, S. Swarnakar, V. Palacharla et al., Design of all-optical AND, OR, and XOR logic gates using photonic crystals for switching applications. Photon. Netw. Commun. 41, 109–118 (2021)

S.E. Kordi, R. Yousefi, S.S. Ghoreishi, H. Adrang, All-optical OR, NOT and XOR gates based on linear photonic crystal with high port-to-port isolation. Appl. Phys. B. 126(169), 1–12 (2020)

A. Safinezhad, H.B. Ghoushji, M. Shiri, M.H. Rezaei, High performance and ultrafast configurable all-optical photonic crystal logic gates based on interference effects. Opt. Quant. Electron. 53(259), 1–20 (2021)

E. G. Anagha, R. K. Jeyachitra, A new configuration for the realization of reconfigurable and power efficient all-optical XOR and NOT gate, 2020. In: 7th international conference on signal processing and integrated networks (SPIN), 10–15 (2020)

E.H. Shaik, N. Rangaswamy, Interference based all-optical photonic crystal logic gates, advances in photonic crystals and devices, 1st edn. (CRC Press, Boca Raton, 2019)

I.A. Sukhoivanov, I.V. Guryev, Photonic crystals: physics and practical modeling (Springer, Berlin, 2009)

N.M. Dsouza, V. Mathew, Interference based square lattice photonic crystal logic gates working with different wavelengths. Opt. Laser Technol. 80, 214–219 (2016)

S. Damodaran, T. Shankar, R. Anbazhagan, All optical clocked D flip flop for 1.72 Tb/s optical computing. Microelectron. J. 103, 104865 (2020)

Y. Ishizaka, Y. Kawaguchi, K. Saitoh, M. Koshiba, Design of ultra compact all-optical XOR and AND logic gates with low power consumption. Opt. Commun. 284(14), 3528 (2011)

P. Sharma, V.D. Kumar, All optical logic gates using hybrid metal insulator metal plasmonic waveguide. IEEE Photon. Technol. Lett. 30(10), 959–962 (2018)

A. Mohebzadeh-Bahabady, S. Olyaee, All-optical NOT and XOR logic gates using photonic crystal nano resonator and based on an interference effect. IET Optoelectron. 12(4), 191–195 (2018)

P. Rani, Y. Kalra, R.K. Sinha, Design of all optical logic gates in photonic crystal waveguides. Optik 126(9), 950–955 (2015)

Funding

Not applicable.

Author information

Authors and Affiliations

Contributions

All authors equally contributed for the preparation of the manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Ethics declarations

This article does not contain any studies involving animals or human participants performed by any of the authors.

Consent to participate

Not applicable.

Consent for publication

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Anagha, E.G., Jeyachitra, R.K. Optimized design of an all-optical XOR gate with high contrast ratio and ultra-compact dimensions. Appl. Phys. B 128, 21 (2022). https://doi.org/10.1007/s00340-021-07747-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00340-021-07747-x