Abstract

The generation and accumulation of trap charges at oxide-semiconductor contact is a crucial point to consider since it affects device performance and reliability. This paper aimed to provide a comprehensive assessment of interface trap charges on the characteristics of a ultra-thin source region-based F-shaped Tunnel FET (UTS-F-TFET) with theoretical and numerical calculation of important frequency and linearity parameters. Comparative research is carried out to opt for the best lower bandgap material for source region to optimize the analog functionality of UTS-F-TFET. With a steeper subthreshold slope, the UTS-F-TFET has increased current carrying capabilities and reduced ambipolar behavior. This research aims to investigate the impact of ITCs on DC characteristics (Thermal equilibrium state, ON and OFF state) and analog/RF performance of the simulated device. Moreover, the consequence of ITCs on linearity figure of merits with reliability consideration is also investigated. As per this investigation, the proposed TFET structure exhibited minimal distortion in linearity metrics with negligible influence of ITCs. As a result, the proposed UTS-F-TFET is compatible with ultra-low power high-frequency operations with minimum distortion.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Device performance, power consumption, and reliability are crucial challenging concerns to resolve, according to the current rapid growth of the semiconductor industry. Moore’s law is pursued to reduce power consumption and enhance device performance, resulting in reducing semiconductor device size. Billions of transistors are now integrated on single chip/microprocessors for compact size with improved device performance. But, Several fabrication challenges arise as semiconductor devices are downsized to accomplish a miniaturized criterion of ICs with the same functionality [1]. As a result, MOSFETs have been down-scaled to improve device functionality in power consumption, switching speed, and package density per unit area with lower fabrication costs. Some adverse effects have been observed due to MOSFET downscaling due to an undesirable increase in leakage current. At room temperature, increased leakage current causes significant consequences like short circuit effect (SCEs), mobility degradation, impact ionization, Drain induced barrier lowing (DIBL), Hot carrier effects (HCEs), and static power consumption. Furthermore, because of the direct dependence on the thermal constant (kT/q), MOSFETs limit the subthreshold slope (SS) to 60 mV/decades [2, 3].

The tunnel field-effect transistor (TFET) shows very promising behavior to overcomes the aforementioned limitation of MOSFET. It offers steeper SS (high switching speed) compared to MOSFET, and it performs better in low-power applications with a lower threshold voltage (\(V_\mathrm{th}\)) [4, 5]. TFET works on phenomena of quantum tunneling of charge carrier from source to channel, which helps to achieve steeper switching characteristics and reduced \(V_\mathrm{th}\) [6]. Apart from these advantages, it also suffers from several limitations such as low current driving capability and ambipolar current behavior that degrades the device analog/RF performance [7, 8]. To overcome these limitations of conventional TFET, various techniques are introduced, such as gate and drain engineering, dielectric material variation, doping type and variation, material (hetero materials) engineering with structural modification, and many more.

To figure out the limitations of conventional TFET, a new structure with ultra-thin source region and reduced drain channel interface-based TFET (UTS-F-TFET) is proposed and investigated in previous work [9, 10]. Because of complete insertion of ultra-thin source region into the channel region, low \(V_\mathrm{th}\) and high ON-state current (\(I_\mathrm{on}\)) are achieved with steeper SS. Furthermore, to reducing \(V_\mathrm{th}\) and increase current driving capability, some lower bandgap materials are used in source region of UTS-F-TFET [11]. This will justify with the help of simulation on SILVACO TCAD tool with incorporating important models and numerical methods.

ITCs accumulate at the semiconductor/oxide interface throughout the manufacturing process due to the oxidation process, stress occurs due to high temperature/hot carrier, and damage sustained during the fabrication steps. The traps are usually divided into donor trap charges (DTCs) and acceptor trap charges (ATCs). DTCs reside above the valance band and behave like positive ITCs (P-ITCs) by donating an electron. Another side, ATCs reside below the conduction band and acts like negative ITCs (N-ITCs) by accepting an electron to fill the empty state within the Si–SiO\(_2\) interface region [12, 13]. These ITCs accumulate in TFETs due to a large electric field at the tunneling junction, which excites the silicon body surface, causing the electric field variation at the source/channel junction (SC-junction). As we know, the tunneling probability and drain current is proportional to the electric field at the tunneling junction of device, resulting in the deviation in current-carrying potentiality of device [14]. As a result, determining the impact of trap charges on device performance characteristics is crucial. This considerable impact of ITCs on device performance was investigated with the help of analyzing the analogue and linearity parameters with respective mathematical equations.

2 Device schematic and parameters

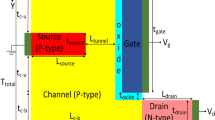

The 2D schematic of the proposed UTS-F-TFET device is illustrated in Fig. 1. The proposed device consists of a single gate with an ultra thin, highly doped source region that is entirely bounded by the intrinsic channel region. On the other hand, drain region of device is attached to the outside of the channel. Because of this, DCi is reduced and device looks like an L-shaped. The optimized physical parameters of UTS-F-TFET such as Gate oxide thickness (\(t_\mathrm{ox}\)), Thickness above and below source (\(t_\mathrm{cu}\)), Channel thickness at bottom of device (\(t_\mathrm{cb} = t_\mathrm{d}+t_\mathrm{ox}\)), Lateral tunneling length (\(L_\mathrm{t}\)), Source thickness (\(t_\mathrm{s}\)), Channel thickness (\(2t_\mathrm{cu}+t_\mathrm{cb}+t_\mathrm{s}\)), Drain thickness (\(t_\mathrm{d}\)) are 1, 16, 6, 4, 3, 35 and 5 nm, respectively. For simulated UTS-F-TFET, Drain doping concentration (\(N_\mathrm{D}\)), Channel doping concentration (\(N_\mathrm{C}\)), source doping concentration (\(N_\mathrm{S}\)), and gate work function (\(\mathrm{WF}_\mathrm{G}\)) are \(5 \times {10}^{18}\) cm\(^{-3}\), \(1 \times {10}^{15}\) cm\(^{-3}\), \(2 \times {10}^{20}\), and 4.5 eV, respectively.

To ensure the model accuracy used during simulation, Experimental data of doped L-shaped tunnel FET (L-TFET) (Ref. [15]) have been used to calibrate the proposed device. With the same physical dimensions and materials of doped L-TFET, calibration is carried out. The simulation results authenticate with experimental data as depicted in Fig. 2a. In this work, the proposed structure is modeled using the same analytical/physical models used in Ref. [15].

For simulation purposes, the following models are incorporated: - Non-local Band to Band Tunneling Model (BTBT), Band Gap Narrowing Model (BGN), FERMI, Auger Recombination Model (Auger), Mobility Models (FLDMOB, CONMOB and SRH), Trap-Assisted Tunneling Model (TAT) etc. Along with these models, Newton’s numerical method was used to provide strong coupling between the resultant equations for better convergence of current [16]. A brief description of used models are mentioned in Table 1.

3 Optimization of source material

The optimal solution of the reduced \(I_\mathrm{on}\) problem in the proposed TFET is to employ a lower bandgap material for the source region. Because of this, tunneling barrier width at SCi getting reduced and helps to increased the tunneling probability, which reflect in terms of increased \(I_\mathrm{on}\). At T = 300 K, some widely used lower bandgap materials are InAs (\(E_\mathrm{g}\) = 0.35 eV), InGaAs (\(E_\mathrm{g}\) = 0.57 eV) and Si–Ge (\(E_\mathrm{g}\) = 0.68 eV) are used as source material in place of silicon (\(E_\mathrm{g}\) = 1.11 eV) with SiO\(_2\) as effective gate oxide. From all the above materials, Si–Ge has the higher effective density of states at the band edges (\(1.92\times 10^{19} \mathrm{cm}^{-3}\)). Because of this, higher no. of electron tunnel from source to channel and recombine at SCi. So, the UTS-F-TFET with Si-Ge as source material has increased \(I_\mathrm{on}\) when compared to the other materials used in source, as depicted in Fig. 2b.

Thermal equilibrium a calibration curve for Ref. [15] and b \(I_\mathrm{ds}-V_\mathrm{gs}\) data plot for different materials

4 DC performance analysis

4.1 Thermal equilibrium state

This section enlightens the effect of ITCs on the functioning of UTS-F-TFET under the thermal equilibrium condition (\(V_\mathrm{ds}\) = 0 V and \(V_\mathrm{gs}\) = 0 V). For this, we analyzed the charge carrier concentration (\(C_\mathrm{conc}\)) on both the interfaces (SCi and DCi) which are shown in Figs. 3 and 4, respectively. Figure 3a reveals that Negative ITC (N-ITC) helps to increase the the electron \(C_\mathrm{conc}\) and opposite effect can be seen for the hole \(C_\mathrm{conc}\) (in Fig. 3b) near the SCi. Another side, electron \(C_\mathrm{conc}\) increases and hole \(C_\mathrm{conc}\) decreases with Positive ITC (P-ITC) at DCi (Fig. 4a and b).

4.2 ON-state condition

The carrier concentration of UTS-F-TFET is shown in Figs. 5 and 6, along X-position for both interfaces. In TFET, mainly SCi and DCi junction affect the device characteristics. Hence, the ITCs impact on both interface w.r.t carrier concentrations of electron and holes has been investigated. From Fig. 5a, we can analyse that the electron concentration profile near the Si-\(SiO_2\) interface falls (rise) for N-ITCs (P-ITCs) concerning the without ITC impact. The opposite impact can be seen for the hole concentration profile at Si–\(SiO_2\) interface in Fig. 5b. Another side, the impact of ITCs is just opposite for the DCi junction because donor trap (P-ITCs) occupied the empty state and helps to increase the donor concentration profile (Electron conc.) in the drain region (Fig. 6a). Same way, P-ITCs helps to decrease the hole carrier concentration in drain region (Fig. 6b). The reduction in hole concentration is beneficial to reduce the ambipolar conduction because \(I_\mathrm{ambi}\) is mainly contributed by the holes present in the region that recombine with an electron at DCi. From Fig. 7a and b, \(V_\mathrm{th}\) (0.3 V) and \(I_\mathrm{on}\) (\(9.12 \times 10^{-4} A/\mu \mathrm{m}\) )is improved with P-ITCs when compared to without ITCs effect.

4.3 OFF-current analysis

This part discusses the impact of ITCs and Temperature (T) at both interfaces (SCi and DCi). The OFF-state condition mainly governs by the DCi junction because the OFF-current (\(I_\mathrm{off}\)) is affected by the recombination at DCi. T and ITCs have a significant impact on reliability-related issues of UTS-F-TFET for circuit-level applications because both of them considerably affect the \(I_\mathrm{on}/I_\mathrm{off}\) ratio [17, 18]. The higher value of \(I_\mathrm{on}/I_\mathrm{off}\) ratio leads to high switching speed. So. an extensive investigation is carried out on UTS-F-TFET for OFF-state conditions. For this, the impact of ITCS, along with models and T variation, was carefully investigated to extract the optimum type of ITCs with T range and models. To examine the effect of ITCs and T on \(I_\mathrm{off}\), we used BTBT, SRH and TAT throughout the simulation process.

The consequence of BTBT model on \(I_\mathrm{off}\), were examined with the help of Eq. 1. From Eq. 1, it is seen that the BTBT mainly depends on electric field (\(E = E_\mathrm{g}^*+ \Delta \varphi\)), body thickness (\(t_\mathrm{si}\)), dielectric constant of material and oxide (\(\epsilon _\mathrm{si}\) and \(\epsilon _\mathrm{ox}\)) and band gap of material (\(E_\mathrm{g}^*\)). The BTBT models controlling the \(I_\mathrm{on}\) under the high E-field and show less sensitivity towards the T variations.

By using Eq. 2, we investigate the impact of the SRH model on proposed devices for T variation (250–400 K). Constant carrier lifetimes [TAUP0 (for hole) and TAUN0 (for electron)] are used in SRH recombination model with dependency on temperature (\(T_{\text {L}}\) term in Eq. 2) and trap energy level (\(E_\mathrm{TRAP}\)), which indicates that T variation significantly affects the OFF-state conduction with the SRH model. Similarly, from Eq. 3, TAT model also shows considerable impact on \(I_\mathrm{off}\) because it depends on field-dependent functions (\(\Gamma _\mathrm{n}^{{\text {DIRAC}}}\) and \(\Gamma _\mathrm{p}^{{\text {DIRAC}}}\)) and all that factor which influence SRH model [19,20,21].

In this proposed device, we get the electric field crowding effect near the corner of source–channel interface, which helps to increase the tunneling rate at SCi. Because of this, higher \(I_\mathrm{ds}\) can be obtained, as mentioned earlier in this work. So, the impact of ITCs on E-field must be investigated. The E-field deviation in the direction of channel region is illustrated in Fig. 8 for different ITCS. The E-field at both junctions (SCi and DCi) can be affected by the ITCs [22]. At SCi junction, higher E-field is achieved in comparison to DCi junction, because of this \(I_\mathrm{ambi}\) is very low in proposed device. From Fig. 8a, the highest E-field at SCi is allocated for the P-ITCs because P-ITCs helps to improve the band bending near the SCi. Similarly, the minimum E-field at DCi is achieved for N-ITCs because of the reduced band bending at DCi with an application of N-ITCs, as depicted in Fig. 8b.

The potential follows the same trend as the E-field, implying that P-ITCs lead to a rise in potential and N-ITCs lead to a drop in potential, as showing in Fig. 9a and b for the SCi and DCi junctions, respectively. For SCi, the deviation in potential is almost negligible for various ITCs compared with potential at DCi junction.

The total charge carrier density is constant at thermal equilibrium conditions because the recombination and generation rate rates are equivalent. But, when the external voltage is applied along with ITCs consideration, the generation of charge carrier increases because of this mobility saturation occurs [23]. Due to this, the recombination rate at both interfaces decrease for P-ITCs, as portrayed in Fig. 10. At DCi, deviation in recombination rate for N-ITCs is significantly very high as compared to Without ITCs (Fig. 10b) because N-ITCs generate more hole carriers at DCi, which recombine with the majority charge carrier (electron) present in drain region.

The significant deviations in E-field, potential and recombination rate at DCi affects the OFF-state behaviour of proposed device for various ITCs, models and temperature (250–400 K). For lower \(V_\mathrm{gs}\), TAT and SRH models become more prominent when \(V_\mathrm{gs}\) decreases. When \(V_\mathrm{gs}\) is very low, the potential barrier at DCi junction is getting reduced and enables the BTBT phenomenon. So, the charge carriers start tunneling across the present potential barrier. The current component of BTBT, BTBT + SRH and BTBT + SRH + TAT have their region of subjection depending upon the E-field at SCi and DCi junctions [24]. From Eq. 1, under high E-field, the BTBT model dominates the \(I_\mathrm{ds}\) value and is less sensitive to T variation and different types of ITCs, as shown in Fig. 11. SRH and TAT models have seemed at lower E-field and try to increase the \(I_\mathrm{ds}\) value with showing strong sensitivity to changes in ITCs and T. From Fig. 11a, the variation in \(I_\mathrm{ambi}\) from \(10^{-19}\) to \(10^{-14}\) \(A/\mu \mathrm{m}\) (\(10^5\) time) for T variation under without ITCs consideration and with application of BTBT model. However, \(I_\mathrm{ambi}\) = \(10^{-18}\) and \(10^{-15}\) for the SRH and TAT models, it rises when T increases. A similar effect for N-ITCs and P-ITCs can be seen for the \(I_\mathrm{ambi}\) when T varies from 250 to 400 K with different models (BTBT, SRH and TAT), illustrated in Fig. 11b and c, respectively. Consequently, at lower T, the SRH and TAT implications are relatively low, and the BTBT resurfaces as a significant and effective tunneling mechanism with reduced sensitivity to T variation and ITCs.

5 Impact on analog/RF parameter

In the circuit level assessment of the device, the radio frequency (RF) statistics are quite important. The parasitic capacitances (\(C_\mathrm{gd}\) and \(C_\mathrm{gs}\)) are investigated in this regard and depicted by Fig. 12a and b of UTS-F-TFET for different ITCs w.r.t \(V_\mathrm{gs}\). From Fig. 12a, it is seen \(C_\mathrm{gd}\) increases with increasing \(V_\mathrm{gs}\) because increment in \(V_\mathrm{gs}\) leads to the reduction in potential barrier between channel and drain [25, 26].The significant increase in \(C_\mathrm{gd}\) with P-ITCs is due to the same phenomena, i.e., P-ITCs minimize the potential barrier between channel and drain as compared to without ITCs consideration. N-ITCs have the opposite phenomenon, resulting in a decrease in \(C_\mathrm{gd}\). From Fig. 12b, it is seen that the deviation in \(C_\mathrm{gs}\) is less for ITCs. The \(C_\mathrm{gs}\) is decreased with increasing \(V_\mathrm{gs}\) because the potential barrier between gate and source decreases for high \(V_\mathrm{gs}\) and the coupling between gate and channel is improved. \(C_\mathrm{gs}\) is decreased (Increases) with P-ITCs (N-ITCs) as shown in Fig. 12b.

Transconductance (\(g_\mathrm{m}\)) is crucial in analogue applications because it affects the intrinsic gain of device and relates the input voltage across the device and output current [27], given as

When designing analog circuits, \(g_\mathrm{m}\) is quite important. Figure 13a depicts the variation in \(g_\mathrm{m}\) with \(V_\mathrm{gs}\) for the different ITCs. The P-ITCs have a rising impact on \(g_\mathrm{m}\) because of improving tunneling rate at SCi, and N-ITCs have a decreasing impact due to the reduced tunneling rate. The N-ITCs and P-ITCs lead to a decrease and increase in \(g_\mathrm{m}\) by 23.46% and 33.76%, respectively.

The cut-off frequency (\(f_\mathrm{t}\)) is another crucial design factor for the high-speed RF devices, at which input current becomes equal to short circuit output current [25]. The mathematical expression of \(f_\mathrm{t}\) given by Eq. 5 and the impact of different ITCs on \(f_\mathrm{t}\) for UTS-F-TFET is shown in Fig. 13b.

For higher \(V_\mathrm{gs}\), \(f_\mathrm{t}\) mainly depends on \(g_\mathrm{m}\) and \(C_\mathrm{gd}\) because both are dominating factors as compared to the \(C_\mathrm{gs}\) (very less value). P-ITCs cause an increase in \(g_\mathrm{m}\), as previously stated, and consequently an increase in \(f_\mathrm{t}\) when compared to without ITCs. On the other hand, N-ITCs exhibit the opposite phenomenon, i.e., \(f_\mathrm{t}\) decreases with N-ITCs. For the proposed device, the N-ITCs and P-ITCs decrease and increase the \(f_\mathrm{t}\) by 3.23% and 1.97%, respectively. Thus, proving that the F-shaped ultra-thin source design is much more immune to the effect of ITCs.

To analyze the device response time and delay, another critical parameter, transit time (TT), comes into the picture, and its mathematical expression is given by Eq. 6. \(f_\mathrm{t}\) and TT are inversely proportional to each other, i.e., for higher \(f_\mathrm{t}\), we get a lower value of TT. The speed of UTS-F-TFET increases with P-ITCs because the \(f_\mathrm{t}\) value significantly increases with the effect of P-ITCs, as shown in Fig. 14a. For N-ITCs, TT is increased as \(f_\mathrm{t}\) increases, which is not desirable for high speed and low response time.

Figure 14b shows the consequence of different types of ITCs on the Gain bandwidth product (GBP), which is defined as the product of bandwidth of device and the gain at which the bandwidth is measured [25, 28]. It is given by Eq. 7as follows:

From Eq. 7, we can say that GBP is directly proportional to \(g_\mathrm{m}/ C_\mathrm{gd}\). The \(g_\mathrm{m}\) and \(C_\mathrm{gd}\) both increase with P-ITCs, but \(g_\mathrm{m}\) is very high so GBP improves with P-ITCs and deteriorate with N-ITCs. The percentage deviation of variation in GBP for P-ITC and N-ITCs is 2.56% (Increase) and 2.31% (Decrease), respectively.

Equations 8 and 9 represent the mathematical formulation of Transconductance frequency product (TFP) and Transconductance generation factor (TGF), which are the key parameters to determine the device efficiency and off-set between power dissipation and operating bandwidth [29]. The impact of different ITCs on TFP and TGF is illustrated in Fig. 15a and b, respectively. Figure 15b demonstrates that TFP rises linearly before the starting of the inversion phase, then attains its maximum value and subsequently decreases for increasing gate bias levels, which is due to mobility degradation. Along with this, an application of P-ITCs leads to a reduction of the maximum peak of TFP compared to N-ITCs (maximum value for TFP). Similarly, the impact of different ITCs on TGF is delineated in Fig. 15a. From Eq. 9, TGF is directly proportional to TFP. Hence the maximum peak of TGF is achieved for N-ITCs, and a lower peak is attained for P-ITCs because of mobility reduction of charge carriers.

6 Effect of ITCs on linearity performance

An enhanced \(I_\mathrm{on}\), high \(I_\mathrm{on}/I_\mathrm{off}\) ratio, low \(V_\mathrm{th}\), and lower value of SS with suppressed ambipolar conduction are not only critical characteristics to assess device behavior in the recent trend of device and circuit applications. In addition, for RF devices to be capable of interacting with today’s modern communication systems, they must have a low signal-to-noise ratio as well as a fast speed. The device should also have linear properties so that the intended output signal is not severely impacted by nonlinear distortion. The device’s linearity analysis is a different statistical process control phase in which the device is integrated in a circuit, and the linear relationship between input and output is examined [30, 31]. The Volterra series can be used to write any nonlinear power series in the following format:

\(g_\mathrm{m}\) must not significantly alter owing to a change in input voltage \(V_\mathrm{gs}\) to validate linearity functionalities. However, the \(g_\mathrm{m}\) of both MOSFETs and TFETs changes with the input voltage \(V_\mathrm{gs}\), resulting in nonlinear behavior for both devices. The various frequency components of the desired inter modulated (IMS) and harmonics signal are mentioned in Table 2. The harmonic distortion is given by the integral multiples of fundamental frequencies (\(f_1\) and \(f_2\)), which can be eliminated because they are very far from the permissible range [32]. Eqution 11 could be used to define the small-signal model (SSM) of output current (\(I_\mathrm{ds}\)) in terms of non-linear \(g_\mathrm{m}\) for \(V_\mathrm{gs}\).

As well as \(V_\mathrm{gs}\) increase, \(I_\mathrm{ds}\) increase with it, but after sometime \(I_\mathrm{ds}\) become saturated because of mobility saturation of charge carrier. Thus, \(g_\mathrm{m}\) starts decreasing after attaining the peak for higher \(V_\mathrm{gs}\). Therefore, a detailed investigation was carried out in this work to examine the impact of P-ITCs and N-ITCs for the proposed device.

From Eq. 11, to affirm the device linearity, the higher-order derivative of \(g_\mathrm{m}\) should be as minimum as possible. The 2nd and 3rd order derivative of \(g_\mathrm{m}\) (\(g_\mathrm{m2}\) and \(g_\mathrm{m3}\)) are calculated by using Eqs. 12 and 13, both of them affecting the device performance as they are accountable for harmonic distortion [27].

To maintain the linear characteristics of UTS-F-TFET, \(g_\mathrm{m2}\) and \(g_\mathrm{m3}\) should be very low because both are responsible for amplification distortion via signals for intermodulation distortions [31]. To define the optimal bias point for linear operation, zero cross over (ZC) point should be marked. The ZC-point locates the higher value of \(V_\mathrm{gs}\) for which \(g_\mathrm{m2}\) and \(g_\mathrm{m3}\) become equal to zero. The impact of ITCs on \(g_\mathrm{m2}\) and \(g_\mathrm{m3}\) is illustrated in Fig. 16a and b, respectively. For the N-ITCs, values of \(g_\mathrm{m2}\) and \(g_\mathrm{m3}\) are minimum. Hence, N-ITCs helps to improve the linearity performance with suppressed 2nd and 3rd order harmonics of \(g_\mathrm{m}\).

The crucial intercept points are 2nd order voltage intercept point (\(\mathrm{VIP}_2\)), 3rd order voltage intercept point (\(\mathrm{VIP}_3\)) and 3rd order input intercept point (\(\mathrm{IIP}_3\)), these parameters should be high to exhibit distortion-less and linear characteristics of UTS-F-TFET. \(\mathrm{VIP}_2\) depicts the projected input voltage in which the 1st and 2nd order harmonic voltages are identical. Similarly, the \(\mathrm{VIP}_3\) exhibits the measured input voltage when the 1st and 3rd order harmonic voltages are equal, while the \(\mathrm{IIP}_3\) represents the estimated input power when the 1st and 3rd order harmonic powers are equal [33, 34].

From Fig. 17a, the peak of \(\mathrm{VIP}_2\) shifts towards the lower \(V_\mathrm{gs}\) with the application of P-ITCs consideration, and opposite behavior can be seen for N-ITCs. But, \(\mathrm{VIP}_2\) attain the maximum peak for the N-ITCs. So, we can say that stronger linear properties can be achieved with higher \(V_\mathrm{gs}\) and N-ITCs consideration.

\(\mathrm{VIP}_3\) inversely proportional to the 3rd order derivative of \(g_\mathrm{m}\), as depicted in Eq. 15. To ensure the suppression of the third-order harmonic, we need a high value of \(\mathrm{VIP}_3\). As we previously discussed with Fig. 16b, \(g_\mathrm{m3}\) reduces with P-ITCs. Hence \(\mathrm{VIP}_3\) is enhanced for P-ITCs with maximum peaks of 4.2 V (First peak) and 3.4 V (Second peak) with reducing \(V_\mathrm{gs}\), as shown in Fig. 17b.

Relation between the product of \(g_\mathrm{m3}\) \(R_\mathrm{s}\) and \(\mathrm{IIP}_3\) is given by Eq. 16, where \(R_\mathrm{s}\) = 50 \(\Omega\) for Radio Frequency applications. \(IIP_3\) should be large for superior linearity performance since we require minimal \(g_\mathrm{m3}\) and high \(g_\mathrm{m}\) with a constant value of \(R_\mathrm{s}\) [35]. Figure 17c exhibits the fluctuation of \(\mathrm{IIP}_3\) for various ITCs. \(\mathrm{IIP}_3\) improves with P-ITCs for lower \(V_\mathrm{gs}\) (0.0–0.20 V), but its show asymmetric behavior towards ITCs variation for higher value of \(V_\mathrm{gs}\) (0.75–1.5 V). The peak of \(\mathrm{IIP}_3\) achieved for the P-ITCs, thus best linearity performance of device can be achieved for P-ITCs.

The mathematical expression of \(\mathrm{IMD}_3\) and \(1-\mathrm{dB}\) compression point (\(1-\mathrm{CP}\)) is given by Eqs. 17 and 18, respectively. \(\mathrm{IMD}_3\) denotes the third-order intermodulation distortion, which must be low amplitude to reduce the converse effect on one electrode (drain) to the second electrode (gate) when we apply voltages on both electrodes. Lower value of \(\mathrm{IMD}_3\) also helps to prevent the wastage of usable power [36]. From Fig. 18a, the \(\mathrm{IMD}_3\) level is up to 0 to − 20 dBm when the device is in saturation state (in ON-state) without the effect of ITCs impact. But, the minimum rage of \(\mathrm{IMD}_3\) (approx. − 700 dBm) is obtained when the device is yet to start for N-ITCs. For The P-ITCs, the minimal range of \(\mathrm{IMD}_3\) is approximately − 300 dBm, which may degrade the device performance.

The \(1-\mathrm{CP}\) depicts the start of distortion when the input power reduces the gain by \(1-\mathrm{dB}\) [37]. The impact of P-ITCs and N-ITCs on the \(1-\mathrm{CP}\) for UTS-F-TFET is shown in Fig. 18b. The value of \(1-\mathrm{CP}\) is decreased in the case of P-ITCs because of low distortion in signal and enhanced value of \(g_\mathrm{m}\) compared to the N-ITCs. P-ITCs lead to enhancement in \(1-\mathrm{CP}\) values, and the opposite impact is shown for N-ITCs.

7 Reliability analysis

This section highlights the device’s reliability issues over different ITCs. In this detailed investigation, we observed that the impact of ITCs variation on \(I_\mathrm{on}\) is very low. Another side, \(I_\mathrm{ambi}\) of UTS–TFET device increases with reduced \(V_\mathrm{on}\) for P-ITCs. The \(I_\mathrm{on}/I_\mathrm{off}\) ratio drastically deteriorates with P-ITCs, but it will improve with the N-ITCs. The OFF-state analysis is carried out to investigate the T and ITCs on impact \(I_\mathrm{ambi}\) with variation in models. Because the SRH and TAT models are highly dependent on temperature, the proposed device’s ambipolar behavior improves with T for P-ITCs. The high-frequency performance parameters are similarly affected by variations in ITCs. With the use of a pie chart, the percentage deviation in analog and RF parameters is investigated and portrayed in Fig. 19a. In the same way, Figure 19b shows the impact on linearity parameters. As a result of a rigorous inspection of the proposed device’s ON- and OFF-state, high frequency, and linearity performance, it can be assessed that the UTS-F-TFET is much more insusceptible towards the effects of ITCs variation, thus making the device more reliable.

8 Conclusion

In this article, a comparative study is carried out to select the best suited lower bandgap material for the source region to enhance the \(I_\mathrm{on}\) of the proposed device. Along with this, we have investigated the Analog/RF, linearity, and reliability performance of UTS-F-TFET device by examining the impact of P-ITCs and N-ITCs at the silicon/oxide interface. In addition, the impact of temperature on OFF-state current component of UTS-F-TFET is also analyzed with ITCs variation. The comprehensive study shows that the ambipolar conduction significantly increases with temperature and SRH+TAT models for P-ITCs. But \(g_\mathrm{m}\) and \(f_\mathrm{t}\) of the proposed device increased with P-ITCs, which indicates that switching speed and bandwidth of the proposed device are enhanced for P-ITCs. The linearity figure of merit \(g_\mathrm{m2}\), \(g_\mathrm{m3}\) is enhanced for the N-ITCs, but lower value of these parameters is required to maintain the linearity of the device. The linearity and reliability of UTS-F-TFET are improved for the P-ITCs. The minor enhancement/degradation of UTS-F-TFET performance in the presence of P-ITCs/N-ITCs makes it a reliable option for high-frequency, low-power, and distortionless applications.

The manuscript follows all the ethical standards, including plagiarism.

Availability of data and material

All relevant data has been included in manuscript.

References

S.-W. Sun, P.G. Tsui, Limitation of cmos supply-voltage scaling by mosfet threshold-voltage variation. IEEE J. Solid-State Circuits 30(8), 947–949 (1995)

M.-H. Tsai, T.-P. Ma, The impact of device scaling on the current fluctuations in mosfet’s. IEEE Trans. Electron Dev. 41(11), 2061–2068 (1994)

S.O. Koswatta, M.S. Lundstrom, D.E. Nikonov, Performance comparison between pin tunneling transistors and conventional mosfets. IEEE Trans. Electron Dev. 56(3), 456–465 (2009)

U. E. Avci, R. Rios, K. J. Kuhn, I. A. Young, Comparison of power and performance for the tfet and mosfet and considerations for p-tfet. In: 2011 11th IEEE International Conference on Nanotechnology. IEEE, (2011), pp. 869–872

U.E. Avci, D.H. Morris, I.A. Young, Tunnel field-effect transistors: prospects and challenges. IEEE J. Electron Dev. Soc. 3(3), 88–95 (2015)

J. Bizindavyi, A.S. Verhulst, Q. Smets, D. Verreck, B. Sorée, G. Groeseneken, Band-tails tunneling resolving the theory-experiment discrepancy in esaki diodes. IEEE J. Electron Dev. Soc. 6, 633–641 (2018)

W.Y. Choi, B.-G. Park, J.D. Lee, T.-J.K. Liu, Tunneling field-effect transistors (tfets) with subthreshold swing (ss) less than 60 mv/dec. IEEE Electron Dev. Lett. 28(8), 743–745 (2007)

K. Nigam, D. Sharma et al., Approach for ambipolar behaviour suppression in tunnel fet by workfunction engineering. Micro Nano Lett. 11(8), 460–464 (2016)

Prabhat, D.S. Yadav, Design and investigation of f-shaped tunnel fet with enhanced analog/rf parameters. Silicon, pp. 1–16 (2021)

P. Singh, D.S. Yadav, Impactful study of f-shaped tunnel fet. Silicon, pp. 1–7 (2021)

S. Yun, J. Oh, S. Kang, Y. Kim, J.H. Kim, G. Kim, S. Kim, F-shaped tunnel field-effect transistor (tfet) for the low-power application. Micromachines 10(11), 760 (2019)

S. Kumar, D.S. Yadav, Assessment of interface trap charges on proposed tfet for low power high-frequency application (2021)

C.K. Pandey, A. Singh, S. Chaudhury, Analysis of interface trap charges on dielectric pocket soi-tfet. In: Devices for Integrated Circuit (DevIC). IEEE 2019, pp. 337–340 (2019)

Z. Jiang, Y. Zhuang, C. Li, P. Wang, Y. Liu, Impact of interface traps on direct and alternating current in tunneling field-effect transistors. J. Electr. Comput. Eng. 2015 (2015)

S.W. Kim, J.H. Kim, T.-J.K. Liu, W.Y. Choi, B.-G. Park, Demonstration of l-shaped tunnel field-effect transistors. IEEE Trans. Electron Dev. 63(4), 1774–1778 (2015)

T. Silvaco, Manuals. atlas (Silvaco Intematiailal. Co, USA, 2021)

P. Venkatesh, K. Nigam, S. Pandey, D. Sharma, P.N. Kondekar, Impact of interface trap charges on performance of electrically doped tunnel fet with heterogeneous gate dielectric. IEEE Trans. Dev. Mater. Reliab. 17(1), 245–252 (2017)

S. Chander, S.K. Sinha, S. Kumar, P.K. Singh, K. Baral, K. Singh, S. Jit, Temperature analysis of ge/si heterojunction soi-tunnel fet. Superlatt. Microstruct. 110, 162–170 (2017)

N. Parmar, P. Singh, D.P. Samajdar, D.S. Yadav, Temperature impact on linearity and analog/rf performance metrics of a novel charge plasma tunnel fet. Appl. Phys. A 127(4), 1–9 (2021)

D.S. Yadav, D. Sharma, R. Agrawal, G. Prajapati, S. Tirkey, B.R. Raad, V. Bajaj, Temperature based performance analysis of doping-less tunnel field effect transistor. In: 2017 International Conference on Information, Communication, Instrumentation and Control (ICICIC). IEEE, pp. 1–6 (2017)

S. Kumar, D.S. Yadav, Temperature analysis on electrostatics performance parameters of dual metal gate step channel tfet. Appl. Phys. A 127(5), 1–11 (2021)

A. Dixit, D.P. Samajdar, N. Bagga, D.S. Yadav, Performance investigation of a novel gaas1-xsbx-on-insulator (gasoi) finfet: role of interface trap charges and hetero dielectric. Mater. Today Commun. 26, 101964 (2021)

S. Sharma, R. Basu, B. Kaur, Interface trap charges associated reliability analysis of si/ge heterojunction dopingless tfet. Dev. Syst. IET Circuits (2021)

P.G. Der Agopian, M.D.V. Martino, S.G. dos Santos Filho, J.A. Martino, R. Rooyackers, D. Leonelli, C. Claeys, Temperature impact on the tunnel fet off-state current components. Solid-State Electron. 78, 141–146 (2012)

K. Nigam, S. V. Singh, P. Kwatra, Investigation and design of stacked oxide polarity gate jltfet in the presence of interface trap charges for analog/rf applications. Silicon, pp. 1–18 (2021)

N. Parmar, D. S. Yadav, S. Kumar, R. Sharma, S. Saraswat, A. Kumar, Performance analysis of a novel dual metal strip charge plasma tunnel fet. In: 2020 IEEE International Students’ Conference on Electrical, Electronics and Computer Science (SCEECS). IEEE, pp. 1–5 (2020)

N. Kumar, A. Raman, Design and analog performance analysis of charge-plasma based cylindrical gaa silicon nanowire tunnel field effect transistor. Silicon, pp. 1–8 (2019)

B.V. Chandan, K. Nigam, D. Sharma, S. Pandey, Impact of interface trap charges on dopingless tunnel fet for enhancement of linearity characteristics. Appl. Phys. A 124(7), 1–6 (2018)

P. Singh, D.P. Samajdar, D.S. Yadav, A low power single gate l-shaped tfet for high frequency application. In: 6th International Conference for Convergence in Technology (I2CT). IEEE 2021, pp. 1–6 (2021)

B.R. Raad, D. Sharma, P. Kondekar, K. Nigam, D.S. Yadav, Drain work function engineered doping-less charge plasma tfet for ambipolar suppression and rf performance improvement: a proposal, design, and investigation. IEEE Trans. Electron Dev. 63(10), 3950–3957 (2016)

D.S. Yadav, D. Sharma, S. Tirkey, D.G. Sharma, S. Bajpai, D. Soni, S. Yadav, M. Aslam, N. Sharma, Hetero-material cptfet with high-frequency and linearity analysis for ultra-low power applications. Micro Nano Lett. 13(11), 1609–1614 (2018)

D.S. Yadav, D. Sharma, B.R. Raad, V. Bajaj, Impactful study of dual work function, underlap and hetero gate dielectric on tfet with different drain doping profile for high frequency performance estimation and optimization. Superlatt. Microstruct. 96, 36–46 (2016)

S. Tirkey, D.S. Yadav, D. Sharma, Controlling ambipolar current of dopingless tunnel field-effect transistor. Appl. Phys. A Mater. Sci. Process. 124(12), 809 (2018)

D.S. Yadav, A. Verma, D. Sharma, S. Tirkey, B.R. Raad, Comparative investigation of novel hetero gate dielectric and drain engineered charge plasma tfet for improved dc and rf performance. Superlatt. Microstruct. 111, 123–133 (2017)

N. Kumar, A. Raman, Performance assessment of the charge-plasma-based cylindrical gaa vertical nanowire tfet with impact of interface trap charges. IEEE Trans. Electron Dev. 66(10), 4453–4460 (2019)

J. Madan, R. Chaujar, Interfacial charge analysis of heterogeneous gate dielectric-gate all around-tunnel fet for improved device reliability. IEEE Trans. Dev. Mater. Reliab. 16(2), 227–234 (2016)

D.A. Buchanan, Scaling the gate dielectric: materials, integration, and reliability. IBM J. Res. Dev. 43(3), 245–264 (1999)

Acknowledgements

The authors would like to thank Dr. Dip Prakash Samajdar from Department of Electronics and Communication Engineering, PDPM Indian Institute of Information Technology, Design & Manufacturing, Jabalpur, Madhya Pradesh, India for providing valuable suggestions and support to carry out this research work.

Funding

Not applicable.

Author information

Authors and Affiliations

Contributions

PS: Conceptualization, data curation, formal analysis, methodology, investigation, writing-original draft. DSY: Supervision, validation, visualization, writing-review and editing.

Corresponding author

Ethics declarations

Conflict of interest

No conflicts of interest.

Consent for publication

We are giving consent to publish.

Consent to participate

We are giving consent to participate.

Research involving human participants and/or animals

No.

Informed consent

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Singh, P., Yadav, D.S. Performance analysis of ITCs on analog/RF, linearity and reliability performance metrics of tunnel FET with ultra-thin source region. Appl. Phys. A 128, 612 (2022). https://doi.org/10.1007/s00339-022-05741-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-022-05741-4