Abstract

In this paper, a first qualitative study on the performance characteristics of dual-work function gate junctionless TFET (DWG-JLTFET) on the basis of energy band profile modulation is investigated. A dual-work function gate technique is used in a JLTFET in order to create a downward band bending on the source side similar to PNPN structure. Compared with the single-work function gate junctionless TFET (SWG-JLTFET), the numerical simulation results demonstrated that the DWG-JLTFET simultaneously optimizes the ON-state current, the OFF-state leakage current, and the threshold voltage and also improves average subthreshold slope. It is illustrated that if appropriate work functions are selected for the gate materials on the source side and the drain side, the JLTFET exhibits a considerably improved performance. Furthermore, the optimization design of the tunnel gate length (L Tun) for the proposed DWG-JLTFET is studied. All the simulations are done in Silvaco TCAD for a channel length of 20 nm using the nonlocal band-to-band tunneling (BTBT) model.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Over the past several decades, CMOS technology has been scaled down tremendously in order to increase integration density, operation speed, and energy proficiency. As we scale down the conventional metal–oxide–semiconductor FET (MOSFET) to sub-20 nm regimes, it encounters critical challenges and major obstacles in the fabrication of ultra-sharp doping gradient at the source and drain junction [1, 2]. Due to these fabrication difficulties, the performance characteristics of MOS devices have deteriorated by various short-channel effect (SCE), such as surface scattering, drain-induced barrier lowering (DIBL) and so on [3, 4]. The carrier injection in the source–channel junction of the MOSFET is dominated by thermionic emission mechanism over the potential barrier that is also increased because of this antagonistic scaling, and hence, the inverse subthreshold swing is limited to 60 mV/decade at room temperature [5]. Therefore, tunnel FET (TFET) is one of the alternative candidates to substitute CMOS technology which is most suitable for low-power applications [6–8]. Unlike MOSFET, TFET is not restricted by the thermionic emission constraint since the carrier injection mechanism from source to channel in the TFET is by band-to-band tunneling (BTBT) which could enable SS lower than kT/q limits of conventional MOSFETs [9–12]. Due to the channel, current is controlled by the quantum tunneling mechanism on the source side; TFETs are less prone to short-channel effects (such as V T roll-off) unlike the conventional MOSFETs [13–15]. However, TFETs suffer from several drawbacks such as ambipolarity, low ON-state current (I ON) as reported in the literature [16–18]. Besides, it is problematic that the SS values of experimentally proved silicon TFET are higher than expected values. In order to overcome these problems, different techniques such as low band gap materials, high-k gate insulators, strained silicon and dual-work function gate concept have been used [19–22]. Moreover, the current saturation mechanism in the output characteristics in a TFET is completely different from a conventional MOSFET [23]. As a result, TFETs often represent delayed saturation in the output characteristics. In addition, the dependence of the drain current on the drain voltage in a TFET is quite dissimilar from a conventional MOSFET [23]. Significant drain-induced barrier lowering (DIBL) effects are sometimes unveiled in a TFET, and this limitation can drastically reduce the efficiency of the device. Therefore, to treat TFETs for low-power CMOS applications, it is favorable that the overall performance characteristics of the TFET must be improved. Recently, junctionless tunnel FET (JLTFET) has represented tremendous potential as it blends advantages of JLTFET, which has high ON-current and TFET, which has low subthreshold slope [24–27]. A JLTFET is basically a uniformly doped junctionless transistor, which utilizes the work function engineering concept to behave analogously to any metallurgical junction. Due to the presence of uniform doping concentration, it has better scalability and low short-channel effects (SCEs). The JLTFET has been proposed as a solution for the various problems encountered in conventional CMOS technology such as scalability, low SS, and ON/OFF current ratio. JLTFETs also make a feature of high speed because of relatively large drive current and at the same time highly suppressed leakage current [28, 29]. Although the subthreshold slope of JLTFET is less than 60 mV/decade at room temperature, ON-state current is still inadequate to use in the present CMOS technology. In this paper, we present the application of dual-work function gate (DWG) in a double-gate junctionless TFET (JLTFET) by means of work function engineering concept. Using calibrated 2D numerical simulations, we prove that by engineering the work functions of the dual gates, it is possible to improve the ON-state current I ON, the OFF-state current I OFF, and the threshold voltage V T and also optimize the subthreshold slope SSavg. The dual-work function gate has been studied considerably and has been treated in not only ultra-scale MOSFETs [30–32], but also in power MOSFETs [33, 34]. However, the calibration of dual-work function gate concept in a JLTFET to enhance its ON-current and the subthreshold slope has not been reported.

The rest of this paper is organized as follows: Sect. 2 elaborates the physical structure of DWG-JLTFET and the simulation model used in this study. Section 3 represents simulation results for a DWG-JLTFET and demonstrates the privilege of using a DWG. In this section, the proposed dual-work function gate JLTFET (DWG-JLTFET) is compared with single-work function gate JLTFET (SWG-JLTFET) which taking scandium (Sc) with the work function of 4.0 eV and tungsten (W) with the work function of 4.4 eV as the gate material with a gate length of 20 nm. Also, in the proposed structure a local conduction band minima, E c due to the low work function of the tunnel gate near the source end are observed, whose effect will be investigated in this section. The analysis of the DWG-JLTFET has been accomplished for V DD = 1.0 V. Finally, Sect. 4 draws important conclusions out of this study.

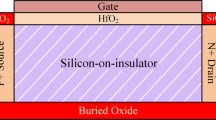

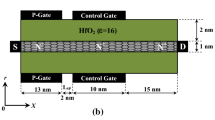

2 Device structure and simulation

The sketch of the proposed dual-work function double-gate junctionless tunnel FET (DWG-JLTFET) and its cross section along the channel are shown in Fig. 1. The parameters for the DWG-JLTFET used in our simulation are [24]: source/drain/channel doping = 1 × 1019/cm3, silicon film thickness (t Si) = 5 nm, gate oxide thickness (t ox) = 2 nm, and isolation layer between SG and TG (L sp) = 5 nm, source/drain extension length (L S/D) = 20 nm, channel length (L G) = 20 nm, tunnel gate length (L Tun) = 6 nm, and auxiliary gate length (L Aux) = 14 nm. The double-gate technology is utilized to provide better electrostatic controllability of gate over the channel. In this feature, both top and bottom gated in the channel region are comprised of materials with two different work functions. We refer to the gate closer to the source region as the tunnel gate (TG) which controls the tunneling generation rate at the source–channel junction. The one closer to the drain as the auxiliary gate (AG) and its work function variation mainly controls the OFF-current. For the proposed device characterization, we have taken the tunnel gate and auxiliary gate metals with the work function of 4.0 and 4.4 eV, respectively. The length of the tunnel gate is L Tun = 6 nm and that of the auxiliary gate is L Aux = 14 nm. Moreover, we have used a source metal electrode platinum (Pt) with a work function of 5.93 eV to make the layer beneath side gate (SG) p + source region. This is while the (TG + AG) in the channel region is used to modulate the effective tunneling barrier on the source and drain side. The integration of SG above the source region and (TG + AG) above the channel region together in the fabrication process, whose work functions are different, could be done by using the techniques as reported in Refs. [35–37]. The formation of the isolation layer with thickness of 5 nm of SiO2 between SG and TG could be done either by using a sputtering process or other modern gate dielectric fabrication process such as atomic layer deposition (ALD) after formation of the field oxide by wet oxidation.

The technology computer aided design (TCAD) simulation has been evaluated by using 2D-ATLAS device simulator [35]. We use nonlocal band-to-band tunneling (BTBT) model [36] to account for the spatial profile of the energy bands and also to account for the spatial separation of electrons generated in the conduction band from the holes generated in the valence band. We comprise the effect of Fermi–Dirac statistics in the calculation of the intrinsic carrier concentration required in the expressions for Shockley–Read–Hall (SRH) recombination. To capture the effect of temperature-dependent mobility, a concentration-dependent mobility (CONMOB) model and parallel and perpendicular electric field-dependent mobility (FLDMOB) model are used. Due to the presence of high doping concentrations, band gap narrowing (BGN) and auger recombination (AUGER) models are included in the simulations. Moreover, to assume high impurity atom in the channel and also to taking into account an interface trap (or defect), the Shockley–Read–Hall (SRH) recombination mode is enabled [37]. To include quantum confinement effects at the Si/SiO2 interface due to heavy doping concentration and thin oxide thickness, Quantum Confinement (HANSCHQM) model given by Hansch [38] is considered. Trap-assisted tunneling (SCHENK.TUNN) model given by Schenk [39] to account for interface trap effect on electron band-to-band tunneling in TFETs is enabled. The simulation model used in this paper, including tunneling model, has also been used in our previous works [26, 27]. Moreover, for validation of the device, conventional JLTFET reported by Ghosh and Akram [24] has been implemented and simulated. The simulated I D–V GS characteristics of this implemented device are calibrated with reported results as shown in Fig. 2. Then, the calibrated conventional JLTFET is scaled to work function and gate-to-source voltage values that are considered in this work.

Calibration for simulation results with the data extracted from [24] under the same conditions

3 Results and discussion

At first, the impact of the work function of the auxiliary gate (Φ Aux) on the OFF-state leakage current, I OFF in a DWG-JLTFET is analyzed. The analysis is accomplished in the same way as it is done in DWG-DGTFET [22]. Figure 3a, b illustrates the variation in the energy band diagram profile of the device as Φ Aux is increased while keeping Φ Tun fixed at 4.0 eV. In the OFF-state (Fig. 3a), as Φ Aux is increased, the tunneling barrier width on the source side increases which results in a significant suppression of the tunneling probability of electrons in the OFF-state. This behavior originates from the smaller band overlap on the source side of the proposed device. The OFF-state current is comprised of BTBT current plus reverse leakage current, as Φ Aux increases up to 4.4 eV; the current flow will be governed by reverse leakage current phenomena since there is no tunneling path. However, with further increase in Φ Aux (>4.4 eV), band overlap starts to appear on the drain side, and if the tunneling barrier width on the drain side becomes narrow enough (as in the case of Φ Aux = 4.8 eV), tunneling can happen in the OFF-state. In the ON-state (Fig. 3b), an increase in Φ Aux does not bring any considerable change in the energy band diagram profile. In this case, the tunnel barrier width modulation between source and channel is negligible and as a result, the electrons tunneling probability is not significantly affected. The transfer characteristics of the DWG-JLTFET while Φ Aux is increased from 4.0 to 4.8 eV, are shown in Fig. 3c. The OFF-state current of the proposed structure, which is defined as the drain-to-source current I DS at V GS = 0 V and V DS = 1 V is considerably affected and exhibits more than two orders of magnitude improvement when Φ Aux ≥ 4.4 eV. However, the ambipolar current which is the tunneling of holes from conduction band of drain-to-valence band of channel begins to flow due to the decrement in tunneling width at the drain–channel interface and further band overlap on the drain side when Φ Aux ≥ 4.8 eV; hence, the drain current starts increasing by the tunneling of holes rather than tunneling of electrons at the opposite end (source–channel interface) in the negative gate voltages. The ON-state current of DWG-JLTFET which is defined as the drain-to-source current I DS at V GS = 1 V and V DS = 1 V, is not diminished seriously. In other words, the flow of minority charge carriers from valence band of source region to the conduction band of channel region does not change considerably.

For DWG-JLTFET with Φ Tun = 4.0 eV, L Tun = 6 nm and L Aux = 14 nm a OFF-state band diagram profile along x-direction (V GS = 0 V, V DS = 1 V). b ON-state band diagram profile along x-direction (V GS = 1.5 V, V DS = 1 V). c Transfer characteristics of DWG-JLTFET with variation of auxiliary gate work function at V DS = 1 V

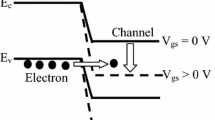

Afterward, the impact of the tunnel gate work function (Φ Tun) on the characteristics (I ON) of a DWG-JLTFET is examined. Figure 4a, b illustrates the variation in the energy band diagram profile of the device as Φ Tun is decreased while keeping Φ Aux fixed at 4.4 eV. In the OFF-state (Fig. 4a), a local conduction band minima, E c is observed in the energy band diagram profile on the source side when Φ Tun is reduced to 4.0 eV. However, there is no significant band overlap on the source side occurs because of conduction band minima (E c). Hence, in the OFF-state, we obtained a quite low BTBT rate which gives as expected low I OFF. But, in the ON-state (Fig. 4b), due to this energy band diagram modulation caused by the reduction in Φ Tun, the tunneling barrier width of the DWG-JLTFET considerably becomes small. So, there is a high probability of tunneling of electrons from the occupied states of the valence band of the source side into the unoccupied states of the conduction band of the channel. Consequently, it will result in an improved ON-current of the proposed structure. The electrical characteristics of the DWG-JLTFET are studied with the reduction of Φ Tun from 4.8 to 4.0 eV keeping Φ Aux fixed at 4.4 eV as shown in Fig. 4c. As predicted, the ION enhances by about one order of magnitude. The I OFF is relatively at the same value for all the work function values of Φ Tun. The threshold (V T) of the DWG-JLTFET which is defined as the gate-to-source voltage V GS where the drain current is 10−7 A/µm [39], is appropriately improved and reduced to 0.48 V at Φ Tun = 4.0 V.

For DWG-JLTFET with Φ Aux = 4.4 eV, L Tun = 6 nm, and L Aux = 14 nm a OFF-state band diagram profile along x-direction (V GS = 0 V, V DS = 1 V). b ON-state band diagram profile along x-direction (V GS = 1.5 V, V DS = 1 V). c Transfer characteristics of DWG-JLTFET with variation of tunnel gate work function at V DS = 1 V

The abovementioned analysis demonstrates using a dual-work function gate concept (TG, AG) in the DWG-JLTFET provides additional capability to control different section of the transfer characteristics results in improving TFET performance operation. It can be seen from Fig. 4c, when we decrease Φ Tun to 4.0 eV, the I ON increases, and V T decreases. Since the conventional SWG-JLTFET suffers from a relatively low I ON and high V T, it is favorable to determine the device parameter to obtain a maximum value of I ON and a minimum value of V T. Also, from the Fig. 3c it is observed that when we increase Φ Aux, the I OFF decreases, but with further increase Φ Aux > 4.4 eV the ambipolar conduction significantly increases leading to lower I ON/I OFF. Therefore, the best possible values for both the tunnel and auxiliary gate are 4.0 and 4.4 eV, respectively. There are several metals nominates that can be engineered to obtain the desirable Φ Tun (4.0 eV) (e.g., Mo, Ni–Ti, and Sc) and Φ Aux (4.4 eV) (e.g., W, Ta, and Mo) [40–45].

The I D–V GS curve of DWG-JLTFET and comparable SWG-JLTFET with different work functions at the drain-to-source voltage V DS = 1 V are shown in Fig. 5. This implicates the good electrostatic integrity of DWG-JLTFET over SWG-JLTFET. It is clear that using dual-work function over SWG-JLTFET. It is clear that using dual-work function gate (DWG) technique, we can provide an enhanced ON-state current as well as improved I OFF, which cannot be achieved by using SWG-JLTFET. Therefore, the I ON/I OFF ratio increases to 1.52 × 109 from 0.58 × 108, which is the best possible value of the SWG-JLTFET by adjusting the gate work function at Φ = 4.4 eV in the simulation. It is observed that at low gate voltage, the OFF-state current of DWG-JLTFET is followed by auxiliary gate (Φ Aux = 4.4 eV) where a low I OFF is achieved and the ON-state current of DWG structure is followed by tunnel gate (Φ Tun = 4.0 eV) at high gate voltage, which gives rise to high value of I ON. Indeed, this treatment implicates that the OFF-state current of the DWG-JLTFET is controlled by the auxiliary gate at low V GS and the ON-state current is controlled by tunnel gate at high gate voltage. As a result, the DWG-JLTFET has simultaneously high ION and low I OFF which is not achievable by use of an SWG-JLTFET. Furthermore, the subthreshold slope SS is lower than that of the SWG-JLTFET, not only for the point SSp extracted from taking off point (V OFF, I OFF) shown in Fig. 5, but also for the average SSavg which is defined as:

where V T is the threshold voltage extracted at the drain-to-source current I DS = 10−7 A/µm [39]. The SSp significantly improves from 37.62 mV/dec in the SWG-JLTFET to 24.21 mV/dec in the DWG-JLTFET and for the SSsvg from 64.8 to 52.12 mV/dec at given V DS = 1 V. It is noteworthy that the manipulation of gate work function in the conventional SWG-JLTFET only shifts the transfer characteristics parallel to the x-axis which does not affect the SS.

The surface potential, lateral electric field, and electron velocity distribution along the channel in the DWG-JLTFET and the corresponding SWG-JLTFET are further investigated in Fig. 6. Contradictory to conventional MOSFET which has a steep potential rising and an electric field peak in the drain side [35, 36], the TFET keeps them on the source side where the quantum band-to-band tunneling (BTBT) occurs. As shown in Fig. 6a, an opposite potential trend emerges at the interface of the two gates of the proposed DWG-JLTFET. This phenomenon originates from a higher work function is used for the auxiliary gate (Φ Aux = 4.4 eV) (Fig. 7). Due to the aforementioned potential step, a negative electric field appears at the transition of two gates as shown in Fig. 6b. This part of electric field decreases the average velocity of electrons which establish in the channel region by means of indirect BTBT in the OFF-state (Fig. 6c). As a consequence, reasonable work function leads to next, we analyze the impact of tunnel gate length (L Tun) to reduce the opportunity of OFF-state tunneling on the drain side, and consequently, the setting helps to suppress the OFF-state leakage current I OFF variation on the electrical characteristic of the proposed DWG-JLTFET and we also find an optimum value of the of tunnel gate length (L Tun) for the given V DS = 1 V. Figure 7 illustrates the change in the transfer characteristics curve of the proposed device as L Tun is increased. The tunnel gate length is varied from 4 to 14 nm, while keeping the total gate length L G = L Tun + L Aux unchanged. It can be concluded from the figure, as the length of the L Tun increases, the local E c minima on the source side become wider which makes the electrons to tunnels from the source to the channel without the applied gate bias. Thus, the region of the channel beneath the L Tun operates as a virtual source of electrons. So, this region under the L Tun creates a downward band bending similar to the PNPN structure [46, 47], which increases the electric field at the tunnel junction and reduces the source to channel tunnel path. As a result, the L Tun gate loses it controllability over the tunneling barrier width at low gate voltage, and for such a PNPN-like structure, the source–channel tunneling junction is not gate-controlled. In this situ, the L Aux takes control responsibility of transistor operation. Therefore, the tunneling barrier width modulation has saturated, and the transistor actually operates by means of lowering the barrier beneath the L Aux gate which is now analogous to MOSFET operation. As a result, this leads to a degradation of the subthreshold slope SS and an enhancement in leakage OFF-current I OFF in the device as L Tun length increases.

Figure 8 shows the dependence of the ON/OFF current ratio (I ON/I OFF) and the point subthreshold slope (SSp) of the proposed DWG-JLTFET with a variation of tunnel gate length (L Tun). When the L Tun starts to increase, as we explained in the previous section, the values of I ON/I OFF and SSp are degraded at room temperature of 300 K. However, for a range of L Tun values (2–6 nm), the DWG-JLTFET represents both a high ON/OFF current ratio and a low SSp exhibiting that the process-induced variations in L Tun will not affect its performance. The aforementioned analysis shows that the length of the tunnel gate can be adjusted for better I ON/I OFF and SSp. Since there is a low I ON/I OFF ratio when L Tun higher than 6 nm, we have chosen L Tun ≤ 6 nm. Finally, we have taken a tunnel gate length of 6 nm for our device simulation, which gives the optimized value of I ON/I OFF ratio and SSp. These simulation results reveal the fact that the utilization of a dual-work function gate to form the PNPN-like structure makes the DWG-JLTFET more attractive candidate compared to an SWG-JLTFET.

4 Conclusion

A comparative study of device physics of the DWG-JLTFET over the conventional SWG-JLTFET is explored through extensive 2D numerical simulations. These results demonstrate that the technique of using DWG can be applied to obtain superior characteristics, e.g., I ON, I OFF and I ON/I OFF ratio improvement and suppression of subthreshold slope SS, compared to the corresponding single-work function JLTFET (SWG-JLTFET). Thus, DWG-JLTFET has potential advantages in the low operation power (LOP) application. Moreover, it is observed that the length of tunnel gate considerably affects the device characteristics by changing channel controllability, as well as affect the tunneling probability. As a general guideline, L Tun = 6 nm and L Aux = 14 nm at L G = 20 nm and the corresponding work function values, Φ Tun = 4.0 eV and Φ Tun = 4.4 eV are proposed for the DWG-JLTFET performance optimization.

References

J.P. ColingeC, W. Lee, A. Afzalin, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. Oneil, A. Blake, M. White, A.M. Kelleher, B. McCarthy, R. Murphy, Nanowire transistors without junctions. Nat. Nanotechnol. 5, 225–229 (2010)

S. GundapaneniM, R.K. Bajaj, K.V.R.M. Pandey, S.Ganguly Murali, A. Kottantharayil, Effect of band-to-band tunneling on junctionless transistors. IEEE Trans. Electron Devices 59(4), 1023–1029 (2012)

R. GandhiZ, N. Chen, K.Banerjee Singh, S. Lee, Vertical Si-nanowire n-type tunneling FETs with low subthreshold swing (≤50 mV/decade) at room temperature. IEEE Electron Device Lett. 32(4), 437–439 (2011)

A. Mallik, A. Chattopadhyay, The impact of fringing field on the device performance of a p-channel tunnel field-effect transistor with a high-κ gate dielectric. IEEE Trans. Electron Devices 59(2), 277–282 (2012)

R.S. Muller, T.I. Kamins, M. Chan, Device Electronics for Integrated Circuits (Wiley, New York, 2003), pp. 443–445

W.Y. ChoiB, G. Park, J.D. Lee, T.J.K. Lee, Tunneling field effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

A.M. Ionescu, H. Riel, Tunnel field-effect transistors as energyefficient electronic switches. Nature 479(7373), 329–337 (2011)

R. Vishnoi, M.J. Kumar, Compact analytical model of dual material gate tunneling field effect transistor using interband tunneling and channel transport. IEEE Trans. Electron Devices 61(6), 1936–1942 (2014)

A.M. Ionescu, New functionality and ultralow power: key opportunities for post-CMOS era, in Proceedings of the International Symposium on VLSI Technology, Systems and Applcations, pp. 72–73, 2008

K.K. BhuwalkaS, A.K. Sedlmaier, C. Ludsteck, J.Schulze Tolksdorf, I. Eisele, Vertical tunnel field-effect transistor. IEEE Trans. Electron Devices 51(2), 279–282 (2004)

A.S. Verhulst, W.G. Vandenberghe, K. Maex, G. Groesenken, Tunnel field-effect transistor without gate-drain overlap. Appl. Phys. Lett. 91(5), 053102-1–053102-3 (2007)

S. Agarwal, G. Klimeck, M. Luisier, Leakage-reduction design concepts for low-power vertical tunneling field-effect ransistors. IEEE Electron Device Lett. 31(6), 621–623 (2010)

K.K. Bhuwalka, J. Schulze, I. Eisele, Scaling the vertical tunnel FET with tunnel bandgap modulation and gate work function engineering. IEEE Trans. Electron Devices 52(5), 909–917 (2005)

T. NirschlS, J. Henzler, M. Fischer, A.B. Flude, M. Stoffi, J. Sterkel, C. Sedlmeir, R. Weber, U. Heinrich, J. Schaper, R. Einfeld, U. Neubert, K. Feldmann, E. Stahrenberg, G. Rudere, A. Georgakos, R. Huber, W.Hansch Kakoschke, D.S. Lanssiedel, Scaling properties of the tunneling field effect transistor (TFET): device and circuit. Solid-State Electron. 50(1), 44–51 (2006)

S. Saurabh, M.J. Kumar, Impact of strain on drain current and threshold voltage of nanoscale double gate tunnel field effect transistor. Jpn. J. Appl. Phys. 48(6), 064503 (2009)

E.H. Toh, G.H. Wang, G. Samudra, Y.C. Yeo, Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. Appl. Phys. Lett. 90(26), 263507-1–263507-3 (2007)

O.M. NayfehC, N. Chleirigh, J. Hennessy, L. Gomez, J.L. Hoyt, D.A. Antoniadis, Design of tunneling field-effect transistors using strained-silicon/strained-germanium type-II staggered heterojunctions. IEEE Electron Device Lett. 29(9), 1074–1077 (2008)

J. AppenzellerY, M. Lin, J. Knoch, Z. Chen, P. Avouris, Comparing carbon nanotube transistors—the ideal choice: a novel tunneling device design. IEEE Trans. Electron Devices 52(12), 2568–2576 (2005)

A. Vandooren, R. Rooyackers, D. Leonelli, F. Iacopi, S.D. Gendt, A. Verhulst, M. Heyns, E. Kunnen, N.D. Nguyen, M. Demand, P. Ong, W. Lee, J. Moonens, O. Richards, W. Vandenberghe, G. Groeseneken, A 35 nm diameter vertical silicon nanowire short-gate tunnel FET with high-k/metal gate, in Proceedings of the IEEE Silicon Nanoelectronics Workshop, pp. 21–22, 2009

K. Boucart, W. Riess, A.M. Ionescu, Lateral strain profile as key technology booster for all-silicon tunnel FETs. IEEE Electron Device Lett. 30(6), 656–658 (2009)

C.-H. Shih, N.D. Chien, Sub-10-nm tunnel field-effect transistor with graded Si/Ge heterojunction. IEEE Electron Device Lett. 32(11), 1498–1500 (2011)

S. Saurabh, M.J. Kumar, Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans. Electron Devices 58(2), 404–410 (2011)

C. ShenS, L. Ong, C.H. Heng, G. Samudra, Y.C. Yeo, A variational approach to the two-dimensional nonlinear Poisson’s equation for the modeling of tunneling transistors. IEEE Electron Device Lett. 29(11), 1252–1255 (2008)

B. Ghosh, M.W. Akram, Junctionless tunnel field effect transistor. IEEE Electron. Device Lett. 34(5), 548–586 (2013)

P.K. Asthana, B. Ghosh et al., High-speed and low power ultradeep-submicrometer III–V heterojunctionless tunnel field-effect transistor. IEEE Electron Device Lett. 61(2), 479–486 (2014)

R.M.I. Abadiand, S.A.S. Ziabari, Representation of strained gate-all-around junctionless tunneling nanowire filed effect transistor for analog application. Microelectron. Eng. 162, 12–16 (2016)

R.M.I. Abadiand, S.A.S. Ziabari, Representation of type I heterostructure junctionless tunnel field effect transistor for high-performance logic application. Appl. Phys. A 122, 616–623 (2016)

S.O. KoswattaS, J. Koester, W. Hanench, On the possibility of obtaining MOSFET-like performance and sub-60 mV/dec swing in 1-D broken gap tunnel transistors. IEEE Trans. Electron Devices 57(12), 3222–3486 (2010)

U. Khan, B. Ghosh, M.W. Akram, Effect of self-heating on selective buried oxide and silicon on insulator based junction less transistors. J. Low Power Electronics 9(3), 295–301 (2013)

N. Cui, R. Liang, J. Xua, J. Xu, Heteromaterial gate tunnel field effect transistor with lateral energy band profile modulation. Appl. Phys. Lett. 2(2), 022111-1–022111-16 (2012)

G. LeeJ, S. Jang, W.Y. Choi, Dual-dielectric-constant spacer hetero-gate-dielectric tunneling field-effect transistors. Semicond. Sci. Technol. 28(5), 052001–052005 (2013)

M.J. Lee, W.Y. Choi, Effects of device geometry on hetero-gate-dielectric tunneling field-effect transistors. IEEE Electron Device Lett. 33(10), 1459–1461 (2012)

R.S. Saxena, M.J. Kumar, Dual material gate technique for enhanced transconductance and breakdown voltage of trench power MOSFETs. IEEE Trans. Electron Device 56(3), 517–522 (2009)

D.R. Lide, CRC Handbook on Chemistry and Physics, 89th edn. (Taylor & Francis, New York, 2008), pp. 12–114

W. Long, H. Ou, J.M. Kuo, K.K. Chin, Dual-material gate (DMG) field effect transistor. IEEE Trans. Electron Devices 46(5), 865–870 (1999)

K.Y. Na, Y.S. Kim, Silicon complementary metal-oxide semiconductor field-effect transistors with dual work function gate. Jpn. J. Appl. Phys. 45(12), 9033–9036 (2006)

C.H. Wangand, H. Chu, Y. S. Lai, Dual work-function metal gates. US Patent no. 73 81619B2, Jun 2008

ATLAS Users ManualSILVACO Int., Santa Clara, CA, 2009

K. Boucart, A.M. Ionescu, Double-gate tunnel FET with High-κ gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

A. Villalon, C.L. Royer, P. Nguyen, S. Barraud, F. Glowacki, A. Revelant, L. Selmi, S. Cristoloveanu, L. Tosti, C. Vizioz, J.M. Hartmann, N. Bernier, B. Previtali, C. Tabone, F. Allain, S. Martinie, O. Rozeau, M. Viner, First demonstration of strained SiGe nanowires TFETs with ION beyond 700 μA/μm, in Proceedings of the Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, pp. 66–67, 2014

W. HanschT, R.Kircher Vogelsang, M. Orlowski, Carrier transport near the Si/SiO2 interface of a MOSFET. Solid-State Electron. 32(10), 839–849 (1989)

A. Schenk, A model for the field and temperature dependence of SRH lifetimes in silicon. Solid State Electron. 35(11), 1585–1596 (1992)

P. Ranade, Y.C. Yeo, Q. Lu, Y.C. Yeo, H. Takeuch i, T.J. King, C. Hu, Molybdenum as a gate electrode for deep sub-micron CMOS technology, in Proceedings of the MRS Symposium, vol. 611, pp. C3.2.1–C3.2.6, 2000

I. Polishchuk, P. Ranade, T.J. King, C. Hu, Dual work function metal gate CMOS transistors by Ni–Ti interdiffusion. IEEE Electron Device Lett. 23(4), 200–202 (2002)

M. Hasan, H. Park, H. Yang, H. Hwang, H.S. Jung, J.H. Lee, Ultralow work function of scandium metal gate with tantalum nitride interface layer for n-channel metal oxide semiconductor application. Appl. Phys. Lett. 90(10), 103 510-1–103 510-3 (2007)

V.V. NagavarapuR, R. Jhaveri, J.C.S. Woo, The tunnel source (PNPN) n-MOSFET: a novel high performance transistor. IEEE Trans. Electron Devices 55(4), 1013–1019 (2008)

A. Tura, Z. Zhang, P. Liu, Y.H. Xie, J.C. Woo, Vertical silicon p–n–p–n tunnel nMOSFET with MBE-grown tunneling junction. IEEE Trans. Electron Devices 58(7), 1907–1913 (2011)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Molaei Imen Abadi, R., Sedigh Ziabari, S.A. Improved performance of nanoscale junctionless tunnel field-effect transistor based on gate engineering approach. Appl. Phys. A 122, 988 (2016). https://doi.org/10.1007/s00339-016-0530-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-016-0530-9