Abstract

DC-side voltage balancing is a critical problem to be solved for cascaded H-bridge energy storage converters. Aiming at inner-phase voltage balancing problem, a space vector pulse width modulation (SVPWM) algorithm with voltage balancing based on simplified vector is proposed. Firstly, the number of voltage vector is simplified by the proposed algorithm. Secondly, the action time of each level is calculated based on the volt-second balance, and the output vector is determined by comparing the DC-side voltage magnitude. Furthermore, the change of module level is minimal at the time of level change, and leapfrog hopping of the module level is prevented. Then, the inner-phase voltage balance can be achieved using vector selection. Due to the simplified SVPWM with voltage balancing, the algorithm is simpler, the switching losses is smaller, and it is easy to extend to cascaded H-bridge converters with more modules. Regarding the mutual-phase voltage balancing problem, the additional power generated by the zero-sequence voltage injection changes the power distribution among the three phases, so that the mutual-phase voltages is balanced. Finally, the effectiveness of the proposed control algorithm is verified by simulation and experimental results.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In recent years, the energy storage technology has gradually become an indispensable component in the stable operation of smart grid with the development of renewable energy [1, 2]. Currently, with the development of energy storage technology in the direction of high voltage and high power, it is of great significance to study high-capacity multilevel energy storage power converters. There are more advantages of CHB topology compared to CHB and other multilevel topologies [3, 4]. The CHB topology is more suitable to be used as a high-power energy storage converters structure due to its modularity, expandability, ease of meeting higher voltage and capacity design requirements, and grid-connectivity without the need for an additional transformer.

The CHB energy storage converters consist of multiple identical modules in cascade, each module consists of an energy storage unit and a full-bridge structure, and the energy storage unit is generally a lithium iron phosphate battery, a lead-acid battery, a supercapacitor, etc. In this paper, supercapacitor is used as an energy storage unit, due to the faster response, higher power density and longer service life compared to battery energy storage [5, 6]. However, considering the differences in capacity and internal resistance as well as losses in the production process of supercapacitors [7]. This can cause an imbalance in the DC-side voltage between modules, as well as over-charging and over-discharging phenomena, which can seriously endanger the service life of supercapacitors. Therefore, the balancing of DC-side voltage is especially critical for the energy storage system, which is a prerequisite for the safe and stable operation of the system.

Inner-phase balancing and mutual-phase balancing controls are commonly employed for DC-side voltage balancing problems in three-phase CHB energy storage systems. For the inner-phase balancing, there are mainly two kinds of hardware balancing and software balancing. In [8], a hardware balancing control by adding a DC–DC link on the DC-side is proposed, which has good control effect, but it is complicated to control and costly. Software balancing is more common than additional hardware balancing control, and software balancing can be subdivided into two categories: indirect control and direct control of voltage balancing. In [9, 10], each module is added an independent voltage balancing PI link in its control section, which is simple and easily scalable. In [11], it is proposed to inject a compensating component to change the modulating waveform to redistribute the module power and reach the voltage balance on the DC-side of the module, which is easy to implement and low cost. The above literatures are all based on carrier phase shifting-sinusoidal pulse width modulation (CPS-SPWM) indirectly controlled voltage balancing approach, which essentially adjusts the modulating waveforms of each module through independent voltage balancing control algorithms and thus changes the duty cycle to achieve the purpose of inner-phase balancing. But, the voltage balancing capability of this type of approach is weak and increases the burden on the system controller due to independent voltage balancing algorithm. Meanwhile, the control parameters of the algorithm are numerous and difficult to select.

For this reason, in [12,13,14], voltage balancing using SVPWM method with direct voltage control is proposed. This method can achieve voltage balancing by using the selection of redundant vectors, which has the advantages of strong voltage balancing capability, high-voltage utilization and simple control. In [15,16,17], SVPWM algorithms in different coordinate systems and the principle of redundant vector generation are studied. In [18] and [19], 1D-SVPWM on a one-dimensional straight line and 2D-SVPWM in a two-dimensional plane were proposed, respectively, which attracted more scholars to study SVPWM with voltage balancing algorithms. In [20,21,22], 3D-SVPWM with voltage balancing algorithm for three-module cascaded converters is proposed, which puts all the voltage vectors into a three-dimensional space for analysis. The above SVPWM algorithms are all able to achieve voltage balancing by selecting vectors, but they do not consider the case of module port level leapfrog hopping and simultaneous action, which will increase the switching losses. Also, with the increase of the number of cascades, the number of vectors will increase dramatically and the algorithm will be more complicated.

The main methods are negative-sequence current injection and zero-sequence voltage injection for mutual-phase balancing problem. In [23], mutual-phase balancing based on negative-sequence current injection is proposed but affects the input-side power quality due to the injection of negative-sequence currents, which is detrimental to the safe operation of the grid. In [24], a combination of hybrid modulation strategy and zero-sequence injection method is proposed for mutual-phase power balancing control, which has lower total harmonic distortion (THD) of the grid-side currents after balancing, but the control is more complicated.

Therefore, an easily scalable SVPWM algorithm with voltage balancing based on simplified vector is proposed in this paper using a three-phase CHB energy storage converters as the study topology. And the problems of high switching losses in the above literature and the sharp increase in the number of voltage vectors with the increase in the number of cascades are overcome by this algorithm. At first, the algorithm simplifies the voltage vectors with the goal of strong voltage balancing capability and low switching losses and selects the output vectors according to the magnitude of the DC-side voltage. Moreover, the change of module level is minimal when the level changes, and leapfrog hopping of the module level is prevented. Then, the inner-phase voltage balancing can be achieved using the selection of vectors. After that, the zero-sequence voltage injection method is used to achieve mutual-phase balancing control for more complex problems of mutual-phase voltage control. Finally, the correctness of the proposed method is verified by simulation and experimental results.

2 Modeling and power control

2.1 Mathematical modeling of energy storage converters

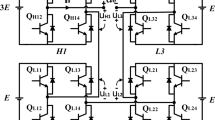

The topology of the CHB energy storage converters is shown in Fig. 1. The three phases of this converter are connected in star-arrangement with each phase consisting of n modules in cascade, and it is connected to the AC grid through filter reactors. In Fig. 1, usa, usb, and usc are the three-phase grid voltages, ua, ub, and uc are the three-phase output voltage of the converter, ia, ib and ic are the three-phase current of the converter, L is the grid-side filter reactor, R is the equivalent losses, Udca1, Udca2, and Udcan are the voltages of the supercapacitor of the energy storage unit, and C is the DC-side filter capacitance of the H-bridge of equal size. For example for phase A, Ua1b1, Ua2b2, and Uanbn are the output voltages of module 1, module 2, and module n, respectively, and the output phase voltage of the AC-side of phase A can be obtained as ua = Ua1b1 + Ua2b2 + Uanbn. When the DC-side voltage of the CHB converter is balanced, i.e., Udca1 = Udca2 = Udcan = Udc, different switch combinations can be used, and the phase voltage ua will have \(2n + 1\) levels from \(- n \cdot U_{dc}\) to \(n \cdot U_{{{\text{dc}}}}\).

The upper and lower switching devices operate in complementary states, for a single H-bridge module. Take the i-th module of phase A as an example, define the switching function Sai as:

where \(i = 1 \sim n\).

Then, the mathematical model of the CHB energy storage converters in the abc three-phase stationary coordinate system is obtained as:

where Udc is the supercapacitor output voltage when each module is balanced.

2.2 System power control

The various physical quantities to be determined for the time-varying alternating current due to the abc three-phase stationary coordinate system, which is more complex to analysis. Thus, the mathematical model under the abc coordinate system is converted by coordinate transformation to under the dq-axis synchronous rotating coordinate system, as in Eq. (3):

where usd, usq and id, iq and Sd, Sq denote the state quantities of the three-phase grid voltage and grid current and switching function of the AC-side in the dq coordinate system, respectively.

Neglecting the three-phase circuit equivalent losses and decoupling id and iq to achieve independent control of active and reactive power, the system power control block diagram of the CHB converters can be obtained, as shown in Fig. 2. P* and Q* are given for active and reactive power, and then, the reference voltage signals vd and vq in dq coordinate system are obtained through the current inner loop decoupling control; then, the output voltage modulated waveforms va*, vb* and vc* in abc coordinate system are obtained through the inverse Park’s transformation. Finally, the SVPWM algorithm with voltage balancing based on simplified vector can be used to obtain PWM signals, which can be distributed to each module to complete the overall control of the system.

3 SVPWM algorithm with voltage balancing based on simplified vector

3.1 Principle of SVPWM algorithm with voltage balancing

For a multilevel converter, each of its phase outputs can output a multilevel phase voltage with different phases and the same level. The phase voltage ua as the reference phase can be compared to a reference vector \(\vec{V}\), whose Y-axis is always zero, and its trajectory is plotted in a planar diagram. The principle of the three-module seven-level CHB, for example, is shown in Fig. 3, assuming that the voltage on the DC-side of the converter is balanced. In Fig. 3, the seven-level [− 3Udc, − 2Udc], [− 2Udc, − Udc], [− Udc, 0], [0, Udc], [Udc, 2Udc], and [2Udc, 3Udc] intervals are denoted as the R1, R2, R3, R4, R5, and R6 regions, respectively. When \(\vec{V}\) is moving in the positive half-axis of the X-axis, the corresponding phase voltage is positive, and its modulus represents the proportion of time that it acts in a given region (how long the vector operates in a given region is equal to the amount of time the phase voltage acts in that level interval). The motion of \(\vec{V}\) running from 0 increasing to 3Udc and then decreasing to 0 is equivalent to the period when the phase voltage is positive. The principle is the same when the vector moves in the negative half-axis of the X-axis as when the vector is in the positive half-axis of the X-axis.

Specifically, it is sufficient to determine that the reference vector \(\vec{V}\) is running in a certain region, and output the level of that region. Assuming that the vector \(\vec{V}\) is running in the R4 region, this causes the system to issue commands for levels 0 and Udc. The principles for phases B and C are the same as for phase A.

3.2 Calculation of leveling time

Taking the A-phase three-module cascade as an example, let the output phase voltages be -3Udc, − 2Udc, − Udc, 0, Udc, 2Udc, and 3Udc with the action times Ta−3, Ta−2, Ta−1, Ta0, Ta1, Ta2, and Ta3, and the switching period is Ts. When the reference vector \(\vec{V}\) is in the interval of [0, Udc], it can be obtained according to the volt-second balance:

Then, Ta0 and Ta1 can be solved as shown in Eq. (5):

Similarly, the action time of \(\vec{V}\) when it is in the region of R1, R2, R3, R4, R5, and R6 is shown in Table 1.

The time allocation can be done after calculating the action time for each level interval, and a three-stage allocation is used in this paper. The R1 to R6 area allocation is the same, take R5 as an example, as shown in Fig. 4. The carrier wave is a triangular wave, Ts is the carrier period, so the carrier amplitude is also Ts because of Ta1 + Ta2 = Ts. The smaller number of levels Ta1 is used as the modulating wave to compare with the carrier wave. The control signal TPWM is 0 and outputs the Udc level when the modulating wave is greater than or equal to the carrier wave. The control signal TPWM is 1 and outputs the 2Udc level, when the modulating wave is smaller than the carrier wave.

3.3 Principles of optimization for simplified vector algorithms

Knowing that each module can output a total of three states of 1, 0, and − 1, which correspond to three levels of Udc, 0, and − Udc, respectively, the A-phase three-module cascade converters can output 27 voltage vectors. Taking the output level number Ua1b1/Udc of the first module of phase A as La1 axis, the output level number Ua2b2/Udc of the second module as La2 axis, the output level number Ua3b3/Udc of the third module as La3 axis, the total phase voltage output level number is La, then:

where La, La1, La2, and La3 are integers and La \(\in [ - 3,3]\).

All the voltage vectors are located in the three-dimensional space of La1, La2, and La3 axes and form a cube, and the vector points with equal values of La can form a tangent plane, and the coordinate origin (0, 0, 0) is located in the center of gravity of the cube. Therefore, the A-phase seven-level converter space voltage vector diagram can be established, as shown in Fig. 5. It can be seen that the equal values of La are redundant vectors, which have the same output level but different voltage balancing effects; there are 27 voltage vectors distributed in a total of seven cuts of La = − 3, − 2, − 1, 0, 1, 2, 3, and the region between every two cuts corresponds to the level intervals and regions defined in Fig. 3. Where the voltage vector is not only at the boundaries of the cuts but also at the inner center of the cuts when La = 0, that is, the center of gravity of the cube.

From Fig. 5, it can be seen that the number of voltage vectors is large, and with the increase of the number of cascades, the voltage vectors will increase more, which makes it very difficult to choose the optimal vector for voltage balancing. To solve this problem, this paper simplifies the voltage vectors with the goal of strong voltage balancing capability and low switching losses, so that the computational difficulty and switching losses are greatly reduced, and it is easier to extend to more number of cascaded converters.

3.3.1 Strong voltage balancing capability

The voltage of the supercapacitor energy storage converters can be balanced by varying the charging and discharging speeds when the optimal voltage balancing effect is the goal. Modules with large voltages are charged less and discharged more, modules with small voltages are charged more and discharged less, and modules with faster charging and discharging speeds in a certain time have more power input or output. Therefore, the charging and discharging speed of the module can be controlled indirectly by controlling the power on the DC-side, which in turn changes the DC-side voltage of each module.

Assuming ideal conditions, the power on the AC-side of the i-th module of phase A of the converter is equal to the power on the DC-side of the module:

where Pai is the AC-side power of the i-th module of phase A, Pdcai is the DC-side power of the i-th module of phase A, φ is the power factor angle, and \(i = 1 \sim 3\).

From Eq. (7), it can be seen that the module DC-side and AC-side currents are equal, and the AC-side voltage Uaibi can be changed to balance the DC-side voltage Udcai of the module. Assuming that the R4 region is initially (0, 0, 0) at a certain point in time, since the output in the R4 region alternates between the 0 level and the Udc level, if the Udca1 voltage is to be increased at the next point in time, one of the three vectors (1, − 1, 1), (1, 0, 0), and (1, 1, − 1) on the AC-side can be selected for voltage balancing by selecting the Udc level. Therefore, among the many vectors of the seven levels, the vector with high-voltage balancing capability represents the most input or output power and the largest input or output voltage on the AC side. It can be made that m is the voltage balancing capability as in Eq. (8):

As La1 = Ua1b1/Udc, La2 = Ua2b2/Udc, La3 = Ua3b3/Udc, therefore:

where m is a nonzero integer.

The larger m represents the strong voltage balancing capability, while the redundant vector at level 0 can be eliminated in a seven-level energy storage converter, but the internal voltage vector at level 0 should be retained in order for the converter to operate properly.

3.3.2 Low switching losses

Reduced switching times should be considered to prevent module level leapfrog hopping when aiming for low switching losses. For example, when in the R4 region, a jump from level 0 (− 1, 0, 1) to level 1 (1, − 1, − 1) may occur; although the voltage balancing capability may be good, module 1 has undergone leapfrog hopping from a − Udc level change to a Udc level, and module 3 has undergone leapfrog hopping from a Udc level change to a − Udc level; And the three-module switching tubes will act at the same time, and the bridge arms need to be subjected to large voltage stress. Secondly, when the level of phase voltage changes, one of the three modules should be made to change the level of one of the modules, and the other two remain unchanged, to meet this requirement, can greatly reduce the switching losses. If the change from level 0 to Udc level is initially (0, 0, 0), the next moment may be one of (0, 0, 1), (1, 0, 0), (0,1, 0) rather than one of (1, − 1, 1), (1, 1, − 1), (− 1, 1, 1).

Therefore, in combination with the goal of strong voltage balancing capability and low switching losses, (0, − 1, 1), (1, − 1, 0), (1, 0, − 1), (0, 1, − 1), (− 1, 1, 0), (− 1, 0, 1) should be removed at level 0 and (0, 0, 0) should be retained; at Udc levels (− 1, 1, 1), (1, − 1, 1), (1, 1, − 1) should be removed; at − Udc levels (− 1, − 1, 1), (1, − 1, − 1), (− 1, 1, − 1) should be removed; ± 2Udc levels and ± 3Udc levels are all retained. The 27 vectors in phase A can then be simplified to 15 vectors with strong voltage balancing capability, reducing the number of vectors by 44.4%, as shown in Fig. 6.

From Fig. 6(a), it can be seen that when La changes from 0 to 1 and 2 to 3, both are only one of the three modules level changes, and the change is 1, and there is no leapfrog hopping. Similarly, when La changes from − 1 to 0 and -3 to − 2, no leapfrog hopping occurs. And when La changes from 1 to 2 and − 2 to − 1, as shown in Table 2, there are 2/3 occurrences of only one module level change out of three modules, and the change is 1 and there is no leapfrog hopping, as shown in the second and third columns of Table 2; and there are 1/3 occurrences of three-module level changes, but with smaller chances of occurring and the change is 1 and there is no leapfrog hopping, as shown in the fourth column of Table 2.

The optimization principle of the simplified vector algorithm by analysis is:

-

1)

It is necessary to keep the internal or boundary voltage vectors of the cut-outs for the system to function properly and to output the full level;

-

2)

Screen the vectors with strong voltage balancing ability by substituting the boundary vectors in the remaining cuts into Eq. (9);

-

3)

Prevent the module level leapfrog hopping, and when the level changes, one of the three modules should be made to change level and the other two should remain unchanged to reduce switching losses.

4 Inner-phase and mutual-phase DC-side voltage balancing control

4.1 Inner-phase DC-side voltage balancing control

According to Sect. 3.3, a total of 27 voltage vectors in phase A are simplified into 15 vectors with strong voltage balancing capability, and the DC-side voltage Udcai of the balancing module is carried out by changing the AC-side voltage Uaibi. However, there are three voltage vectors at the output AC-side voltage of ± Udc level and ± 2Udc level, and the redundant voltage vectors at the same level can be considered to have different effects on the DC-side voltage. Then, the vector with stronger voltage balancing ability is selected to be different according to the DC-side voltage magnitude and input current direction. The voltage vectors at different output levels affect the DC-side voltage as shown in Table 3, where “↓” indicates a voltage decrease, “↑” indicates a voltage increase, and “ + ” indicates that the A-phase input current ia is positive, and “−” indicates that the phase A input current ia is negative.

From Table 3, it can be obtained that there is only one vector at La = 0 and La = ± 3 after simplifying the vectors, and there is no need to make a selection, which reduces the burden on the system. At La = ± 1 and La = ± 2, the selection of the optimal vector is made according to the voltage magnitude and current direction. Take the R5 region as an example, the flowchart is shown in Fig. 7, when the A-phase output level La is located in the R5 region.

Firstly, the output Udc level and 2Udc level are determined by determining that it is located in the R5 region based on the reference vector; then, Ta1 and Ta2 are calculated and time allocation is performed, and the operating level is determined to be either the Udc level or the 2Udc level based on the TPWM generated by the time allocation, which can be assumed to be the following moments:

-

1)

The voltage vector is (1, 0, 0) when La = 1 i.e., output Udc level at moment t;

-

2)

If ia < 0 and Udca2 is minimal at moment t + 1, the output (1, 0, 1) at La = 2 will decrease Udca1 and Udca3 according to Table 3;

-

3)

If ia < 0 and Udca1 is maximal at moment t + 2, the output (1, 0, 0) at La = 1 will decrease Udca1 according to Table 3;

-

4)

If ia > 0 and Udca3 is maximum at moment t + 3, the output (1, 1, 0) at La = 2 will increase Udca1 and Udca2 according to Table 3.

It can be seen that the above moments are all three modules in which only one module level changes, and the change is 1, there is no leapfrog hopping, reducing the switching losses. And through the relationship between the current direction and the DC-side voltage magnitude, and then, select the voltage vector with strong voltage balancing ability, it can achieve fast voltage balancing. Secondly, the SVPWM algorithm with voltage balancing based on simplified vector reduces numerous redundant vectors and can be implemented with only a simple ordering and a few logic judgements. Hence, the burden on the system is small, the operation speed is fast, and it can be extended to H-bridge converters with much number of modules.

4.2 Mutual-phase DC-side voltage balancing control

The three-phase input voltage and current can be decomposed into positive-sequence, negative-sequence, and zero-sequence components according to the method of symmetrical components. The additional zero-sequence voltage does not affect the total output power of the system due to the star-arrangement of the system, and the zero sequence current is zero. Then, the additional power generated by injecting zero-sequence voltage can be used to change the power distribution between the three mutual phases, thus achieving mutual-phase voltage balancing.

In Fig. 1, the three-phase current of the energy storage converters can be made to be expressed as:

where I is the three-phase current RMS value, δi is the initial phase of the current.

Then, the additional fluctuating power in the three phases generated by the zero-sequence voltage is:

where Pa0, Pb0, and Pc0 are the three-phase additional fluctuation power generated by the zero-sequence voltage, U0 is the rms value of the zero-sequence voltage, and θ0 is the phase angle of the zero-sequence voltage.

Making the sum of the DC-side voltages of each module of the three-phase cascade of a, b, and c of the CHB energy storage converters as shown in Fig. 1 to be Udca, Udcb, and Udcc, respectively, the average values of the DC-side voltages of each module of each phase, Uava, Uavb, and Uavc, are:

The average value of the DC-side voltage Udcav of each module of the three phases is:

The deviation values of Uava, Uavb, Uavc, and Udcav are defined as ∆Udca, ∆Udcb, and ∆Udcc:

Equation (14) reflects the mutual-phase DC-side voltage of the CHB energy storage converters degree of imbalance.

As the DC-side voltage unbalance between the three phases ∆Udca, ∆Udcb, and ∆Udcc determines the size of the additional fluctuation power Pa0, Pb0, and Pc0 injected into each phase during mutual-phase voltage balancing. So, the degree of voltage unbalance is proportional to the additional fluctuation power injected into each phase, as in Eq. (15), with the proportionality coefficient k.

By associating Eqs. (11), (14), and (15), the RMS value of the injected zero-sequence voltage U0 and the phase angle θ0 required for mutual-phase balance can be found:

where λ is:

The ∆Udcα and ∆Udcβ in Eq. (17) indicate that Eq. (14) is converted from the abc three-phase stationary coordinate system to the αβ two-phase stationary coordinate system for the convenience of computation, as shown below:

Note that the larger the proportionality coefficient k, the larger the rms value of the zero-sequence voltage, and the larger its additional power, the more efficient the mutual-phase power balance of the energy storage converters will be. But, k must not be too large, it will affect the safe operation of the system due to too large will cause the system output voltage and current to produce large distortion.

The block diagram of mutual-phase DC-side voltage balancing control based on zero-sequence voltage injection method can be obtained from the above analysis, as shown in Fig. 8. It consists of two parts: system power control and zero-sequence voltage injection. The system power control has been introduced in Sect. 2.2, and its main function is to control the power of the storage converter to produce three-phase voltage modulated waves va*, vb*, and vc*. The zero-sequence voltage injection module obtains the required zero-sequence voltage RMS value U0 and the phase angle θ0 by calculating, and the injection of the zero-sequence voltage component U0 can change the power distribution among the three phases, making the mutual-phase DC-side voltage balancing. The three-phase modulating voltages va*, vb*, and vc* are superimposed with the zero-sequence voltage component U0 to obtain the final modulating wave voltages va*ʹ, vb*ʹ, and vc*ʹ.

5 Simulation and experimentation

5.1 Simulation analysis

The three-module CHB energy storage converter simulation model is built based on Matlab/Simulink for analysis, in order to verify the inner-phase voltage balancing of the SVPWM algorithm with voltage balancing based on simplified vectors, as well as the mutual-phase voltage balancing effect of the zero-sequence voltage injection method. Setting the initial supercapacitor voltage of each module in each phase during charging and discharging is not equal to verify the inner-phase balance, and setting the initial supercapacitor voltage between the three phases is not equal to verify the mutual-phase balance, the main simulation parameters are shown in Table 4.

5.1.1 Inner-phase voltage balancing

The waveforms of the A-phase grid-side voltage, current, and three-phase grid-side current for verifying the DC-side voltage balancing in inner-phase are shown in Fig. 9. It can be seen that in Fig. 9a, the voltage is in the same phase as the current when charging at a given power, which enables the storage of power, and in Fig. 9b, the voltage is 180º out of phase with the current when discharging, which enables the release of power. And the three-phase AC currents of charging and discharging are still symmetrical when the initial voltages of supercapacitors of each module are unequal, and the voltage balancing algorithm of the simplified vector will not affect the three-phase AC current output.

The DC-side voltage waveform of each module in abc three-phase using the SVPWM algorithm with voltage balancing based on simplified vector is shown in Fig. 10. It can be seen, taking phase A as an example, that the energy storage unit with a large initial value voltage during charging charges at the slowest rate, and the energy storage unit with a small initial value voltage charges at the fastest rate. At last, it charges at the same rate at 0.72 s with decreasing degree of imbalance. Then, the rate of discharge is reversed to that of charging, and the eventual balance is reached at 0.48 s. Although the initial values of the voltages of each energy storage unit in each phase are set to be different, the voltages can still be balanced in a short time, and the charging and discharging can be carried out at the same charging rate. This proves that the proposed inner-phase voltage balancing algorithm has a strong voltage balancing capability.

Figure 11 shows the comparative analysis of the DC-side voltage of each module in three phases during charging under inner-phase balance. From the figure, it can be seen that the three-phase DC-side voltage of the traditional method takes about 0.65 s, 0.64 s, and 0.585 s to reach balance from unbalance, respectively; and the three-phase DC-side voltage of the proposed method takes about 0.7 s, 0.685 s, and 0.635 s to reach balance from unbalance, respectively. Both the proposed method and the traditional method can reach balance in short time, and the voltage balance of the proposed method is a little slower than that of the traditional method (< 0.05 s).

Figure 12 shows the voltage waveforms of each module port in phase A during charging under converter voltage unbalance. It can be seen that there is leapfrog hopping in the levels of modules 1, 2, and 3 under the traditional 3D-SVPWM method in Fig. 12a, and there is also a simultaneous change in the levels of the three modules when the level of the A-phase output voltage ua changes. Since the vectors are not simplified, the module moves more frequently and the switching losses are higher. And because the initial supercapacitor voltages of modules 1, 2, and 3 are 60 V, 80 V, and 100 V, respectively, when setting up A-phase charging, module 1 needs to charge faster to get more power to maintain balance, followed by module 2 and finally module 3. Therefore, module 1 needs to have a high level to get more power and maintains the + 1 level when ia > 0 in Fig. 12a. However, there still exists a situation that all three module levels change at the same time when the level changes under the non-simplified vectors, such as at voltage amplifica-tion (1) and (2) in Fig. 12a.

The port voltage of each module in phase A under the proposed method is shown in Fig. 12b. It can be seen that there is no leapfrog hopping in each module when the ua level changes, presenting a step wave, and only one of the three modules has a change in level. It is indicated that the switching devices of each module of the converter under the SVPWM algorithm with voltage balancing based on simplified vector have fewer actions, low voltage stress, and small switching losses.

In addition, in order to further verify the advantages of the proposed method over the traditional method in terms of system switching loss, the average value of the number of switching actions for 3 cycles after 0.3 s is counted by simulation in Fig. 13, taking the converter A-phase as an example. It can be seen from the figure that although the number of switching actions in the first module A1 in phase A using the proposed method is slightly more than the traditional 3D-SVPWM with voltage balancing method. But, the number of switching actions in the other modules and the total number of switching actions in phase A is reduced by about 50% compared to the traditional method, which significantly reduces the switching losses.

According to the comparison between the traditional 3D-SVPWM algorithm with voltage balancing and the proposed algorithm in Table 5, it can be seen that the proposed algorithm has the following advantages over the traditional algorithm. First, the proposed algorithm reduces the number of voltage vectors used in a single phase by 44.4%, which makes the system less burdensome and easy to expand to more modules in cascade. Second, compared with the traditional algorithm, the proposed algorithm greatly reduces the switching losses; and the network side current THD is also smaller.

5.1.2 Mutual-phase voltage balancing

Figure 14 shows the analysis of three-phase DC-side voltage, injected zero-sequence voltage, three-phase grid-side current, and grid-side current THD under mutual-phase balance after adding inner-phase balance. It can be seen that the mutual-phase voltage balancing in Fig. 14a cannot be achieved when charging without injecting zero-sequence voltage and there is a deviation value. The mutual-phase balancing starts after the injection of the zero-sequence voltage at 1 s. As the zero-sequence voltage decreases, the degree of unbalance between the three mutual-phases decreases, and eventually charges at the same rate at 1.8 s. Figure 14b shows the mutual-phase balancing by injecting the zero-sequence voltage at 0.6 s during discharge, and the balancing is achieved at 1.4 s as the zero-sequence voltage decreases. Also, the mutual-phase cannot be balanced automatically when it is not injected. Moreover, the three-phase grid-side current does not change when the zero-sequence voltage is injected at 1 s and 0.6 s. It means that zero-sequence voltage injection does not affect the output of three-phase grid-side current, which verifies the feasibility and correctness of the zero-sequence voltage injection method. The grid-side currents are analyzed for THD after both inner-phase and mutual-phase are balanced. From the THD analysis of the grid-side currents in Fig. 14a and b, it can be seen that the grid-side current during charging: THD = 1.06%, and the grid-side current during discharging: THD = 0.91%, both of which are less than 2% and satisfy the national requirement of less than 5% of the grid entry.

5.2 HIL experimental verification

A hardware-in-the-loop (HIL) experimental platform as shown in Fig. 15 is built to further verify the feasibility of the simulation results. It mainly provides HIL experimental verification of the proposed SVPWM algorithm with voltage balancing based on simplified vector for inner-phase voltage balancing as well as the zero-sequence voltage injection method for mutual-phase voltage balancing. Among them, the main circuit is built in the Typhoon HIL402 platform, the HDSP-DF28335P controller is used to output pulses, and the harmonic distortion rate of the grid-side currents is analyzed by using the HIOKI power quality analyzer PQ3198. The main parameters of the HIL experiment are consistent with the simulation parameters in Table 4.

Figure 16 shows the HIL experimental waveforms of phase A under inner-phase balance, which shows that the voltage and current are in the same phase in Fig. 16a for charging, and the voltage and current are 180º out of phase in Fig. 16b for discharging. The experimental waveforms are consistent with the simulation results, and the storage and release of power are achieved. When charging, with the addition of SVPWM algorithm with voltage balancing based on simplified vector, it finally reaches balance at 0.8 s. When discharging, with the decrease of the degree of imbalance, it reaches balance at 0.5 s, and finally charging and discharging at the same rate, which verifies that the inner-phase voltage balancing algorithm proposed in this paper has a strong voltage balancing capability.

The HIL experimental waveforms of the port voltage and phase voltage of each module in phase A during charging under converter voltage unbalance are shown in Fig. 17. It can be seen that Fig. 17a under the traditional 3D-SVPWM method exists a situation in which the levels of the three modules change at the same time when the phase voltage ua level changes, and level leapfrog hopping occurs in all three modules. And under the simplified vector in Fig. 17b, each module did not show the level leapfrog hopping when the phase voltage ua level changes. In addition, the output voltage of only one module unit among three module units has one level change, which is the same as the simulation results, verifying that the proposed algorithm has small switching losses.

The average value of computing time for the proposed method and the traditional method calculated in the HIL platform is shown in Fig. 18. It can be seen from Fig. 18 that the algorithm computation time of the traditional method is 19.18 μs, which accounts for 27.4% of the control cycle, and the algorithm computation time of the proposed method is 13.51 μs, which accounts for 19.3% of the control cycle. The proposed method reduces 5.67 μs and enhances the operation speed by about 30% compared to the traditional method. This shows that the proposed simplified vectors algorithm can effectively reduce the computing burden of the controller and improve the response speed of the system.

Figure 19 shows the HIL experimental waveforms of mutual-phase voltage balancing without adding zero-sequence voltage injection and mutual-phase voltage balancing with adding zero-sequence voltage injection, as well as the THD analysis of the grid-side currents. The supercapacitor voltages of the first module in the three phases of A, B, and C are selected for the analysis because only four waveforms can be observed at one time by the TBS 2000X SERIES oscilloscope. It can be seen that in Fig. 19a charging without adding the mutual-phase balance of zero-sequence voltage injection, it does not reach the balance automatically, while with the addition of the mutual-phase balance, it reaches the balance at 1.3 s. In Fig. 19b, the discharging is consistent with the charging, and finally balance at 0.8 s. Then, the THD of the grid-side current is 1.69% and 1.87%, respectively, after charging and discharging balance, both are less than 2% and meet the national requirement of less than 5% for grid entry.

6 Conclusion

A SVPWM algorithm with voltage balancing based on simplified vector is proposed in this paper for the converter inner-phase voltage balancing with CHB energy storage converters as the research background, which overcomes the problems of larger number of voltage vectors and higher switching losses. Firstly, the algorithm carries out simplification of voltage vectors by targeting strong voltage balancing capability and low switching losses and simplifies a total of 27 voltage vectors to 15 vectors in a single phase of a conventional SVPWM with voltage balancing, which is a reduction of 44.4% of the vectors. It makes the algorithm simpler, the system burden smaller, and it is easier to extend to cascaded H-bridge converters with more modules. Besides, the algorithm prevents the occurrence of leapfrog hopping in the level of each module and makes only one level change in one module when the phase voltage level changes, which greatly reduces switching losses. Finally, the additional power generated by zero-sequence voltage injection is used to change the distribution of power among the three phases, thus changing the charging and discharging speeds of the three-phase energy storage units, so that the mutual-phase voltage is balanced. The THD of the charging and discharging grid-side currents meets the requirements for grid-connection after both inner-phase and mutual-phase voltages are balanced. It is verified by the simulation and experimental results that the proposed control algorithm is correct.

Data availability

The datasets used or analyzed during the current study are available from the corresponding author on reasonable request.

References

Li X, Wang S (2019) Energy management and operational control methods for grid battery energy storage systems[J]. CSEE J Power Energy Syst 7(5):1026–1040

Liu M, Cao X, Cao C et al (2022) A review of power conversion systems and design schemes of high-capacity battery energy storage systems[J]. IEEE Access 10:52030–52042

Liang G, Rodriguez E, Farivar GG et al (2022) A constrained intersubmodule state-of-charge balancing method for battery energy storage systems based on the cascaded H-bridge converter[J]. IEEE Trans Power Electron 37(10):12669–12678

Liu C, Gao N, Cai X et al (2019) Differentiation power control of modules in second-life battery energy storage system based on cascaded H-bridge converter[J]. IEEE Trans Power Electron 35(6):6609–6624

Krishan O, Suhag S (2020) A novel control strategy for a hybrid energy storage system in a grid-independent hybrid renewable energy system[J]. Int Trans Electr Energy Syst 30(4):e12262

Bi K, Sun L, An Q et al (2018) Active SOC balancing control strategy for modular multilevel super capacitor energy storage system[J]. IEEE Trans Power Electron 34(5):4981–4992

Yao Z, He X, Xiao Z et al (2024) Sensorless simultaneous self-balance mechanism of voltage and current based on Near-CRM in interleaved three-level DC-DC converter[J]. IEEE Trans Power Electron 39(2):2086–2099

Ling Z, Zhang Z, Li Z, et al. (2016) State-of-charge balancing control of battery energy storage system based on cascaded H-bridge multilevel inverter[C]//2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia). IEEE, 2310–2314

Moosavi M, Farivar G, Iman-Eini H et al (2013) A voltage balancing strategy with extended operating region for cascaded H-bridge converters[J]. IEEE Trans Power Electron 29(9):5044–5053

Ghias AMYM, Pou J, Ciobotaru M et al (2014) Voltage-balancing method using phase-shifted PWM for the flying capacitor multilevel converter[J]. IEEE Trans Power Electron 29(9):4521–4531

Zhao T, Wang G, Bhattacharya S et al (2012) Voltage and power balance control for a cascaded H-bridge converter-based solid-state transformer[J]. IEEE Trans Power Electron 28(4):1523–1532

Lewicki A, Odeh C, Morawiec M (2023) SVPWM strategy for multilevel cascaded H-bridge inverter with DC-link voltage balancing ability[J]. IEEE Trans Industr Electron 70(2):1161–1170

Fan X, Zhao R, He J et al (2023) Hybrid SVPWM strategy of cascade H-bridge multilevel converter for battery energy storage system[J]. IEEE Trans Power Electron 39(1):626–635

Wu X, Xiong C, Yang S, Yang H, Feng X (2019) A simplified space vector pulsewidth modulation scheme for three-phase cascaded H-bridge inverters[J]. IEEE Trans Power Electron 35(4):4192–4204

Gupta AK, Khambadkone AM (2007) A general space vector PWM algorithm for multilevel inverters, including operation in overmodulation range[J]. IEEE Trans Power Electron 22(2):517–526

Shu Z, Ding N, Chen J et al (2012) Multilevel SVPWM with DC-link capacitor voltage balancing control for diode-clamped multilevel converter based STATCOM[J]. IEEE Trans Industr Electron 60(5):1884–1896

Liu Z, Wang Y, Tan G et al (2015) A novel SVPWM algorithm for five-level active neutral-point-clamped converter[J]. IEEE Trans Power Electron 31(5):3859–3866

Leon JI, Portillo R, Vazquez S et al (2008) Simple unified approach to develop a time-domain modulation strategy for single-phase multilevel converters[J]. IEEE Trans Industr Electron 55(9):3239–3248

Leon JI, Vazquez S, Portillo R, et al. (2010) Two-dimensional modulation technique with dc voltage control for single-phase two-cell cascaded converters[C]//2010 IEEE International Conference on Industrial Technology. IEEE, 1365–1370

She X, Huang AQ, Wang G (2011) 3-D space modulation with voltage balancing capability for a cascaded seven-level converter in a solid-state transformer[J]. IEEE Trans Power Electron 26(12):3778–3789

Zhang M, Atkinson DJ, Ji B et al (2014) A near-state three-dimensional space vector modulation for a three-phase four-leg voltage source inverter[J]. IEEE Trans Power Electron 29(11):5715–5726

Lin H, Shu Z, Yao J et al (2019) A simplified 3-D NLM-based SVPWM technique with voltage-balancing capability for 3LNPC cascaded multilevel converter[J]. IEEE Trans Power Electron 35(4):3506–3518

Zhong W, Gong J, Pan S et al (2022) An improved Negative-sequence current compensation method for star-connected CHB STATCOM[J]. IEEE Trans Power Deliv 37(6):4786–4795

Mao W, Zhang X, Zhao T et al (2019) Research on power equalization of three-phase cascaded h-bridge photovoltaic inverter based on the combination of hybrid modulation strategy and zero-sequence injection methods[J]. IEEE Trans Industr Electron 67(11):9337–9347

Funding

This work was supported in part by the National Natural Science Foundation of China under Grant 51907083 and in part by the Basic Research Project of Xuzhou under Grant KC23024.

Author information

Authors and Affiliations

Contributions

ZL wrote the main manuscript text; DR wrote the section of simulation; and JC, KZ, YY, and FW wrote the section of experiment jointly.

Corresponding author

Ethics declarations

Conflict of interest

The authors declared no potential conflicts of interest with respect to the research.

Ethical approval

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Liu, Z., Ren, D., Chen, J. et al. Study of SVPWM control algorithm with voltage balancing based on simplified vector for cascaded H-bridge energy storage converters. Electr Eng (2024). https://doi.org/10.1007/s00202-024-02595-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00202-024-02595-2