Abstract

The conventional approach of predictive torque control (PTC) is frequently employed in the control of permanent magnet synchronous motors (PMSMs) driven by a two-level voltage source inverter (2L-VSI). This technique offers low complexity and reduced torque ripples in the low-speed region by minimizing the duty-cycle of the applied voltage vector (VV) compared to the complete utilization of the DC-link voltage. However, it has its limitations, including slow torque dynamics, restricted modulation index (MI), and an inability to select zero VV, which would be useful for minimizing ripples in multilevel VSI drives. Additionally, it can lead to an unbalanced DC link due to the restricted VV selection, especially at low MI. To address these limitations, a modified PTC based on space vector pulse-width modulation approach is proposed for three-level neutral-point-clamped (3L-NPC) VSI-fed PMSM. The proposed 3L-PTC method can reduce torque and flux ripples at low MI, improve dynamic response, and maintain a balanced DC link regardless of operating conditions. Intensive numerical and experimental evaluations are carried out to validate the effectiveness of the proposed 3L-PTC.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Over the past few years, there has been an increasing focus on the application of predictive torque control (PTC) to improve the performance of AC machines and effectively regulate their torque, particularly in the case of permanent magnet synchronous motors (PMSMs) [1,2,3,4,5,6,7,8]. PTC has gained popularity as an attractive choice due to its inherent simplicity, ability to optimize various factors using a unified cost function, and straightforward integration into real-time systems.

PTC can be primarily categorized into two main groups: finite-control-set (FCS) PTCs, as referenced in [1, 9,10,11], and continuous-control-set (CCS) PTCs, as discussed in [4, 12,13,14,15,16,17]. FCS-PTC operates in a manner akin to conventional direct torque control (DTC), where a limited set of preferred control actions are evaluated according to their specific goals. In such cases, the output is in a discrete form and is directly applied to control the switching components of the voltage source inverter (VSI). Nevertheless, FCS-PTC shares a significant drawback with DTC; that is, it only applies a single voltage vector (VV) within each control period (Ts), leading to substantial torque and flux fluctuations [18,19,20].

On the other hand, CCS-PTC relies on pulse-width modulation (PWM) to generate the switching patterns for the VSI. This approach ensures a consistent switching frequency, offering a notable advantage over FCS-PTC. Recent studies have brought about improvements in CCS-PTC, with the goal of reducing variations in torque and flux in PMSM drives [12,13,14,15]. Through an examination of the relationship between the applied VV and electromagnetic torque, an improved version of classical CCS-PTC has been introduced to enhance the performance of PMSMs powered by a two-level voltage source inverter (2L-VSI) [12]. Nevertheless, the classical CCS-PTC still grapples with significant torque and flux fluctuations due to the limitations of the applied VV, potentially leading to unstable PMSM operation in high-speed conditions [4].

Improvements in CCS-PTC can be realized by integrating multilevel inverters (MLIs) into PMSM drive setups, as detailed in [21,22,23]. Among these MLIs, the most widely recognized is the three-level neutral-point-clamped (3L-NPC) VSI, as shown in Fig. 1. However, maintaining balance in the neutral point (NP) is necessary to optimize the performance of PMSMs driven by the 3L-NPC VSI [24]. Deviations in the DC-link voltage can lead to NP voltage imbalances, potentially causing premature failures of switching components and an increase in total harmonic distortion (THD) in the output current and voltage [24, 25]. Additionally, the traditional PTC method suffers from significant torque and flux fluctuations due to limitations in applied VVs, resulting in subpar performance in both steady-state and transient operations.

Numerous space vector modulation (SVM) approaches have been documented in the literature, with the aim of reducing DC-link voltage fluctuations [26,27,28,29]. However, these techniques entail complex calculations, necessitate knowledge of the NP current, and often result in high THD in output phase currents, along with noticeable torque and flux variations. In a previous study [16], a novel NP balancing algorithm was introduced for three-level predictive torque control (3L-PTC). This algorithm employs space vector pulse-width modulation (SVPWM) techniques to adjust the duty cycles of reference three-phase pole voltages based on DC-link voltage deviations. Notably, this proposed NP balancing algorithm is straightforward, as it only requires information regarding the upper and lower capacitor voltages of the 3L-NPC VSI. It estimates new modulation reference signals based on the NP deviation status. This extended research paper provides further elaboration on the theoretical concepts of 2L-VSI and 3L-NPC VSI, along with an in-depth analysis of the improved steady-state and transient-state performance of the proposed 3L-PTC method. Extensive simulation and experimental results are presented to validate the efficacy of the proposed 3L-PTC approach.

The rest of the paper is organized as follows. Section 2 provides a mathematical modeling of PMSM and a brief comparison of 2L- and 3L-NPC VSIs. Section 3 presents an overview of the PTC and the limitations of employing the conventional PTC in 3L-NPC VSI PMSM drives. Section 4 extensively illustrates the proposed PTC with DC-link balancing and its effectiveness in improving both steady- and transient-state operations. Sections 5 and 6 discuss the various simulation and experimental results, respectively. Finally, Section 7 presents the conclusions of this paper.

2 System description

In this section, the modeling of PMSM is provided to understand the relationship between torque, flux, and applied VV. It is also important to highlight the differences of 2L- and 3L-NPC VSIs in terms of their physical model and their applicable VVs to investigate the limitation of the conventional PTC for 3L-NPC PMSM drives.

2.1 Modeling of PMSM

To analyze the performance and control of the PMSM, it is important to model it in different reference frames (i.e., stationary reference frame [α–β], rotating reference frame [d–q], and synchronous rotating reference frame [f–t]), as shown in Fig. 2. Hence, one of the most effective methods for mathematically representing the PMSM is through the voltage model. This model articulates the relationship between stator voltage vs, current is, and flux ψs, as outlined in (1):

where ψs can be expressed as a function of is and rotor flux ψr as expressed in (2):

where R and L represent the stator resistance and inductance, respectively. The electromagnetic torque (Te) of the PMSM can be calculated using the cross product of ψs with is consideration of its pole pair (pn) as in (3):

2.2 Two-level VSI

The standard circuit topology of a 2L-VSI consists of two switches in each phase leg, as shown in Fig. 3a. For example, the upper and lower switching in a-phase are Sa1 and Sa2, respectively. These switching devices are typically controlled using PWM technique with the help of seven VVs (i.e., six large VVs VL1–VL6 and one zero VV Vz). These VVs can be represented by the switching state P or N for each phase, as shown in Fig. 3a. The type of switching devices used are insulated-gate bipolar transistors (IGBTs). The 2L-VSI produces an output voltage waveform that approximates a square wave, with only two voltage levels, + Vdc/2 and – Vdc/2. As the output waveform is not sinusoidal, it requires filtering to reduce the THD. The advantage of the two-level VSI is its simplicity and low cost, but it has a high harmonic distortion in the output waveform.

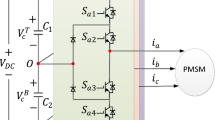

2.3 Three-level NPC VSI

The circuit topology of a 3L-NPC VSI is more complex than the 2L-VSI, as shown in Fig. 3b. It consists of four switches in each phase leg (Sa1, Sa2, Sa3, and Sa4), typically controlled using the PWM technique with more complexity than the control of the 2L-VSI. There are nineteen VVs (i.e., six large VVs VL1–VL6, six medium VVs VM1–VM6, six small VVs VS1–VS6, and one zero VV Vz). These VVs can be represented by the switching state P, O, or N for each phase, as shown in Fig. 3b. The type of switching devices used are IGBTs, which can produce an output voltage waveform with three voltage levels, + Vdc/2, 0, and – Vdc/2. The zero-voltage level is created by connecting the NP of the DC-link capacitors to the midpoint of the load (O). This results in a better approximation of a sinusoidal waveform and lower THD compared to the 2L-VSI. This is particularly important in applications where low harmonic distortion is required, such as in motor control or grid-connected applications. However, the 3L-NPC VSI is more expensive and complex to control, especially its neutral-point voltage balancing, where these drawbacks are absent in 2L-VSI systems.

3 PTC fundamentals for PMSM drives

To better understand the main concept of the PTC for PMSM drives, it is important to illustrate the relationship between Te slope and vs, as well as the increment or decrement of ψs with respect to vs.

3.1 Relationship between T e slope and v s

To examine the slope of Te, it is crucial to calculate the variation in Te over each Ts, as indicated in (4):

As depicted in (4), the Te rate of change is governed by the cross product of the rate of change of ψs and is, as well as the rate of change of is and ψs. Consequently, (1) and (2) can be reformulated as shown in (5) and (6), respectively:

Through the substitution of (5) and (6) into (4), it becomes possible to estimate the Te slope as shown in (7):

With knowledge of is, ψs, and ψr, it becomes feasible to regulate Te toward a desired value by controlling vs.

3.2 Relationship between ψ s and v s

As shown in Fig. 4, to examine the relationship between ψs and vs, the first section on the right-hand side of (7) must be reconfigured. This rearrangement leads us to (8):

By substituting (8) into (7), we have a more simplified equation for estimating the Te slope, as expressed in (9):

In (9), the calculation of ΔTe is notably more straightforward compared to that in (7). When provided with the magnitude of vs, it is possible to deduce the voltage control angle θv, as outlined in (10):

Utilizing the angle θv to regulate the direction of vs can prove to be highly effective in minimizing ΔTe. Moreover, the angle π − θv can be employed to reduce the magnitude of ψs.

3.3 Drawbacks of implementing conventional PTC using 3L-NPC VSI for PMSM drives

As mentioned in the previous section, 3L-NPC VSI outperforms 2L-VSI due to the increased degree of freedom in selecting more VV and their corresponding switching states, which contribute to ripple reduction particularly when the PMSM is operating at low speeds. However, the restriction of applied VV magnitude caused by the conventional PTC results in large ψs and Te ripples, as the relationship between the applied VV and ψs can be derived from (5) as in (11):

When utilizing the conventional PTC for 3L-NPC VSI-fed PMSM, VL and VM are responsible for Te increment, while VS are used for Te decrement. However, due to the absence of the Vz, large torque and flux ripples are present in the low-speed region. This is due to the restriction of applied VV magnitude (Vm) to 70% of the maximum allowable vs. Furthermore, the conventional PTC cannot operate in high-speed regions unless an extra Vdc is injected. The Te dynamic is also slower compared to the case if the maximum allowable vs is applied. Finally, NP balancing can be a challenging task due to this limitation.

4 Proposed PTC With DC-link balancing

In this section, a detailed explanation of the proposed PTC method is provided, with a primary emphasis on achieving balanced DC-link voltage in the 3L-NPC VSI. This enhancement aims to improve the performance of the PMSM in both steady-state and transient operating conditions. A schematic control diagram illustrating the proposed PTC-based SVPWM for PMSM driven by a 3L-NPC VSI is given in Fig. 5. The figure reveals that the DC-link balancing algorithm modifies the reference voltages for the SVPWM without any dwelling time calculation of VVs. Therefore, the proposed scheme is considered a simple approach for maintaining excellent performance of the PMSM under a balanced DC-link.

4.1 Torque ripple reduction and fast dynamics

As outlined in the preceding section regarding the limitation of the conventional PTC, which is summarized in (11), the proposed PTC does not apply any restriction on Vm. Alternatively, it utilizes all types of VVs available in the space vector diagram of 3L-NPC VSI (Fig. 3b). This concept is originated from the principle of DTC, which controls AC motors using VS and Vz in the low-speed regions and other VV types in medium- and high-speed regions. Therefore, the proposed PTC adjusts Vm according to the operating condition of the PMSM, as expressed in (12):

From (12), it can be summarized that half Vm is used in the low-speed region to maintain minimized torque and flux ripples, while the full Vm is essential for keeping the PMSM rotating in a stable condition during medium- and high-speed regions. In addition, the full Vm can be useful for improving the dynamic performance of the PMSM during transient-state operation.

4.2 SVPWM and DC-link balancing

Numerous modulation approaches based on SVM have been introduced to tackle the fluctuations in the DC-link voltage. While these algorithms achieve balanced DC-link capacitor voltages, they often require extensive computation of dwelling times’ applied VVs, increasing system complexity and resulting in increased Te ripples. To mitigate these drawbacks, a simple yet effective DC-link balancing algorithm is proposed for 3L-NPC VSI-fed PMSM. The main advantage of the proposed algorithm is that it is based on SVPWM, which is flexible and does not require calculation for dwelling time for each applied VV. It also maintains a constant switching frequency due to the help of a PWM carrier. As a result, system performance can be improved with minimized ripples and reduced THD.

In Fig. 6, we have a depiction of the a-phase reference voltage (v*as), offset voltage (vsn), and pole voltage (v*an) utilizing the SVPWM approach. The figure illustrates that vsn switches the line frequency of v*as three times. To compute v*as, it is necessary to express vs from the PTC block in a polar form relative to the PMSM rotor position, as described in (13):

where v*abcs represents the three-phase reference voltages.

Subsequently, the inclusion of vsn into the system becomes necessary to enhance the modulation index (MI), thereby enhancing the PMSM’s performance at high-speed operations and diminishing the THD in the output waveforms [30]. Note that vsn can be computed by taking into account the maximum and minimum values of v*abc, as given in (14):

After adding vsn to v*abcs, v*abcn can be obtained as in (15):

For simplification, v*abcn should undergo a normalization process and be expressed in relation to the reference modulation signals T*abc, as specified in (16):

To equalize the DC-link voltages, T*abc should be modified into T*abc(mod) in accordance with the difference between C1 and C2 voltages vC1 and vC2, respectively, as shown in the flowchart for the DC-link balancing algorithm depicted in Fig. 7.

Considering a microcontroller, a PWM carrier is designed as a counter with a peak value (Cp) based on the switching frequency. Therefore, T*abc(mod) needs to be divided into dual reference signals T*abc(mod)1 and T*abc(mod)2 in order to reduce the complexity of generating the PWM switching signals for the 3L-NPC VSI by reducing the required PWM carriers from dual to single PWM carrier (Carr.) [24]. T*abc(mod)1 and T*abc(mod)2 are generated as expressed in (17):

Finally the switching signals are generated by comparing T*abc(mod)1 and T*abc(mod)2 with Carr., as shown in (18):

Note that Sabc1 and Sabc3 are turning ON and OFF in a complementary manner with Sabc2 and Sabc4, respectively.

5 Simulation verification

Simulation trials are conducted using the PSIM tool developed by Powersim to assess how the proposed 3L-PTC performs in comparison to the conventional PTC using 2L-VSI (2L-PTC), conventional PTC using 3L-VSI without DC-link balancing algorithm (3L-PTC1), and conventional PTC using 3L-VSI with proposed DC-link balancing algorithm (3L-PTC2) [16]. The PMSM specifications are summarized in Table 1. The applied DC-link voltage is set at 300 V with correspondence to the base speed of 875 rpm. Ts is set as 100 µs to ensure proper execution of all functions, and the switching frequency is set as 10 kHz. These simulation results are provided to test the low-speed region with large torque step from 2 to 10 N m, as shown in Fig. 8. The figure reveals that there is no issue associated with the DC link in 2L-PTC. However when 3L-PTC1 is implemented, a large deviation occurs in the DC link due to the restriction of selecting the VVs. To mitigate this outcome, the DC-link balancing algorithm is implemented in 3L-PTC2. As a result, vdc_err. is almost zero even during torque transient. Nevertheless, ψs, Te, and ia have large ripples. Therefore, the proposed 3L-PTC maintains almost zero vdc_err. with minimized ripples in ψs, Te, and ia. This is due to the merits in maintaining minimized torque and flux ripples during steady-state operation and fast dynamic response. The mechanism of the proposed 3L-PTC method is by controlling the Vm according to the desirable operated conditions. Compared to 3L-PTC2, the proposed 3L-PTC has reduced torque and flux ripples from 0.93 to 0.79 N m and from 0.025 to 0.013 Wb, respectively.

Comparative simulation evaluation during torque dynamics from 2 to 10 N m at 300 rpm: a 2L-PTC; b 3L-PTC1; c 3L-PTC2 [16]; d proposed 3L-PTC

The major DC-link deviation caused by the 3L-PTC1 is a serious problem for reliability of DC-link capacitors of the 3L-NPC VSI and for PMSM performance. Therefore, a DC-link balancing is essential to maintain a reliable and robust performance of PMSM, as achieved by 3L-PTC2 and the proposed 3L-PTC.

A summary of a comparative simulation evaluation is presented in Table 2. The table shows the torque ripple (Te ripple), flux ripple (ψs ripple), and phase current THD (ia THD) of the four PTC methods during torque transient from 2 to 10 N m at 300 rpm. These results show that the proposed 3L-PTC has the smallest Te ripple and ψs ripple, lowest ia THD, and quickest torque dynamics.

6 Experimental validation

To assess and evaluate the performance of PMSM under four PTC methods, a hardware experimental setup is realized, as shown in Fig. 9. This experimental setup consists of a 5 kW PMSM, which is mechanically coupled with an IM acting as mechanical load. A single microcontroller (DSP TMS320F28335) from Texas Instruments is utilized to execute the control algorithm, including PTC methods. A PC is used to control the system by using Code Composer Studio software. The experimental results are captured with the help of an oscilloscope. Finally, 2L-VSI and 3L-NPC VSI are employed to conduct a fair evaluation.

To verify the effectiveness of the proposed 3L-PTC method in balancing the DC-link voltages, a new experimental result is conducted as shown in Fig. 10. The figure reveals that the proposed balancing algorithm is effective in such critical case when the PMSM is operating in the low-speed region of 300 rpm with light torque load of 2 N m. The vdc_err is minimized due to the modifications of T*abc, as indicated in the flowchart in Fig. 7. The proposed method clearly maintains a small torque and flux ripples in addition to balanced voltages of the DC link.

There are two experimental environments to test the operation of the PMSM under PTC methods. The first one is conducting a constant speed operation at 300 rpm with a large step change in Te from 2 to 10 N m, as shown in Fig. 11. It is shown that 2L-PTC has the fastest torque dynamics with 0.9 ms. This is because of the environment of 2L-VSI, which utilizes VVs that have the same magnitude as large VVs in the 3L-NPC VSI. Nevertheless, Te ripple and ψs ripple are the largest, as shown in Fig. 11a. On the other hand, the 3L-PTC methods, including the proposed one, have better performance compared to 2L-PTC in terms of Te ripple and ψs ripple. However, the 3L-PTC1 has a serious impact on the DC link, where the vdc_err. deviates widely. The proposed 3L-PTC offers the best performance among the four techniques, with the smallest Te ripple and ψs ripple and fast dynamics owing to its simple yet robust control.

Comparative experimental evaluation during torque dynamics from 2 to 10 N m at 300 rpm: a 2L-PTC; b 3L-PTC1; c 3L-PTC2 [16]; d proposed 3L-PTC

The second set of experimental validation is during speed variation from 50 to 875 rpm, as shown in Fig. 12 and its magnified version in Fig. 13. During this critical experimental environment, which may lead to the failure of the DC-link capacitors, the 3L-PTC1 method is excluded. Therefore, this test aims to assess the robustness of the DC-link balancing algorithm during speed variation. Among the three PTC methods, the proposed 3L-PTC offers almost zero steady-state vdc_err. in the low-speed region and minimum during speed and torque transient. In addition, Te ripple and ia THD are substantially improved.

Comparative experimental evaluation during speed transient from 50 to 875 rpm: a 2L-PTC; b 3L-PTC2 [16]; c proposed 3L-PTC

Magnified comparative experimental evaluation during speed transient from 50 to 875 rpm: a 2L-PTC; b 3L-PTC2 [16]; c proposed 3L-PTC

Finally, a comparative summary of the experimental results is presented in Table 3. The table shows the Te ripple, ψs ripple, and ia THD of the four PTC methods during torque dynamics from 2 to 10 Nm at 300 rpm. These data show that the proposed 3L-PTC has the smallest Te ripple and ψs ripple and lowest ia THD with very quick torque dynamics. As a result, the proposed 3L-PTC could be among the best alternatives for PMSM drives.

7 Conclusion

Based on theoretical, numerical, and experimental evaluations, the proposed 3L-PTC method is found to be a superior solution for controlling PMSMs compared to the 2L-PTC and other 3L-PTC techniques analyzed in this paper. The proposed 3L-PTC method offers a multitude of benefits, such as reduced torque and flux ripples, improved dynamic response, and a well-balanced DC link, irrespective of operating conditions. Simulation results have shown that the proposed method outperforms the other tested methods in terms of torque ripples, flux ripples, and phase current THD and has faster torque dynamics. Experimental results likewise confirm the effectiveness of the proposed method, with its quick torque dynamics, reduced torque and flux ripples, and a balanced DC link even during critical operating conditions. Therefore, the proposed 3L-PTC method is highly recommended for various industrial applications for maintaining reliable and high-performance PMSM drives.

References

Habibullah, M., Lu, D.D.C., Xiao, D., Rahman, M.F.: Finite-state predictive torque control of induction motor supplied from a three-level NPC voltage source inverter. IEEE Trans. Power Electron. 32(1), 479–489 (2017)

Liu, G., Farahat, A., Chen, Q., Zhang, J., Wang, X.: Sensorless control for five-phase PMSMs under normal and open-circuit fault conditions using super-twisting sliding mode observers. J. Power Electron. 23, 1098–1110 (2023)

Al-kaf, H.A.G., Hakami, S.S., Lee, K.-B.: Hybrid current controller for permanent-magnet synchronous motors using robust switching techniques. IEEE Trans. Power Electron. 38(3), 3711–3724 (2023)

Hakami, S.S., Lee, K.-B.: Enhanced predictive torque control for three-level NPC inverter-fed PMSM drives based on optimal voltage magnitude control method. IEEE Trans. Power Electron. 38(3), 3725–3738 (2023)

Foo, G.H.B., Ngo, T., Zhang, X., Rahman, M.F.: SVM direct torque and flux control of three-level simplified neutral point clamped inverter fed interior PM synchronous motor drives. IEEE/ASME Trans. Mechatron.Mechatron. 24(3), 1376–1385 (2019)

Vafaie, M.H., Dehkordi, B.M., Moallem, P., Kiyoumarsi, A.: A new predictive direct torque control method for improving both steady-state and transient-state operations of the PMSM. IEEE Trans. Power Electron. 31(5), 3738–3753 (2016)

Zhang, X., Wang, Z., Yang, G.: Fast position predictive control with current and speed limits for permanent magnet motor systems without weight coefficients. J. Power Electron. 23, 625–636 (2023)

Mohammed, S.A.Q., Lee, K.-B.: Improved adaptive iterative learning current control approach for IPMSM drives. J. Power Electron. 23, 284–295 (2023)

Sun, D., Su, J., Sun, C., Nian, H.: A simplified MPFC with capacitor voltage offset suppression for the four-switch three-phase inverter-fed PMSM drive. IEEE Trans. Ind. Electron. 66(10), 7633–7642 (2019)

Yan, L., Wang, F., Tao, P., Zuo, K.: Robust predictive torque control of permanent magnet synchronous machine using discrete hybrid prediction model. IEEE Trans. Energy Convers. 35(4), 2240–2248 (2020)

Agoro, S.A., Husain, I.: Robust deadbeat finite-set predictive current control with torque oscillation and noise reduction for PMSM drives. IEEE Trans. Ind. Appl. 58(1), 365–374 (2022)

Zhu, H., Xiao, X., Li, Y.: Torque ripple reduction of the torque predictive control scheme for permanent-magnet synchronous motors. IEEE Trans. Ind. Electron. 59(2), 871–877 (2012)

Cho, Y., Lee, K.-B., Song, J.-H., Lee, Y.I.: Torque-ripple minimization and fast dynamic scheme for torque predictive control of permanent-magnet synchronous motors. IEEE Trans. Power Electron. 30(4), 2182–2190 (2015)

Vafaie, M.H.: Performance improvement of permanent-magnet synchronous motor through a new online predictive controller. IEEE Trans. Energy Convers. 34(4), 2258–2266 (2019)

Adase, L.A., Alsofyani, I.M., Lee, K.-B.: Predictive torque control with simple duty-ratio regulator of PMSM for minimizing torque and flux ripples. IEEE Access 8, 2373–2381 (2020)

Hakami, S.S., Lee, K.-B.: Modified predictive torque control for balancing three-level NPC inverter-fed permanent magnet synchronous motor. In: Proceedings of International Power Electronics Conference (IPEC-Himeji 2022-ECCE Asia), pp. 854–858 (2022)

Wang, A., Zhang, H., Jiang, J., Jin, D., Zhu, S.: Predictive direct torque control of permanent magnet synchronous motors using deadbeat torque and flux control. J. Power Electron. 23, 264–273 (2023)

Hakami, S.S., Lee, K.-B.: Four-level hysteresis-based DTC for torque capability improvement of IPMSM fed by three-level NPC inverter. Electronics 9(10), 1558 (2020)

Hakami, S.S., Alsofyani, I.M., Lee, K.-B.: Torque ripple reduction and flux-droop minimization of DTC with improved interleaving CSFTC of IM fed by three-level NPC inverter. IEEE Access 7, 184266–184275 (2019)

Mohan, D., Zhang, X., Foo, G.H.B.: Generalized DTC strategy for multilevel inverter fed IPMSMs with constant inverter switching frequency and reduced torque ripples. IEEE Trans. Energy Convers. 32(3), 1031–1041 (2017)

Xu, S., Sun, Z., Yao, C., Zhang, H., Hua, W., Ma, G.: Model predictive control with constant switching frequency for three-level T-type inverter fed PMSM drives. IEEE Trans. Ind. Electron. 69(9), 8839–8850 (2022)

Kakosimos, P., Abu-Rub, H.: Predictive speed control with short prediction horizon for permanent magnet synchronous motor drives. IEEE Trans. Power Electron. 33(3), 2740–2750 (2018)

Teng, Q., Xu, R., Han, X.: Integral sliding mode-based model predictive current control with low computational amount for three-level neutral-point-clamped inverter-fed PMSM drives. IEEE Trans. Energy Convers. 35(4), 2249–2260 (2020)

Lee, K.-B., Lee, J.-S.: Reliability Improvement Technology for Power Converters. Springer, Singapore (2017)

Hwang, J.-H., Halabi, L.M., Ko, Y.J., Lee, K.-B.: Lifetime-based fault tolerant strategy for three-level hybrid ANPC inverters. J. Power Electron. 23, 363–373 (2023)

Jing, M., Xing, X., Li, X., Zhang, R., Jiang, Y., Zhang, C.: Virtual vector based model predictive control for three-level sparse neutral point clamped inverter. In: Proceedings of IEEE International Conference on Predictive Control of Electrical Drives and Power Electronics (PRECEDE), pp. 41–45 (2021)

Wang, F., Li, Z., Liu, Z.: Model predictive control methods for three-level sparse neutral point clamped inverter. IEEE J. Emerg. Sel. Top. Power Electron. 8(4), 4355–4366 (2020)

Zhang, X., Foo, G.H.B., Jiao, T., Ngo, T., Lee, C.H.T.: A simplified deadbeat based predictive torque control for three-level simplified neutral point clamped inverter fed IPMSM drives using SVM. IEEE Trans. Energy Convers. 34(4), 1906–1916 (2019)

Salem, A., Mamdouh, M., Abido, M.A.: Predictive torque control and capacitor balancing of a SiC-based dual T-type drive system. IEEE Trans. Power Electron. 35(3), 2871–2881 (2019)

Kim, S.-H.: Electric Motor Control: DC, AC, and BLDC Motors. Elsevier, Amsterdam (2017)

Acknowledgements

This work was supported in part by the Korea Institute of Energy Technology Evaluation and Planning (KETEP) and the Ministry of Trade, Industry and Energy (MOTIE) of the Republic of Korea under Grant 20206910100160 and Grant 20225500000110, respectively.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Hakami, S.S., Lee, KB. Modified predictive torque control for balancing three-level NPC inverter-fed PMSM drives. J. Power Electron. 24, 586–597 (2024). https://doi.org/10.1007/s43236-023-00763-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s43236-023-00763-4