Abstract

Quantum-dot cellular automata (QCA) technology is a kind of nanotechnology utilized for building computational circuits. It can be a good technology for overcome CMOS drawbacks at nano-scale due to its low delay and area. The Content-Addressable Memory (CAM) is a very fast memory that can perform search operations in a very short time. This feature makes the relative popularity of these memories and many applications for them, especially in network routing and processors. In this study, a novel loop-based circuit is designed for the QCA memory unit, which reduces area, cell count, latency, and cost. The obtained results using QCADesigner tool version 2.0.3 demonstrate that the designed QCA memory unit utilizes 16 cells, 0.01 µm2 area, and 0.25 clock cycles and has a reduction of 33% in the number of cells, 50% in area, 50% in latency, and 75% in cost compared to existing works. Then, this memory unit is utilized to design an efficient structure for CAM circuit. The results show that the developed structure for CAM circuit has 0.75 clock cycles, 32 cells, and 0.03 µm2 area, and it has a reduction of 20% in the number of cells, 25% in area, 40% in latency, and 75% in cost compared to existing works.

Article Highlights

-

An efficient Content-Addressable Memory (CAM) circuit is designed using a novel QCA memory unit.

-

The proposed QCA memory unit and CAM circuit have reduced cell count, area, latency, and cost.

-

The QCADesigner tool version 2.0.3 is utilized to evaluate the developed circuits.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The CMOS technology is a dominate technology for digital circuits design, but this technology has several concerns at nano-scale including short channel effects. The Quantum-dot Cellular Automata (QCA) technology is a significant kind of nanotechnology for the implementation of digital circuits such as full adder, comparator, shift register, counter, multiplier, and memory [1,2,3,4,5,6,7,8]. This kind of nanotechnology has significantly low delay and area compared to CMOS technology [3, 9]. So, it can significantly improve the design performance of logical circuits. The fundamental element in the QCA technology is named cell that is composed of two electrons and four dots. The electrons of each cell can move across the dots. Thus, there are two stable states in each cell based on coulombic repulsion. These stable states are equal to logics “0” and “1” in digital circuits [1, 10, 11].

One of the most important elements in digital circuits design is memory [12]. There are two well-known kinds of memory, Content-Addressable Memory (CAM) and Random Access Memory (RAM). The CAM is a very fast memory that can perform search operations in a very short time [13,14,15,16,17,18]. The CAM circuit is accessed in parallel and simultaneously based on the content of the data rather than the specific location or address. The CAM circuit is especially suitable for parallel searches based on data due to its internal organization. This type of memory can be used in the Central Processing Unit (CPU) of computers. Therefore, many researchers [5,6,7, 12, 15, 17, 19,20,21] tried to improve the performance of memory circuits, especially CAM circuit.

In this study, a new structure is designed for 1-bit CAM circuit. Since the CAM circuit is composed of two main components: (a) memory unit and (b) identity gate; developing efficient circuits for these components can lead to increase the performance of the CAM circuit. For this purpose, an efficient 1-bit loop-based memory unit is developed as building block in this paper. This building block is composed of a MUX gate, which is constructed based on Majority Gates (MGs) and a feedback. In addition, we propose a new CAM circuit using this memory unit. The QCADesigner tool version 2.0.3 is employed for functionality verification of the developed circuits. The obtained results indicate that this new circuit for the memory unit has 0.01 µm2, 16 cells, and 0.25 clock cycles. The developed CAM circuit has 0.03 µm2, 32 cells, and 0.75 clock cycles. The designed circuits have many advantages with regard to area, cell count, latency, and cost.

The rest of this study is organized as follows: An overview of QCA concepts and structures is presented in Sect. 2. The developed circuits are presented in Sect. 3. The results and their comparison will be introduced in Sect. 4. Finally, we will conclude this study in Sect. 5.

2 Background

This section introduces the basic elements of the QCA technology.

2.1 QCA cell

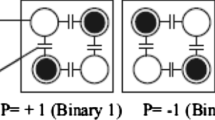

The fundamental element in the QCA technology is a square cell that has two electrons in four dots. These electrons can freely tunnel between dots, but they cannot tunnel out of the cell [11]. So, there are two stable states that creates two polarizations, P = − 1 and P = + 1. These two polarizations are related to digital values “0” and “1” [22,23,24]. The QCA cell polarization is displayed in Fig. 1 [25].

The polarization of the QCA cell a P = + 1 and b P = − 1 [25]

2.2 QCA gates

There are two important QCA gates, (a) the majority gate and (b) inverter gate.

The majority gate with 3 inputs plays a vital role in digital circuits design in the QCA technology. Figure 2 displays this gate. If the majority gate inputs are shown by A, B, and C, the output of this gate is denoted as follows [2, 8]:

The QCA implementation of three-input majority gate [8]

Additionally, if the constant values “1” and “0” are assigned to the input C, the MG will function as AND gate and OR gate, respectively [2, 8].

The inverter output will be the inverse of its input. Figure 3 displays the inverter gate [8]. Figure 3a displays the complex inverter gate in which the output has no noise. Figure 3b displays the simple inverter gate that can be designed using two QCA cells [8].

The QCA inverter gate; a complex gate and b simple gate [8]

These two basic gates are utilized to implement QCA digital circuits such as memory.

2.3 The CAM circuit

The CAM circuit is a very fast memory that can perform search operations in a very short time [13,14,15,16,17,18]. So, many researches have been done to increase the performance of the memory circuits, especially CAM circuit in recent years.

Hashemi and Navi [15] have offered a 1-bit RAM circuit using a robust MUX gate that has set and reset ability. In this circuit, an extra clocking zone is added to read/write signal to synchronize the input signals. This structure is displayed in Fig. 4.

The developed 1-bit QCA RAM circuit in [15]

This RAM circuit has 109 cells, 1.75 clock cycles, and 0.13 µm2 area.

Angizi et al. [19] have offered a 5-input majority gate. Then, they have offered a 1-bit RAM circuit using this 5-input MG and 3-input MG that is shown in Fig. 5. This memory circuit has set and reset ability, which are used to control the output.

The developed 1-bit RAM circuit in [19]

This RAM circuit requires 88 cells, 1.5 clock cycles, and 0.08 µm2 area.

Mubarakali et al. [12] have offered a 1-bit RAM circuit, which has select ability. The designed memory circuit is constructed of a MUX gate, an inverter gate, and five 3-input MG. Figure 6 displays the designed RAM in [12].

The designed 1-bit RAM circuit in [12]

This RAM circuit requires 87 cells, 1.5 clock cycles, and 0.13 µm2 area.

Song et al. [7] have designed a novel loop-based RAM circuit using the developed 2–1 multiplexer and D-latch circuits. The half-cell misplacement method is utilized for the implementation of inverse operation in the developed multiplexer circuit. The developed 1-bit RAM circuit has synchronous set and reset, which has the 3-input MG advantages. Figure 7 displays the designed 1-bit RAM circuit in [7].

The developed 1-bit RAM circuit in [7]

This RAM circuit has 26 cells, 1 clock cycles, and 0.026 µm2 area.

Rasouli Heikalabad et al. [20] have offered a 5-input MG. Then, they have designed a 1-bit CAM circuit based on this offered 5-input MG. Figure 8 displays the designed CAM circuit in [20].

The developed 1-bit CAM circuit in [20]

This CAM circuit requires 100 cells, 0.14 µm2 area, and 2 clock cycles.

Park et al. [6] have offered a 1-bit CAM circuit in three-layer. The developed CAM circuit is illustrated in Fig. 9.

The designed 1-bit CAM circuit in [6]

This CAM circuit requires 89 cells, 0.09 µm2 area, and 2 clock cycles latency.

Hussien et al. [5] have offered a 5-input MG to increase the performance of the developed circuits in [20]. Then, they have designed a 1-bit CAM circuit based on this designed 5-input MG. Figure 10 displays the designed CAM circuit in [5]

The designed 1-bit CAM circuit in [5]

This memory circuit requires 87 cells, 2 clock cycles, and 0.11 µm2 area.

Sadoghifar and Rasouli Heikalabad [17] have designed a unique gate structure using an XOR gate and a 3-input MG. Then, they have designed a 1-bit CAM circuit based on this developed unique gate and memory unit. Figure 11 displays the developed 1-bit CAM circuit in [17].

The designed 1-bit CAM circuit in [17]

This memory circuit requires 46 cells, 1.25 clock cycles, and 0.04 µm2 area.

Majeed et al. [21] have designed an optimal unique block using 2-input XOR gate and 3-input MG. Then, they utilize the developed optimal unique block for building a novel CAM circuit. The developed CAM circuit is shown in Fig. 12.

The designed 1-bit CAM circuit in [21]

This memory circuit requires 40 cells, 1.25 clock cycles, and 0.04 µm2 area.

Although these memory circuits have a suitable performance, the performance of the QCA memory circuits can be increased as described in next section.

3 The proposed circuits

This section presents the proposed structure for the CAM circuit. The proposed structure for the CAM circuit composed of two components: (a) the developed memory unit as building block and (b) identity gate. In the memory unit, the read and write operations are controlled using control signal. The output in this unit is used as the input of the identity gate. The identity gate has the task of matching the memory unit's output to the desired data. This section outlines the developed structures for memory unit and content-addressable memory.

3.1 The proposed memory unit

The proposed structure for the memory unit in the developed CAM circuit is based on the following equation:

Based on Eq. (2), if R/W is "0", the input signal IN will be displayed in the output M. Whenever R/W is "1", the previous value will be hold in the output M regardless of the input IN. The memory unit proposed in this work is consists of a multiplexer 2 to 1 and negative feedback. The feedback loop is implemented by connecting the output M to the input port that is active when R/W is equal to “1”. The proposed QCA structure for the implementation of the memory unit is displayed in Fig. 13. Table 1 shows the correctness of the developed structure for the implementation of memory unit based on Eq. (2).

Our new structure for the memory has 0.01 µm2 area, 0.25 clock cycles, and 16 cells. This new structure will be utilized to develop a CAM circuit.

3.2 The proposed content-addressable memory

The proposed structure for the developed CAM circuit is based on the following equation:

Figure 14 displays the developed structure for the CAM circuit.

The developed structure for the CAM circuit requires 0.03 µm2 area, 0.75 clock cycles, and 32 cells. Recall that the proposed structure composed of two components: the developed memory unit as building block and identity gate. In the memory unit, the read and write operations are controlled using control signal that is shown by R/W. The output in this unit is shown by M that is the input of the identity gate. In addition, the identity gate has two other inputs named A and S. The output of the developed CAM circuit that is also output of the identity gate is shown by Q. Table 2 displays the correctness table for the proposed structure for the QCA CAM circuit based on Eq. (3). In accordance with Eq. (3), when the R/W value of the memory unit of the proposed CAM circuit is set to “0”, the output of memory unit will be equal to the input IN. This means writing operation is performed. On the other hand, when the R/W value of the memory unit of the proposed CAM circuit is set to “1”, the output of the memory unit is the previous value, that means the read operation is performed. Moreover, when the S value is set to “1”, the output Q is “1” and when the S value is set to “0”, the output Q is determined based on the inputs A and M.

4 The results and comparison

This section outlines the simulation results and comparison the obtained results from the proposed structures for memory unit and content-addressable memory with the simulation results that are reported in other works. The developed structures are simulated by using QCADesigner tool version 2.0.3.

4.1 The proposed memory unit

Figure 15 displays the simulation results of the designed memory unit, where the Bistable approximation engine is used for implementation. The simulation results verify the functionality of the designed memory unit. In addition, these results denote that our structure has 0.25 clock cycles delay. Table 3 displays the results of the deigned structure and its comparison with another circuit in [21].

Based on these results that are shown in the Figs. 13, 15 and Table 3, our proposed memory unit provides advantages compared with [21] with regard to cell count, area, latency, and cost. Accordingly, the designed structure has improved compared with that design in [21] by about 50%, 33%, 50%, and 75% with regard to area, cell count, latency, and cost, respectively, due to the use of the proposed structure for the memory unit.

4.2 The proposed content-addressable memory

Figure 16 illustrates the results of the developed CAM circuit. The simulation results verify the functionality of the designed content-addressable memory. In addition, these results denote that our structure has 0.75 clock cycles delay. Table 4 summarizes the results of the simulation in comparison with previous works in [5, 6, 12, 15, 17, 19,20,21].

Based on these results that are shown in Figs. 14, 16 and Table 4, our proposed CAM circuit has advantages compared with [5, 6, 12, 15, 17, 19,20,21] with regard to cell count, area, and cost. The proposed CAM circuit has improved in comparison with that design in [21] by about 25%, 20%, 40%, and 60% with regard to area, cell count, latency, and cost, respectively, due to the use of the developed memory unit and efficient design if CAM circuit.

5 Conclusions

The QCA technology is one of the novel kind of nanotechnologies that has been able to replace the CMOS by relying on its superior capabilities such as speed and area. The CAM circuit is a type of memory circuits that is mostly utilized in high-speed systems. In this paper, a new circuit was developed for the memory unit. Subsequently, this new memory unit was utilized to developed CAM circuit in the QCA technology. The results are obtained using QCADesigner tool version 2.0.3. The proposed circuit for the CAM circuit requires 0.03 µm2 area, 32 cells, and 0.75 clock cycles delay. The simulation results indicate improvements in the proposed circuit compared with other circuits. The proposed CAM circuit has been improved compared to recently designed CAM circuit by about 25%, 20%, 40%, and 60% with regard to area, cell count, latency, and cost, respectively.

References

Divshali MN, Rezai A, Hamidpour SSF (2019) Design of novel coplanar counter circuit in quantum dot cellular automata technology. Int J Theor Phys 58(8):2677–2691

Hariprasad A, Ijjada SR (2019) Quantum-dot cellular automata technology for high-speed high-data-rate networks. Circuits Syst Signal Process 38(11):5236–5252. https://doi.org/10.1007/s00034-019-01119-9

Gudivada AA, Sudha GF (2020) Design of Baugh-Wooley multiplier in quantum-dot cellular automata using a novel 1-bit full adder with power dissipation analysis. SN Appl Sci 2(5):1–13

NiknezhadDivshali M, Rezai A (2021) Novel circuits design for SISO shift register in QCA technology. J Circ Syst Comput. https://doi.org/10.1142/S0218126621502030

Ali Hussien M, MohdShamian Z, Esam A, Danial MdN (2020) A content-addressable memory structure using novel majority gate with 5-input in quantum-dot cellular automata. Int J Integr Eng 12(4):28–38

Park C-S, Jeon J-C (2020) Design of QCA content-addressable memory cell for quantum computer environment. J Converg Cult Technol 6(2):521–527

Song Z, Xie G, Cheng X, Wang L, Zhang Y (2020) An ultra-low cost multilayer RAM in quantum-dot cellular automata. IEEE Trans Circ Syst II Express Briefs 67(12):3397–3401

Jeon J-C (2020) Low-complexity QCA universal shift register design using multiplexer and D flip-flop based on electronic correlations. J Supercomput 76(8):6438–6452. https://doi.org/10.1007/s11227-019-02962-y

Hänninen I, Takala J (2010) Binary adders on quantum-dot cellular automata. J Signal Process Syst 58(1):87–103

Hashemi S, Farazkish R, Navi K (2013) New quantum dot cellular automata cell arrangements. J Comput Theor Nanosci 10(4):798–809

Hashemi S, Azghadi MR, Navi K (2019) Design and analysis of efficient QCA reversible adders. J Supercomput 75(4):2106–2125

Mubarakali A, Ramakrishnan J, Mavaluru D, Elsir A, Elsier O, Wakil K (2019) A new efficient design for random access memory based on quantum dot cellular automata nanotechnology. Nano Commun Netw 21:100252. https://doi.org/10.1016/j.nancom.2019.100252

Chisvin L, Duckworth RJ (1989) Content-addressable and associative memory: alternatives to the ubiquitous RAM. Computer 22(7):51–64

Grosspietsch K-E (1992) Associative processors and memories: a survey. IEEE Micro 12(3):12–19

Hashemi S, Navi K (2012) New robust QCA D flip flop and memory structures. Microelectron J 43(12):929–940

Kohonen T (2012) Content-addressable memories. Springer, Berlin, p 388

Sadoghifar A, Heikalabad SR (2018) A content-addressable memory structure using quantum cells in nanotechnology with energy dissipation analysis. Phys B Condens Matter 537:202–206

Sardinha LH, Silva DS, Vieira MA, Vieira LF, Neto OPV (2015) Tcam/cam-qca:(ternary) content addressable memory using quantum-dot cellular automata. Microelectron J 46(7):563–571

Angizi S, Sarmadi S, Sayedsalehi S, Navi K (2015) Design and evaluation of new majority gate-based RAM cell in quantum-dot cellular automata. Microelectron J 46(1):43–51

Heikalabad SR, Navin AH, Hosseinzadeh M (2016) Content addressable memory cell in quantum-dot cellular automata. Microelectron Eng 163:140–150

Majeed AH, Salih B, bin Zainal MS, Nor DB (2019) Power Efficient optimal structure CAM-cell in QCA technology. Indian J Sci Technol 12(37):1–6

Abdullah-Al-Shafi M, Bahar AN (2016) Optimized design and performance analysis of novel comparator and full adder in nanoscale. Cogent Eng 3(1):1237864

Bahar AN, Waheed S (2016) Design and implementation of an efficient single layer five input majority voter gate in quantum-dot cellular automata. Springerplus 5(1):636

Wang L, Xie G (2018) Novel designs of full adder in quantum-dot cellular automata technology. J Supercomput 74(9):4798–4816

Divshali MN, Rezai A, Karimi A (2018) Towards multilayer QCA SISO shift register based on efficient D-FF circuits. Int J Theor Phys 57(11):3326–3339

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors state that there is no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Enayati, M., Rezai, A. & Karimi, A. Efficient circuit design for content-addressable memory in quantum-dot cellular automata technology. SN Appl. Sci. 3, 804 (2021). https://doi.org/10.1007/s42452-021-04788-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-021-04788-x