Abstract

Quantum-dot cellular automata (QCA) is one of the alternative nanotechnologies that empower nanoscale circuit models with high performance and minimal energy depletion features. In this study, design for a 5-input majority gate (MV5) is proposed. The reported design requires a smaller number of cells, lower time delay, less design cost, and area. The precision of this 5-in MV is confirmed by the theoretical validation, and the QCADesigner simulation engine is applied for proving the majority circuit with functionality. In addition, an optimized full adder (FAd) circuit is designed to consider the appropriateness of the proposed (MV5). The outcomes exhibit that the designed full adder performs reliably well associated with contemporary multi-layer layouts, and executes well in the case of existing coplanar FAd circuits in all sides. The designed FAd obtains an improvement of 20% in terms of covered extent, 35% in cell extent, 32% in cell intricacy, 58% in delay, and 20% in cost correspondingly, as compared to its best counterpart. QCAPro, an energy valuation tool, is employed to assess the power consumption of the reported designs. The outcomes in this work corroborate that the hardware prerequisite for a QCA design is decreased, and circuits become simpler in gate counts and clock segments by considering the proposed design.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

Traditional complementary metal oxide semiconductor (CMOS) archetype has regulated our nanotechnology industry for over past decades; besides, it has sustained to be an effective replacement than preceding technologies [1, 2]. However, gradually a day will come when traditional CMOS technology of circuit designing will attain its shortcoming, and we will have to move to a contemporary technology [3]. Quantum-dot cellular automata (QCA) presents all images of becoming a dominant and improved substitute for the traditional CMOS archetype [4, 5]. In 1993, Lent et al. [1] presented QCA, and it was physically demonstrated in the year 1997 [1]. CMOS archetype is rigid to improve further due to limitations caused by short channel effect and continues to diminish the scope of gate oxides at the nanoscale. Moreover, there are far more scaling limitations in CMOS archetype [3,4,5]. Several researches are employed on devising nanoscale circuits with substitute techniques; for instance, single-electron transistor (SET) or QCA. Among them, QCA is notable due to its attractive features of small size, high performance, and minimal energy depletion [1, 2]. The notable advantage of QCA devices is the simplest connection among cells [6], where a correlation achieved only with adjacent cells; thus, the complete connection is not necessary [7, 8]. A number of QCA based digital devices have studied to date; designs for 5-input majority gate (MV) [9,10,11,12,13,14,15,16,17,18], designs of FAd [10, 14, 19,20,21,22], multipliers [23], dividers [24], memory circuits [25], counter [6] QCA based memory cells [26], flip flops [27,28,29], and multiplexer [30] have also been researched. The application of FAd is inevitable up-to-date transmission where accuracy performs an eminent function. Though the QCA archetype has some difficulties, and one of them is the absence of sophisticated QCA in industrial manufacture [31]. QCA is formed on the mutual repulsion and confinement of electrons, where the basic element is a squared cell with four quantum dots and two additional electrons inside [19, 20]. Moreover, it proposes a different view in data transmission where the data is conducted the transmission of polarization between QCA cells correspondingly. In this study, first, an effective 5-input QCA majority voter is designed, then using this majority voter, the design of FAd is realized. The foremost points of this study are as provided:

-

Designing an effective single layer 5-input majority (MV5) gate with minimal energy dissipation and cell intricacy.

-

Based on the proposed majority voter, a single-layered design for FAd is proposed that utilizes minimal area, latency, cell, and cost compared to the best-listed one in the literature.

-

Comparing the proposed MV5 and FAd with other state-of-the-art designs regarding energy dissipation.

The MV5 is a complex and one of the essential logical element in QCA. Many complex circuits can be designed without difficulty by MV5. Up to now, several MV5 structures are designed, but these designs face many lacking like layer availability, size, could not connect several designs. But, the proposed design solves these issues, and there is a possibility to add more designs with the inputs. The structural proof confirms constancy of the proposed MV5 while energy estimation approves the low power utilization of designed MV. The designed FAd shows significance in the design, and experimental outcomes explain the significant enhancements in design level in terms of area, cell count, energy, and clock compared to that of traditional design styles.

The rest of the study is prepared as follows: “Preliminaries of quantum-dot cellular automata” presents an analysis of QCA structures with different kinds of crossing methods. “An analysis of 5-input majority gate” organizes a thorough study of existing MV5s. Moreover, the proposed majority voter accompanied by physical, resilient, and power study of preceding models is focused in this section. Later in “Designed Full Adder circuit in quantum-dot cells”, the designed majority voter with a FAd circuit is provided along with simulation outcomes. A complete assessment of existing works with energy consumption is reviewed in “Comparative analysis with energy consumption models”, and lastly, the study ends with a concluding part in “Conclusion”.

Preliminaries of quantum-dot cellular automata

Some essential perceptions of QCA nanotechnology, like logical gates, wiring, clocking, and specific faults in QCA, are organized in this section.

Basic structures

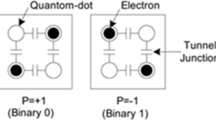

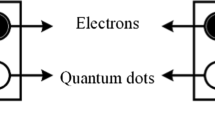

The elementary computing component in QCA is a quantum cell, and every single cellblock encloses quartet quantum dots that are positioned in the four edges of a quadrangle. Every single quantum cell consists of pair electrons that mechanically tunnel concerning these dots through the minimal potential barrier. As shown in Fig. 1a concerning Coulombic revulsion potency, two steady formations of P = + 1 and P = − 1 are designed: which presents ‘1’ and ‘0’ in binary form correspondingly [1, 4]. QCA wires are formed with a structure of cells that are capable of emitting a response to the output signal. Two types of QCA wires, 90° and 45° are exhibited in Fig. 1b, and through the outline, it can be realized that the input in the 90° wire is shifted to the next phase starved of transform, however, in the 45° wire crossing, the feedback can be produced at the output phase.

The majority gate is measured as a significant block of QCA layouts. The 3-in MV is the vital analytical presentation in the QCA nanocircuits that determine the Boolean statement as presented:

Figure 1c presents the QCA illustration of a 3-in MV, and it should be stated that just fixing one of three inputs majority stable to ‘0’ or ‘1’, AND or OR operations can be generated [4]. Because of the remarkable space optimization of nanocircuits by the 3-in MV as assessed to silicon designed transistors, conceiving an optimum configuration for an MV5 acquires many considerations, organized in Fig. 1d. The concept that amplifies the designing interest for this circuit in the study is its capability aimed at proposing the more well-organized FAd circuits [13]. The inverter is another vital block in QCA layouts. The cellular outlooks of the inverters are shown in Figure; where the first inverter circuit that is presented in Fig. 1e poses more cellblocks in contrast with the second one shown in Fig. 1f. The former inverter divergences the input into two routes and joins them by controlling a 45° wire that generates the contrasting polarization.

QCA clocking

QCA circuits need clock pulses so that the circuits operate properly. The clock pulse pursues two main objects. The first one is maintaining energy to circuits, and the next one is regulating data discharge in cells. The flow of electrons enabled by the clock pulses within cells; therefore, permit electrons to transform their formation in a pre-determined routine as well as adjust the blocks of channeling among the dots [4]. There are no power lineups in the QCA archetype. Clock zones allow the operation in a consecutive fashion [19, 20]. Generally, a clocking scheme contains four segments, namely switch, hold, release, and relax, so explained in Fig. 2. Switch period introduces the procedure of cell polarization that remains up to the cell is fully polarized.

The cell retains its polarization once the clock pulse extents the higher level. The process is recognized as a hold phase. The diminution of the cellblock arises once the clock permits over the release phase. To end, the cell is un-polarized at the last clock pulse or Relax phase [32].

Wire-crossing

In QCA configurations, interconnection design between elements requires to be controlled competently for an improved constancy. Until now, there are two distinct sorts of wire crossing are presented, namely, multi-layer and coplanar. Several levels are employed as in-circuit layout for interconnection among QCA elements in a multi-layer design, as represented in Fig. 3a. Wiring is completed by distinct diploid cells in coplanar crossing where these cells are rectangular to one another; therefore, they work exclusive of concerning adjoining cells. The first wire contains cells of 90° formations, and the second has 45° formations, as illustrated in Fig. 3b. One of the major shortcomings of this structure is that a little misalignment of cells throughout design might affect a cross-connecting between the two wires. Researches have been organized to lessen suchlike influences, as well to enhance the durability of the nanocircuits; nevertheless, these schemes turn out with oversized space overhead [33]. A special type of coplanar wiring is focused in Shin et al. [34] where a crossing is formed on the interference of clocking segments as presented in Fig. 3c.

QCA realization concerns

Molecular dots, metal islands, and semiconductor dots [35] are measured as QCA based archetypes [36]. Molecular dots have a precisely small extent and specify extreme frequency [37] where metal islands and semiconductor dots operate at minimal temperature. By recognizing the structural complications, all improvement could be materially applied. A major contentious limitation in applied QCA nanocircuits is their functional condition [4]. This minimum temperature is measured as a suitable division of a QCA cell [24]. Some surveys [35, 37] also have been carried out to review the possibility of expanding QCA temperature. These reviews illustrate the substantial aspects of the QCA by allowing QCA-designed circuits with excessive conditions.

Faults in QCA

Mostly, deficiencies in QCA ensue in the impeachment procedure. These faults are mainly separated into four groups, as presented:

-

Cell exclusion or omission: this sort of fault arises by reason of the omission of one particular cell, as shown in Fig. 4a.

-

Cell displacement: this category of defect arises because of the dislocation of cells from the primary position as exhibited in Fig. 4b.

-

Cell misalignment: this kind of fault arises because of the misalignment of cells, as presented in Fig. 4c.

-

Extra-cell accretion: this sort of fault arises by reason of the exclusion of the cell in bed, as shown in Fig. 4d.

An analysis of 5-input majority gate

For several years, nanocircuits based on QCA are developed with 3-input majority gates (3-in MV). In the meantime, specialists have presented the MV5 schemes are well-organized concerning area occupied as well firm than the conventional ones. Each design integrates the identical synchronization style of 3-in MV. Already, a number of configurations for MV5 have been focused [9,10,11,12,13,14,15,16,17,18]. The Boolean depiction of the MV5 can be presented as follows:

The circuit design in [9], the output cell, is enclosed by input cells, which is problematic to contact the layout in a single crossing. The design in [10] undergoes from surplus consequence as input blocks are proximate enough to one another. Designs recommended in [11, 12] strove to alleviate the mentioned complications. A related study also has been presented in [13, 14]. A single layer design is proposed in [17] needs 11 cells, but the input cells are adjacent to each other. In [18], another layout is presented, which requires 11 cells, but this design encounters some polarization complications.

Structural proof

To substantiate a QCA gate, 32 distinctive input states are essential for a MV5. In this study, we have deliberated only one position out of 32. We have studied A = D = 0, B = C = E = 1, to prove the precision of the proposed circuit. All the cells are equivalent dimension (18 × 18) nm, and the pair of adjoining cells are splitting by a distance of 2 nm. We have used a top-down approach to find potential energy. The estimation is counted from the adjoining cell of the output cell. The overall polarization is inverted at the output level. Using the adjacent cell of the output, there is no big impact on the considering cell to other cells. So, the overall estimation is accurate. Electrons are organized in such a method, which reduces their latent force to attain constancy. The force or energy U joining two charges is calculated with Eqs. (3) and (4), respectively [38]. The possible energy defined as U, between electron charges, is assessed from Eq. (5). In Eq. (3), Keq is preset colon, and r is the space between electron charges:

Two distinctive positions for electrons x and y are studied for cell 1, as indicated in Fig. 5a and b. The key concept following this is to locate a position that presents marginal latent energy.

For X electron,

For Y electron,

The same approach can be utilized to find the potential energy from a different state. We have considered another position of the design to find the energy, as presented in Fig. 6:

Total potential energy for< structure 2,

For the complete latent energy of both x and y, regarding electrons in both positions are estimated using the mentioned equations. It is noticed that the position in structure 1 is steadier.

Physical investigation

The outlined majority voter contains 12 QCA cells where five cells are inputs, five cells are middle cells, and one output. An extra cell is used with the output block, which inverts the charge of the operations. The proposed gate has a significance that it is occupied in a single layer; thus, simple to contact the cells with no extra crossing in the gate. The outlined architecture is expedient and pliable, contrasting existing designs. The middle cells are polarized by input cells, but the output is less polarized due to the adjacent cell of the output. These influences transmit the mainstream result of responses to the corresponding output and consequence a MV5. The output and feedback blocks are not confined by other cells that defeat the limitation within the aforementioned gates. The designed majority gate is indicated in Fig. 7a, and to authenticate the gate, simulation outcome has been exhibited in Fig. 7b. The proposed design attains anticipated outcomes with sophisticated polarization. Underlying investigation of the outlined design with all accessible designs is organized in Table 1, where quite a few imperative factors like cellblock intricacy, ratio, area engaged, polarization, and coplanar availability is considered. The designs in [9, 10, 17, 18] take fewer cells than the proposed one but take more extent for implementation moreover;, some designs are not entirely single layer accessible. The designed circuit indicates a noteworthy development concerning intricacy, polarization, ratio, the area covered, and coplanar availability in contrast to other layouts [9,10,11,12,13,14,15,16,17,18]. The outlined circuit relishes full availability to input and output cells.

Power analysis

To evaluate the overall energy dissipation of QCA circuits, a Hamiltonian matrix is focused. Hamiltonian matrix for a range of QCA cells can be determined with Hartree–Fock estimation and mean-field method interactivity [39] as presented in Eq. 3:

In the above equation, Xi implies polarization of the ith adjoining cell, fi,j is the scientific aspect identifying the electrostatic line connecting cell i and j cells following the scientific plot, γ is the channeling potency connecting two logic positions of a cell and \(\sum_{i}\mathrm{i}\mathrm{s}\) the complete potential over the blocks.

The possible charge for a QCA cell energy at every single clock phase is estimated from the following equation:

In Eq. (4), \(\hbar\) outlined as the Planck constant, \(\overrightarrow {{{\kern 1pt} \Gamma }}\) is the energy atmosphere vector, and \(\overrightarrow {\lambda }\) is the coherence vector.

The power operations in a QCA cell are classified into four major points as Pdiss, Pclock, Pout, and Pin. The operations of Pout and Pin are alike except Pout signifies the liquidated energy to the rightward cell, and Pin signifies the achieved energy from the leftward adjacent QCA cell [39]. Right through the switch stage, inter-dot cellblocks are steadily lifted, pointing to the transference of a suggestive degree of force to the cellblock, and in the release phase, the cellblocks are bit by bit lessened; therefore a part of the consuming force is folded back to the signaling level. Thus, there is a marginal energy lessening identified Pdiss. The instantaneous comprehensive energy for a distinct cell can be assessed as:

Two foremost factors implicated in Eq. (7): firstly, the enhancement of energy arrives at the variation of the feedback and output signal then afterward, assigned clocking signal or Pclock to the cellblock. The complete depleted power denoted by Pdiss. The energy consumption of a cellblock in a particular cycle Tee = [− T, T] is attained in regard to Hamiltonian and Coherence vectors [40] as presented:

It is substantial to specify that even though the variation degree of \(\overset{\lower0.5em\hbox{$\smash{\scriptscriptstyle\rightharpoonup}$}}{\Gamma }\) is uppermost, the highest energy will be dissipated. Weighing \(\overset{\lower0.5em\hbox{$\smash{\scriptscriptstyle\rightharpoonup}$}} {\Gamma } _{ + }\) and \(\overset{\lower0.5em\hbox{$\smash{\scriptscriptstyle\rightharpoonup}$}} {\Gamma } _{ - }\) separately, the energy depletion pattern of higher bound is acquired and presented in equation [9]:

In Eq. (9),\(\overset{\lower0.5em\hbox{$\smash{\scriptscriptstyle\rightharpoonup}$}} {\Gamma } _{ + }\) and \(\overset{\lower0.5em\hbox{$\smash{\scriptscriptstyle\rightharpoonup}$}} {\Gamma } _{ - }\) are the Hamiltonian assesses former and following the variation, T is the stable temperature, and Kz is the Boltzmann constant. A comparative study of the designed FAd with existing designs is presented in “Comparative analysis with energy consumption models”.

Designed full adder circuit in quantum-dot cells

An immense significant arithmetic operation that arises in digital logic is the addition. Other mathematical functions like subtraction, multiplication, and division are fulfilled with adders. Thus, a constructive adder is indispensable being conniving the excessive performing arithmetic operations. A recent enhanced QCA FAd is organized in this part with an optimized five input majority voter.

The graphical representation of the outlined FAd is directed in Fig. 8a with the QCA circuit diagram in b, respectively. The outcomes of a FAd can be figured as presented:

As shown in Fig. 8, the logical layout for realizing the FAd is constituted of four key building blocks covering two basic inverters, one 3-in MV and MV5. In the proposed circuit, a usual form of QCA cells is utilized, which has a well-organized outline for fabricating. Various research on FAd has been done so far [10, 14, 19,20,21,22], but maximum layouts are confined to 3-in MV.

Simulation tools

Walus et al. [32] proposed a competent software for QCA-based circuit design, QCADesigner, which is a widespread simulation engine for circuit design. This tool permits clients to draw as well as to authenticate a variety of assignments in QCA. The principle of this simulation tool is to form an expedient model and design that can be accessible spontaneously to the researchers. A significant design parameter is that other designers should be capable of integrating their own functionalities into QCADesigner [41]. In addition, simulation tools can be added into QCADesigner with a harmonized convening technique with data types. The existing copy of QCADesigner involves three modeling tools. The primary is a digital simulant that counts cellblocks to be either null or entirely diverged [32]. The next one is a nonlinear estimation approach that applies the nonlinear cell response method to state the persistent status of the cellblocks inside a layout [42]. The last one organizes an estimation of the extensive quantum automated paradigm of correspondent a system. Architecture might be distinct or multi-layered. In a single crossing outline, usual cellblocks rotated cells as well firm polarity cells can be occupied. Once a clock changes from one particular level to next, it passes over perpendicular cells. Afterward, at the top level, it transmits over crossover QCA cells. To conclude, it can go low to the core level over perpendicular cellblocks.

For energy depletion, QCAPro [40], a versatile engine for dissipated energy calculation, is utilized. QCAPro presently uses the design file produced from QCADesigner. With this design file, QCAPro can operate a rapid design assessment to check the value of outputs for all potential series of inputs. It originates the polarization probability of distinct cells in a circuit with an estimation technique. Therefore, the results acquired from this engine for polarization and energy depletion are a pessimistic estimation. This tool can be utilized to find out the average power deficiency, upper and lower power deficiency in a circuit through an input switching process [40].

Existing QCA FAd models

A number of full-adder circuits have been studied so far. In this part, the existing QCA adders are investigated. The design in [43] takes 95 QCA cells, 0.087 μm2 area, delay 8 with quantum cost 0.1740. The design of Kianpour et al. [44] takes 69 cells, 0.07 μm2 area, four clock phases with quantum cost 0.07. The design is coplanar. Roohi et al. [12] proposed a design with 58 cells, and the extent of 0.04 μm2, three clock phases, and cost are 0.03, but it is a multi-layer approach. In [14], a coplanar adder with 71 cell, 0.06 μm2 extent, delay 3 and quantum cost 0.045 is proposed. Sen et al. [45] outlined a coplanar adder that incorporates 86 QCA cells, 0.08 μm2 area, delay 4 with quantum cost 0.08. Mohammadi et al. [21] design an efficient adder with 38 cells, 0.02 μm2 area, three clock phases with quantum cost 0.015, but the layout is a multi-layer. In [46, 47] two adders with 22 and 23 cell, 0.01 μm2 area, delay 3 with quantum cost 0.007, respectively, is proposed. However, both designs are multi-layer. Another multi-layer adder design in [9] is proposed by Navi with 61 cells, 0.03 μm2 area, clock phases 3 with quantum cost 0.0225. In [48], a design with 63 QCA cells, 0.05 μm2 extent, delay 3, and quantum cost 0.0375 is proposed. Navi et al. [10] proposed another competent layout. But it was a multi-layer adder with 0.04 μm2 extent, clock phases 3, 73 QCA cell with quantum cost 0.030. A coplanar design is proposed in [49] that contain 0.06 μm2 extent, four clock phases, 60 QCA cell with quantum cost 0.060. Sonare et al. [50] design a layout with 95 cells, 0.12 μm2 area, four clock phases, with quantum cost 0.120. A multi-layer adder in [51] with 0.06 μm2 extent, four clock phases, 86 QCA cell, and quantum cost 0.060 is proposed by pudi. Besides, design with the XOR gate is presented in [19]. Most of the time, it is practicable to use a coplanar approach rather than multi-layers.

Outcome study

In recent, researches illustrate the rising demands for functional QCA-based circuits. A number of coplanar and multi-layer designs have been achieved so far. As clarified in Fig. 9, the simulation outcome of the proposed adder with three consecutive input. Intricacy, latency, and cost are measured as the major benefits of QCA design that outclass all the counterparts with significant supremacy.

The simulation outcome for all inputs Ao, Bo, and Co are clarified in Fig. 9 and result indorse that the designed FAd performs well and specifies the opposite operation. In this design, Ao, Bo, and Co are considered as inputs, and the output cells are considered as sum and Cout. For instance, the input combinations of Ao = Bo = Co = 1, the precise outcomes combinations of Cout = 1 with sum = 1 are conceived, as illustrated in Fig. 9. The major significant waveshape attained commencing the carry-sum product, is formed following one clock cycle. For the input combination {Ao Bo Co} = {000, 001, 010, 011, 100, 101, 110, 111} all specific faulty results in the outcome sum are acquired: {01110001, 00001111, 11001100, 11010100, 01010101, 00101011, 10101010, 01001101, 00010111, 00110011}; moreover, each specific faulty results in Cout are acquired: {11101000, 00110011, 00001111, 01001101, 10001110}. The comparative investigation presents that the proposed structure has more compactness than the existing designs.

Comparative analysis with energy consumption models

A complete comparative study of designed and existing FAd is demonstrated in this section. Table 2 presents that the outlined QCA FAd expands the existing adders with regard to area, latency, cost as well as complexity. The comparison analysis organizes that the proposed adder is quite efficient compared to other coplanar and multi-layer adder circuits in [41, 43, 44, 14,15,16, 48, 49, 43,44,45,46,47,48,49,50,51,52,53,54,55,56,57,58,59,60,61,62,63,64,65,66,67,68,69,70]. Though fewer cells engaged in [15, 19, 21, 46, 47, 54, 60, 61], the outlined adder circuit in this study has enhanced performance. Moreover, the adder circuit designed in a single layer without using any rotating cell. It could be verified that extending the feedback and result appearances of the designed adder circuit indicates to further consistent response with the designed adder is beyond consistent around fluctuating the appearance shapes than the model. Besides, congruity with existing layouts, convenience to the feedbacks, and results with the pliability for modifying the size of the input and product appearances are other benefits of the outlined adder. The assessment between the designed adder outline and existing outlines are illustrated in Table 2. In Table 2, area utilization, cost, and ratio can be found using the following equations:

Relative improvement assessment

The proposed adder has a precise solid outline and an identical potential with the existing preeminent models. Besides, the design encompasses a minimum number of inverters and majority gates. The proposed design has 33, 27, 24, and 33% progress regarding the enclosed extent, cell area, cell intricacy with cost, separately, in contrast with [14]. In contrast with the designed adder in [16], our design has 20, 35, 32, 58, and 20% enhancements in extent, cell extent, cell count, delay, and cost parameters, correspondingly. Similarly, designed FAd received improvements of 60, 58, 57, 40, and 76% in terms of area, cell area, cell count, delay, and cost parameters compared with [22]. Compared to [55], the proposed design obtained an enhancement of 76, 64, 63, 25, and 82% in terms of area, cell area, cell count, delay, and cost parameters. In contrast with the designed FAd in [58], our design obtains an extreme improvement. It has 88, 76, 75, 58, and 88% enhancements in extent, cell extent, cell count, and cost parameters, correspondingly. Maximum improvements are achieved with [41], where almost 93, 82, 81, 78, and 98% improvements are attained in terms of area, cell area, cell count, delay, and cost parameters, respectively. Besides, our proposed adder has the convenience of output cells. Other improvements with corresponding parameters are presented in Figs. 10 and 11. Though some design enclosed the same or less area than the proposed design [9, 10, 12, 15, 19, 21, 46, 47, 60, 65]. Likewise, design [15, 19, 21, 46, 47, 61] has less cell area, design [19, 21, 46, 47, 54, 60, 61] consumed less cell, design [9, 10, 12, 14, 15, 19, 21, 23, 24, 46,47,48, 54, 58, 63,64,65,66,67,68,69,70] has equal or less delay, and design [9, 10, 12, 15, 21, 46, 47, 54, 60, 61, 63, 68] has fewer quantum cost than the proposed design. But all the mentioned adder circuits are designed in a multi-layer approach. Thus, these circuits have some design sophistication.

The proposed adder takes a minimal cell with lower latency, area, and quantum cost. Moreover, it is designed for avoiding a multi-layer approach. A comprehensive analysis concerning the extent, cell extent, cell complication, delay, and cost are presented in Fig. 11. From Fig. 11a, it is perceived that the proposed FAd contains a minimal extent. As in [14] and [23], these designs have an extent of 0.06 μm2 and 0.09 μm2, respectively, where the extent of the proposed design is 0.04 μm2. Similarly, the proposed design shows its improvements over the existing design. Though some design consumes less extent, like [9, 15, 46]; however, those designs are multilayered circuits.

The maximum extent of 0.62 μm2 in [41] shows the highest peak of the figure. Figure 11b illustrates the cell extent of the presented design, where the proposed FAd has a minimal cell extent of 0.017 μm2 than existing. The highest cell extent is 0.0095 μm2 designed in [41]. Cell complication is presented in Fig. 11c, where it shows the proposed FAd takes 54 cells. Most of the design presented in the figure contains more cells than the proposed. However, several designs like [15, 46, 47, 60, 61] take a fewer cells, but these designs have multi-layer limitations. The delay of the layouts is presented in Fig. 11d where the highest delay is 14 for the design in [41], and the lowest is 1 for [63, 66, 68]. The delay of our design is three clock phases, and compared to [63, 66, 68], the design in [63, 68] is both multi-layer and [66] contains more extent and cell extent than proposed design. Figure 11e shows the quantum cost, where the highest cost is 2.17 for design [41]. The proposed FAd has a cost of 0.03, which is quite beneficial than the existing design.

Energy dissipation study

For measuring the overall energy depletion of the proposed majority voter and FAd, QCAPro [40] has been utilized as an energy assessor tool. This simulation engine mainly used to find out thorough dissipated energy [71]. Though others approach like Hamming distance [72], QCADesigner-Energy [19] is used in many researches. For estimation, three distinct channeling energies are acquired (0.5 Ek, 1.0 Ek, 1.5 Ek) at 2 K temperature. Figure 12 illustrates the energy depletion charts of the proposed majority voter and FA circuit with directing the energy of 1.0 Ek. Cells with extreme energy deletion are signified by more dark colors in thermal hotspot plots. A relative evaluation of energy depletion of designed majority voter and FAd circuit is represented in Tables 3 and 4 correspondingly, where outflow and switching energies influence to overall power depletion. From Tables 3 and 4, it is perceived that designed circuits reach minor energy depletion in contrast to all standing coplanar MV5 and FAds.

Figures 13 and 14 are presented for entire energy depletion for all proposed designs to enhanced readability. From Fig. 13, it is obvious that the proposed majority voter energy depletion performance is superior over the design in [9,10,11,12,13,14, 17, 18]. As compared with [11], total depleted energy at 0.5 Ek, 1.0 Ek, 1.5 Ek channeling energy is 36.1 meV, 40.56 meV and 46.53 meV, correspondingly but in the proposed design the overall depletion rate is very low e.g. 1.02e − 8 meV, 1.39e − 8 meV and 1.82e − 8 meV correspondingly. The proposed design is very beneficial as compared with design in [18]. The design in [18] takes 7.90 meV, 10.34 meV and 13.31 meV energy from three distinct energy levels at 2 K temperature. Similarly, assess with its best counterpart in [13], the design consume huge energy at different channeling energy e.g. 49.96 meV, 55.84 meV and 63.90 meV correspondingly but the proposed design shows incredible performance by consuming minimal energy. Other comparisons for majority voter are effected in Fig. 13. In Fig. 14, it is noticeable that proposed design FAd is exceeding over the design in [44, 53, 55, 59, 63, 65, 67, 69, 70, 73,74,75,76,77].

Comparing to adder in [44], the design consumes 143.52 meV, 190.31 meV and 246.92 meV energy at three different energy levels of 0.5 Ek, 1.0 Ek, 1.5 Ek while in the proposed design, it takes 107.52 meV, 122.57 meV and 148.00 meV, respectively. The design in [70], consumes 138.51 meV, 180.14 meV and 233.38 meV energy which is quite high than the proposed design. In [76], the design dissipates huge energy 172.07 meV, 254.00 meV and 349.17 meV at three different energy levels at 2 K temperature. However, the designed FAd dissipates minimal energy at the same temperature. Though the design in [53, 55, 59, 65, 67, 75] dissipates minimal energy although these design has several intrications for instance, area utilization, total number of cell, delay, cell extent and wire crossing. The proposed FAd shows improved performance regards these issues. It is significant observing that the overall energy depletion of the outlined circuits is quite reduced associated to the remaining designs. This low energy and reduced extent aspects allow designers to comprehend complex and low power QCA circuits. The temperature position on the result polarization of proposed designs is comprehended at various temperatures by QCADesigner software [78]. The average or standard output polarization (AOP) for all QCA block is estimated as of [79, 80]. Both designs operate capably in the temperature range of 1–12 K, with the AOP for each QCA cellblock, which is distorted quite small to this extent.

Conclusion

In this study, a modified proficient MV5 has been designed with substantial proofs. To sustenance this, a thorough assessment of structures and energy concerns of all previous designs and proposed MV5 were performed. QCADesigner 2.0.3, a widely used simulation engine was applied to evaluate the circuits and power is assessed through QCAPro tool. Next, a refurbished low energy depleted FAd circuit is proposed to represent the effectiveness of the proposed MV5. The designed FAd focuses on the coplanar layout; besides, it is practical that this coplanar configuration is efficient for significant adaptation in temperature with concedes more solid digital circuits respecting existing coplanar models. The simulation outcomes verified that the proposed circuits have overtaken all aforementioned layouts with regard to the cost function and indicated noteworthy enhancements in terms of cell intricacy, the area covered, energy depletion, and input–output clock delay in assessment to most of the multi-layer and coplanar designs. The outlined preeminent structures can make it possible for designing more composite and high-functioning nanoscale QCA circuits in the future.

References

Lent, C.S., Tougaw, P.D., Porod, W., Bernstein, G.H.: Quantum cellular automata. Nanotechnology 4(1), 49 (1993)

Wilson, M., Kannangara, K., Smith, G., Simmons, M., Raguse, B.: Nanotechnology: basic science and emerging technologies. CRC Press, Boca Raton (2002)

Hoefflinger, B.: ITRS: the international technology roadmap for semiconductors. Chips 2020, pp. 161–174. Springer, Berlin (2011)

Lent, C.S., Tougaw, P.D.: A device architecture for computing with quantum dots. Proc. IEEE 85(4), 541–557 (1997)

Fijany, A., Toomarian, B.N.: New design for quantum dots cellular automata to obtain fault tolerant logic gates. J. Nanoparticle Res. 3(1), 27–37 (2001)

Abdullah-Al-Shafi, M., Bahar, A.N., Habib, M.A., Bhuiyan, M.M.R., Ahmad, F., Ahmad, P.Z., Ahmed, K.: Designing single layer counter in quantum-dot cellular automata with energy dissipation analysis. Ain Shams Eng. J. 9(4), 2641–2648 (2017)

Bahar, A.N., Uddin, M.S., Abdullah-Al-Shafi, M., Bhuiyan, M.M.R., Ahmed, K.: Designing efficient QCA even parity generator circuits with power dissipation analysis. Alex. Eng. J. 57(4), 2475–2484 (2018)

Bahar, A.N., Billah, M., Bhuiyan, M.M.R., Abdullah-Al-Shafi, M., Ahmed, K., Asaduzzaman, M.: Ultra-efficient convolution encoder design in quantum-dot cellular automata with power dissipation analysis. Alex. Eng. J. 57(4), 3881–3888 (2018)

Navi, K., Sayedsalehi, S., Farazkish, R., Azghadi, M.R.: Five-input majority gate, a new device for quantum-dot cellular automata. J. Comput. Theor. Nanosci. 7(8), 1546–1553 (2010)

Navi, K., Farazkish, R., Sayedsalehi, S., Azghadi, M.R.: A new quantum-dot cellular automata full-adder. Microelectron. J. 41(12), 820–826 (2010)

Akeela, R., Wagh, M.D.: A five-input majority gate in quantum-dot cellular automata. In: NSTI Nanotech, vol. 2, pp. 978–981 (2011)

Roohi, A., Khademolhosseini, H., Sayedsalehi, S., Navi, K.: A symmetric quantum-dot cellular automata design for 5-input majority gate. J. Comput. Electron. 13(3), 701–708 (2014)

Angizi, S., Sarmadi, S., Sayedsalehi, S., Navi, K.: Design and evaluation of new majority gate-based RAM cell in quantum-dot cellular automata. Microelectron. J. 46(1), 43–51 (2015)

Hashemi, S., Navi, K.: A novel robust QCA full-adder. Proc. Mater. Sci. 11, 376–380 (2015)

Sen, B., Rajoria, A., Sikdar, B.K.: Design of efficient full adder in quantum-dot cellular automata. Sci. World J. 2013, 1–10 (2013)

Hashemi, S., Tehrani, M., Navi, K.: An efficient quantum-dot cellular automata full-adder. Sci. Res. Essays 7(2), 177–189 (2012)

Sheikhfaal, S., Angizi, S., Sarmadi, S., Moaiyeri, M.H., Sayedsalehi, S.: Designing efficient QCA logical circuits with power dissipation analysis. Microelectron. J. 46(6), 462–471 (2015)

Sasamal, T.N., Singh, A.K., Mohan, A.: An optimal design of full adder based on 5-input majority gate in coplanar quantum-dot cellular automata. Optik 127(20), 8576–8591 (2016)

Abdullah-Al-Shafi, M., Bahar, A.N.: An architecture of 2-dimensional 4-dot 2-electron QCA full adder and subtractor with energy dissipation study. Active Passive Electron. Compon. 2018, 1–10 (2018)

Abdullah-Al-Shafi, M., Bahar, A.N.: Optimized design and performance analysis of novel comparator and full adder in nanoscale. Cogent Eng. 3(1), 1237864 (2016)

Mohammadi, M., Mohammadi, M., Gorgin, S.: An efficient design of full adder in quantum-dot cellular automata (QCA) technology. Microelectron. J. 50, 35–43 (2016)

Kumar, D., Mitra, D.: Design of a practical fault-tolerant adder in QCA. Microelectron. J. 53, 90–104 (2016)

Cho, H., Swartzlander, E.E.: Adder and multiplier design in quantum-dot cellular automata. IEEE Trans. Comput. 58(6), 721–727 (2009)

Sayedsalehi, S., Azghadi, M.R., Angizi, S., Navi, K.: Restoring and non-restoring array divider designs in quantum-dot cellular automata. Inf. Sci. 311, 86–101 (2015)

Abutaleb, M.M.: A novel power-efficient high-speed clock management unit using quantum-dot cellular automata. J. Nanoparticle Res. 19(4), 128 (2017)

Vankamamidi, V., Ottavi, M., Lombardi, F.: A serial memory by quantum-dot cellular automata (QCA). IEEE Trans. Comput. 57(5), 606–618 (2008)

Abdullah-Al-Shafi, M., Bahar, A.N.: Ultra-efficient design of robust RS flip-flop in nanoscale with energy dissipation study. Cogent Eng. 4(1), 1391060 (2017)

Shamsabadi, A.S., Ghahfarokhi, B.S., Zamanifar, K., Movahedinia, N.: Applying inherent capabilities of quantum-dot cellular automata to design: D flip-flop case study. J. Syst. Archit. 55(3), 180–187 (2009)

Yang, X., Cai, L., Zhao, X.: Low power dual-edge triggered flip-flop structure in quantum dot cellular automata. Electron. Lett. 46(12), 825–826 (2010)

Abdullah-Al-Shafi, M., Bahar, A.N., Ahmad, F., Ahmed, K.: Performance evaluation of efficient combinational logic design using nanomaterial electronics. Cogent Eng. 4(1), 1349539 (2017)

Tahoori, M.B., Momenzadeh, M., Huang, J., Lombardi, F.: Defects and faults in quantum cellular automata at nano scale. In: 22nd IEEE VLSI test symposium, 2004. Proceedings, pp. 291–296. IEEE (2004)

Walus, K., Dysart, T.J., Jullien, G.A., Budiman, R.A.: QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3(1), 26–31 (2004)

Bhanja, S., Ottavi, M., Lombardi, F., Pontarelli, S.: QCA circuits for robust coplanar crossing. J. Electron. Test. 23(2–3), 193–210 (2007)

Shin, S.H., Jeon, J.C., Yoo, K.Y.: Design of wire-crossing technique based on difference of cell state in quantum-dot cellular automata. Int. J. Control Autom. 7(4), 153–164 (2014)

Mitic, M., Cassidy, M.C., Petersson, K.D., Starrett, R.P., Gauja, E., Brenner, R., Clark, R.G., Dzurak, A.S., Yang, C., Jamieson, D.N.: Demonstration of a silicon-based quantum cellular automata cell. Appl. Phys. Lett. 89(1), 013503 (2006)

Lu, Y., Liu, M., Lent, C.: Molecular quantum-dot cellular automata: from molecular structure to circuit dynamics. J. Appl. Phys. 102(3), 034311 (2007)

Walus, K., Jullien, G.A.: Design tools for an emerging SoC technology: quantum-dot cellular automata. Proc. IEEE 94(6), 1225–1244 (2006)

McDermott, L.C.: Research on conceptual understanding in mechanics. Phys. Today 37(7), 24–32 (2008)

Timler, J., Lent, C.S.: Power gain and dissipation in quantum-dot cellular automata. J. Appl. Phys. 91(2), 823–831 (2002)

Srivastava, S., Sarkar, S., Bhanja, S.: Estimation of upper bound of power dissipation in QCA circuits. IEEE Trans. Nanotechnol. 8(1), 116–127 (2009)

Vetteth, A., Walus, K., Dimitrov, V.S., Jullien, G.A.: Quantum-dot cellular automata carry-look-ahead adder and barrel shifter. In: IEEE emerging telecommunications technologies conference, pp. 2–4 (2002)

Amlani, I., Orlov, A.O., Toth, G., Bernstein, G.H., Lent, C.S., Snider, G.L.: Digital logic gate using quantum-dot cellular automata. Science 284(5412), 289–291 (1999)

Bishnoi, B., Giridhar, M., Ghosh, B., Nagaraju, M.: Ripple carry adder using five input majority gates. In: Electron devices and solid state circuit (EDSSC), 2012 IEEE international conference on 2012, pp. 1–4. IEEE (2012)

Kianpour, M., Sabbaghi-Nadooshan, R., Navi, K.: A novel design of 8-bit adder/subtractor by quantum-dot cellular automata. J. Comput. Syst. Sci. 80(7), 1404–1414 (2014)

Sen, B., Sahu, Y., Mukherjee, R., Nath, R.K., Sikdar, B.K.: On the reliability of majority logic structure in quantum-dot cellular automata. Microelectron. J. 47, 7–18 (2016)

Seyedi, S., Navimipour, N.J.: An optimized design of full adder based on nanoscale quantum-dot cellular automata. Optik 158, 243–256 (2018)

Roohi, A., DeMara, R.F., Khoshavi, N.: Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron. J. 46(6), 531–542 (2015)

Labrado, C., Thapliyal, H.: Design of adder and subtractor circuits in majority logic-based field-coupled QCA nanocomputing. Electron. Lett. 52(6), 464–466 (2016)

Goswami, M., Mohit, K., Sen, B.: Cost effective realization of XOR logic in QCA. In: 2017 7th international symposium on embedded computing and system design (ISED), pp. 1–5. IEEE (2017)

Sonare, N., Meena, S.: A robust design of coplanar full adder and 4-bit ripple carry adder using qunatum-dot cellular automata. In: 2016 IEEE international conference on recent trends in electronics, information and communication technology (RTEICT), pp. 1860–1863. IEEE (2016)

Pudi, V., Sridharan, K.: Low complexity design of ripple carry and Brent-Kung adders in QCA. IEEE Trans. Nanotechnol. 11(1), 105–119 (2012)

Waje, M.G., Dakhole, P.K.: Analysis of various approaches used for the implementation of QCA based full adder circuit. In: 2016 international conference on electrical, electronics, and optimization techniques (ICEEOT), pp. 2424–2428. IEEE (2016)

Abedi, D., Jaberipur, G., Sangsefidi, M.: Coplanar full adder in quantum-dot cellular automata via clock-zone-based crossover. IEEE Trans. Nanotechnol. 14(3), 497–504 (2015)

Safoev, N., Jeon, J.C.: Full adder based on quantum-dot cellular automata. In: Proceedings of international conference of trends in engineering and technology, pp. 83–86 (2017)

Wang, W., Walus, K., Jullien, G.A.: Quantum-dot cellular automata adders. In: 2003 Third IEEE conference on nanotechnology, 2003. IEEE-NANO 2003, vol. 1, pp. 461–464. IEEE (2003)

Azghadi, M.R., Kavehie, O., Navi, K.: A novel design for quantum-dot cellular automata cells and full adders. arXiv preprint arXiv:1204.2048 (2012)

Pudi, V., Sridharan, K.: Efficient design of a hybrid adder in quantum-dot cellular automata. IEEE transactions on very large scaleintegration (VLSI) systems 19(9), 1535–1548 (2010)

Kim, K., Wu, K., Karri, R.: The robust QCA adder designs using composable QCA building blocks. IEEE Trans. CAD Integr. Circuits Syst. 26, 176–183 (2007)

Tougaw, P.D., Lent, C.S.: Logical devices implemented using quantum cellular automata. J. Appl. Phys. 75(3), 1818–1825 (1994)

Sayedsalehi, S., Moaiyeri, M.H., Navi, K.: Novel efficient adder circuits for quantum-dot cellular automata. J. Comput. Theor. Nanosci. 8(9), 1769–1775 (2011)

Sarmadi, S., Sayedsalehi, S., Fartash, M., Angizi, S.: A structured ultra-dense QCA one-bit full-adder cell. Quantum Matter 5(1), 118–123 (2016)

Cho, H., Swartzlander, E.E.: Adder designs and analyses for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 6(3), 374–383 (2007)

Zhang, R., Walus, K., Wang, W., Jullien, G.A.: Performance comparison of quantum-dot cellular automata adders. In: 2005 IEEE international symposium on circuits and systems, pp. 2522–2526. IEEE (2005)

Cho, H.: Adder and multiplier design and analysis in quantum-dot cellular automata. PhD dissertation, Faculty of the Graduate School, University of Texas, Austin (2006)

Angizi, S., Alkaldy, E., Bagherzadeh, N., Navi, K.: Novel robust single layer wire crossing approach for exclusive or sum of products logic design with quantum-dot cellular automata. J. Low Power Electron. 10(2), 259–271 (2014)

Zhang, R., Walnut, K., Wang, W., Jullien, G.: A method of majority logic reduction for quantum cellular automata. IEEE Trans. Nanotechnol. 3, 443–450 (2004)

Hänninen, I., Takala, J.: Binary adders on quantum-dot cellular automata. J. Signal Process. Syst. 58(1), 87–103 (2010)

Chudasama, A., Sasamal, T.N.: Implementation of 4× 4 vedic multiplier using carry save adder in quantum-dot cellular automata. In: 2016 International conference on communication and signal processing (ICCSP), pp. 1260–1264. IEEE (2016)

Zhang, Y., Xie, G., Sun, M., Lv, H.: An efficient module for full adders in quantum-dot cellular automata. Int. J. Theor. Phys. 57(10), 3005–3025 (2018)

Mohammadyan, S., Angizi, S., Navi, K.: New fully single layer QCA full-adder cell based on feedback model. IJHPSA 5(4), 202–208 (2015)

Abdullah-Al-Shafi, M., Bahar, A.N.: Energy optimized and low complexity 2-dimensional 4 dot 2 electron flip-flop and quasi code generator in nanoscale. J. Nanoelectron. Optoelectron. 13(6), 856–863 (2018)

Abdullah-Al-Shafi, M., Bahar, A.N.: Fredkin circuit in nanoscale: a multilayer approach, international journal of information technology and computer. Science 10(10), 38–43 (2018)

Zhang, Y., Xie, G., Sun, M., Lv, H.: Design of normalised and simplified FAs in quantum-dot cellular automata. J. Eng. 1(1), 1–9 (2017)

Jaiswal, R., Sasamal, T. N.: Efficient design of full adder and subtractor using 5-input majority gate in QCA. In: 10th International conference on contemporary computing, (IC3), pp. 1–6 (2017)

Heikalabad, S.R., Asfestani, M.N., Hosseinzadeh, M.: A full adder structure without cross-wiring in quantum-dot cellular automata with energy dissipation analysis. J. Supercomput. 74(5), 1994–2005 (2018)

Hanninen, I., Takala, J: Robust adders based on quantum-dot cellular automata. In: 2007 IEEE international conf. on application-specific systems, architectures and processors (ASAP), pp. 391–396 (2007)

Ahmad, F., Bhat, G.M., Khademolhosseini, H., Azimi, S., Angizi, S., Navi, K.: Towards single layer quantum-dot cellular automata adders based on explicit interaction of cells. J. Comput. Sci. 16, 8–15 (2016)

Abdullah-Al-Shafi, M., Bahar, A.N.: A new structure for random access memory using quantum-dot cellular automata. Sensor Lett. 17(7), 595–600 (2019)

Abdullah-Al-Shafi, M., Rahman, Z.: Analysis and modeling of sequential circuits in QCA nano computing: RAM and SISO register study. Solid State Electron. Lett. 1(2), 73–83 (2019)

Abdullah-Al-Shafi, M., Bahar, A.N., Bhuiyan, M.M.R., Shamim, S.M., Ahmed, K.: Average output polarization dataset for signifying the temperature influence for QCA designed reversible logic circuits. Data Brief 19, 42–48 (2018)

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no potential conflict of interest in the manuscript.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Abdullah-Al-Shafi, M., Islam, M.S. & Bahar, A.N. 5-Input majority gate based optimized full adder circuit in nanoscale coplanar quantum-dot cellular automata. Int Nano Lett 10, 177–195 (2020). https://doi.org/10.1007/s40089-020-00304-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40089-020-00304-y