Abstract

This paper presents a low power, wide-tuned Inductor-capacitor (LC) voltage-controlled oscillator (VCO). A floating active inductor (FAI) with a high-quality factor (Q) is used in the VCO design. The FAI is designed with a cascode transistor pair and a cross-coupled transistor pair to achieve a high Q value of up to 3290. The inductance value of the FAI ranges from 12.5 nH to 256.2 nH. The VCO has 164.8% of oscillation frequency tuning, from 235 MHz to 2.83 GHz with a phase noise of −85.3 dBc/Hz to −102.4 dBc/Hz at 1 MHz offset frequency. The FAI and VCO have 17.1 × 18 µm2 and 58.6 × 64.6 µm2 silicon area respectively. The power consumption ranges from 6.8 mW to 8.62 mW within the frequency tuning range. The FAI and VCO are designed in UMC 0.18 µm mixed-mode CMOS technology.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

Today the world demands new technologies such as the Internet of Things (IoT), cognitive radio, etc. The connectivity among the devices in these technologies are mostly the very popular short-range wireless standards such as Bluetooth (IEEE 802.15.1), Wi-Fi (IEEE 802.11b/g/n), LTE (Long Term Evolution) in L Band and lower C Band in mobile phones and other devices. To support all these standards in one radio frequency integrated circuit (RFIC) [1], a device needs multiple fixed narrowband RF transceiver chips [2]. But this consumes more power and area, at a very high cost. The alternative solution is a single-chip reconfigurable RF transceiver supporting multiple wireless standards with more effective hardware sharing [3]. A voltage-controlled oscillator (VCO) is responsible for signal generation with different frequencies and reconfiguration in the context of frequency synthesis and clocking in the transceiver.

In the current scenario, the industry demands wideband, reconfigurable, low area, low power, and cost-effective VCO with reasonable phase noise. VCOs are classified as (i) ring (relaxation) VCO, well-known for their wide tuning range, low power, and low area, (ii) LC (harmonic) VCO [4] better known for its low phase noise. The tuning capability of the LC VCOs is enhanced using variable capacitors and tunable on-chip passive inductors [5]. Although the tunable passive inductors have a high Q value, they require isolation from the neighboring elements to avoid electromagnetic interference consuming much more area and it makes the chip design complex and costly. Implementing active inductors (AIs) is the best way to get rid of these issues as they have tunable and high-valued quality factors and inductance. Both quantities are dependent on the transistor parameters, used for the realization of AI. The transistor parameters can be varied by changing the biasing conditions of the transistors which in turn tune the AI properties. At the same time, AIs suffer from noise, non-linearity, and power consumption issues. Nonlinearity and power consumption can be reduced to a greater extent with the proper design of the AI, but the noise needs to be compromised. So as a measure of performance generally the Figure of Merit (FoM) is calculated for the VCO which will be discussed later in this paper.

In this work, the design of a high-Q floating active inductor (FAI) and its use in a reconfigurable multiband VCO for a broad range of wireless applications is presented. The subsequent sections are presented as follows: Section II highlights the basic principles of the AI and the VCO using AI. Section III presents the proposed design of FAI and the design of VCO. The post-layout simulation results are discussed in Section IV, and the entire work is concluded in Section V.

Basics of Active Inductor and VCO

The current trend in RFIC is to make smaller ICs without compromising their performance. In this way, the active components are replaced by their passive on-chip counterparts. Here we address the fundamentals of AI and VCO using the active elements.

Active Inductor

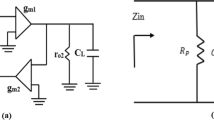

AIs are basically of self-biased type [6], boot-strapped type [7], and gyrator-C type [8, 9] as shown in Fig. 1. The self-biased type of AI (Fig. 1a) has low- Q but provides a high voltage swing with the least area and power consumption. It suffers from voltage headroom issues. The boot-strapped AI (Fig. 1b) has a transformer for its realization making it bulky. It exploits the current amplification between two spirals of the integrated transformer and enhances the equivalent inductance value as seen from the input of AI as well as the Q-value. The inductance is proportional to the amplification of the transconductance stage. It is suitable for very high frequency, such as millimeter-wave applications. The most popular one is the gyrator-C AI (Fig. 1c), due to its high Q value, high inductance value, and wide frequency range. It consists of two transconductors, one positive and one negative, connected back-to-back.

The equivalent circuit of AI consists of a parallel R-L-C network, comprising the parasitic resistances and capacitances of the active devices. These parasitics reduce the Q-value of the AI. Different circuit topologies, namely, cascode structures [10], feedback structures [11,12,13,14], and negative resistance structures [15, 16] are incorporated in the basic gyrator-C AI circuit to improve the Q-value.

AIs are categorized into single-ended AI (SAI) [16] and floating AI (FAI) [10, 17, 18]. The FAI has certain advantages over SAI like the voltage swing can be made double that in SAI and if the FAI has a symmetrical structure, it can reject the common-mode disturbances and becomes more suitable to be used in the VCOs. The SAI [16] has a cascode structure and a cross-coupled structure that provide negative resistance to compensate for the parasitic losses in the circuit, thereby improving its Q value.

Low power, wideband, differential input differential output operational transconductance amplifiers (OTAs) have been used in [10] to realize the FAI. The FAI [12, 19] has an additive capacitor technique with the transistors operating in the sub-threshold region by reducing the operating currents and so the power consumption. But it affects the frequency tuning range and the frequency of oscillation. A regulated cascode structure in addition to resistive feedback configuration is used to implement the FAI [20]. The regulated cascode structure reduces the series resistance loss to improve the quality factor of the FAI. But the use of the feedback resistance introduces thermal noise in the circuit.

Voltage Controlled Oscillator

The most popular LC VCOs used in the RFICs are Hartley VCO [21], Colpitts VCO [22], and cross-coupled VCO [11]. Cross-coupled VCOs are focused in this paper. Figure 2 shows the conventional top-biased cross-coupled LC VCO [23]. It consists of an LC tank and a core (a cross-coupled pair of nMOS transistors) which provides negative resistance to compensate for the loss introduced by the LC tank circuit.

The current trend in RFICs is the massive use of active elements to save die area. The passive capacitors are replaced by MOS varactors such as inversion mode MOS transistors (IMOS) or accumulation mode MOS transistors (AMOS) [24] or capacitor banks [25]. One of the major problems of using a passive inductor in VCO (Fig. 2) is that it is very difficult to predict the resistances associated with passive inductors like RL1 and RL2, and so to design the negative resistance circuit (M1, M2). One of the possible solutions is to replace the passive inductors with active inductors.

In [17], SAI is used in the VCO design which is connected to the supply. But this type of design introduces the noise from the supply in the circuit. To avoid this, the current source is placed in between the inductor and the supply. FAI is used in the VCO design [19] along with AMOS as the varactor. A wider transistor of the AMOS can result in higher frequency tuning. The voltage swing of the oscillator is maintained by the circuit itself as the increase in controlled voltage of the FAI is taken care of by the voltage headroom of the constituent transistors. In addition to the buffer, the circuits can also be used at the VCO outputs for a better output.

Design of Proposed FAI and VCO

Proposed FAI

The proposed FAI as shown in Fig. 3 is used for a bandpass filter realization in sub-GHz applications [26]. A cascode transistor structure and a cross-coupled transistor pair [27] are used for its realization. The widths of transistors are also modified for high-frequency applications. Here, compensation of parasitic resistance present in the FAI is discussed through a more detailed analysis of the half symmetry small-signal equivalent circuit of FAI as shown in Fig. 4. In this case, Cgsi, Cgdi, and gmi are the gate to source capacitance, the gate to drain capacitance, and the transconductance of transistors Mi (i = 1, 2, 3, 4), respectively. The derived input impedance from the small-signal equivalent circuit between the terminals LP/LM and the ground is given in (1).

The (1) can be represented in the form of (2) to match the equivalent circuit of the FAI as shown in Fig. 5.

Different parameters of the FAI such as inductance (Lse), negative parallel resistance in the circuit due to the cross-coupled transistor structure (Rnpl), parallel capacitance (Cpl), equivalent parallel resistance of RS (Req), self-resonant frequency (ω0) and Q are derived from (1), in-line with [8] and [28], also presented in (3) to (9).

When Rnpl is equal to Req there is no loss in the FAI. So the condition for the FAI to be lossless is

Taking Cgs3 = 5.22 fF, Cgs1 = 5.35 fF, Cgs4 = 7.15 fF, gm3 = 0.476 mS, gm1 = 0.466 mS, and, gm4 = 1.517 mS for VB = 1.2 V and VCON = 847 mV, it may be noted that the left-hand side and right-hand side of (10) are almost equal. This shows the nullification of parasitic resistance associated with the FAI. Further, the channel noise (both thermal and Flicker noise) of the transistors (as shown in Fig. 4) is only considered to calculate the input-referred noise spectral density of the FAI. The small signal analysis leads to the following set of equations

where

If Vn is the input-referred noise voltage at the terminal LP (LM) then it can be expressed as

where Vni is the input-referred noise spectral density due to the individual transistor given as:

where \(i_{ni}\) is the channel noise of the transistor Mi, consisting of thermal noise and flicker noise, represented as

where k = Boltzmann’s constant, T = absolute temperature, γ is technology-dependent constant, Cox is gate oxide capacitance, Kf is flicker noise co-efficient, AF is the flicker noise exponent, and gd0 is the drain-source conductance at zero Vds. Thus,

Proposed VCO

The flicker noise minimization using a top-biased approach is presented to improve the VCO phase noise [29]. Based on this design, Fig. 6 shows the proposed VCO, in which the passive inductors are replaced by the proposed FAI (Fig. 3). The variable capacitors (C3, C4) are designed with the accumulation MOS Transistor pair (AMOS) varactors, and the current source is implemented by a current mirror. In the proposed VCO, the transistor M11 acts as a resistor and is solely responsible for the current flow in the VCO. The capacitance C is used to cancel the noise raised from the higher-order harmonics. The small resistances R1 and R2 are used for biasing the FAIs. The top-biased approach [30] is followed here to improve the VCO phase noise. By doing so, less flicker noise is upconverted to phase noise as compared to other techniques. But the amplitude of the VCO output is less due to the loss arising from the resonator loading.

Figure 7a shows the equivalent R-L-C circuit of the proposed VCO. The equivalent half circuit of Fig. 7a with the negative resistance of the core is shown in Fig. 7b. The VCO resonant frequency can be presented as

where \(L_{tank} = 2L_{se} \left( {1 + {\raise0.7ex\hbox{$1$} \!\mathord{\left/ {\vphantom {1 {Q_{eff}^{2} }}}\right.\kern-0pt} \!\lower0.7ex\hbox{${Q_{eff}^{2} }$}}} \right)\) and \(C_{tank} = \left( {2C\parallel CC_{1} \parallel C_{pl} \parallel C_{xcp} } \right)\). \(C_{xcp}\) is the equivalent capacitance due to the cross-coupled circuit as seen from the tank circuit. The quality factor of the LC tank is represented as

Here, gtank (conductance of the tank circuit) is the reciprocal of R1 or R2 as FAI has negligible parasitic resistance and Itail is the current through the transistor MP5. The coarse tuning of the oscillation frequency is obtained by varying the value of the control voltages VB and VCON of the FAI, whereas fine-tuning of the oscillation frequency is achieved by capacitance variation of AMOS varactors through VCAP voltage variation. The calculated values of the resistances and capacitances of the proposed VCO are R1 = R2 = 16 Ω, C1 = C2 = 250 fF, and C3 = 32 fF.

Table 1 presents the calculated width of all transistors keeping the minimum length of the transistors at 0.18 µm. The phase noise in an LC VCO arises normally due to the tank circuit. In this case, the incorporation of the FAI in VCO added extra phase noise to the circuit. So, the total phase noise can be presented as

The first term in (16) is due to the tank circuit, which is based on the well-known Leeson’s Formula. The second term is contributed by the FAI where \({\Gamma }_{rms}^{2}\) is the impulse sensitivity function of the VCO and \({(i}_{n}^{2}/\Delta f)\) is the sum of the current noises of the active parts of the FAI. It can be noted that the incorporation of FAI in VCO results in area reduction and reduction of the up-converted 1/f noise of the cross-coupled structure, due to the highly symmetric nature of FAI. The 1/f noise can be further reduced by switching the transistors between inversion and accumulator regions at regular intervals of time [30].

Post Layout Simulation Results and Discussion

The proposed FAI and VCO are simulated in spectre-RF simulator of Cadence (IC6.1.6) software, using UMC 0.18 µm mixed-mode CMOS technology. The corresponding layout, as shown in Fig. 8, consumes an area of 58.6 × 64.6 µm2, with each of the FAIs occupying an area of 17.1 × 18 µm2. The XCP in the layout represents the cross-coupled transistor pair.

For all nMOS transistors, the substrates are connected to the ground and for all pMOS transistors, the substrates are connected to the supply. Metal–Insulator-Metal capacitors (MIM-CAP) are used in the VCO design to avoid the mutual inductance between the plates. As poly resistors contribute less noise as compared to other on-chip resistors, they are also used in this design.

Figure 9 indicates that the simulated inductance value of FAI ranges from 12.5 nH to 256.2 nH and the self-resonance frequency from 3 GHz to 7.18 GHz. These values correspond to a range of control voltage VB from 1.2 V to 1.45 V and VCON from 760 mV to 1 V. The straight-line portion of the curves indicates that the AI is completely stable, frequency-independent with a constant inductance value, and after that, it is marginally stable and frequency-dependent up to the resonant frequency. After the resonating frequency, the structure does not behave as an inductor rather it shows a capacitive behavior.

Figure 10 shows the maximum Q value of FAI as 3290. The maximum Q values at 1.9 GHz and 2.4 GHz are nearly 1900. The above values are obtained by biasing the two control voltages VB = 1.2 V and VCON = 905 mV for 1.9 GHz and VB = 1.2 V and VCON = 847 mV for 2.4 GHz. The Q-values at a particular frequency can be varied by changing the current through the FAI. Table 2 summarizes the simulated inference of the proposed FAI.

The coarse tuning of the frequency of oscillation of VCO is shown in Fig. 11a. The tuning range for which the frequency varies linearly is found to be 235 MHz to 2.83 GHz corresponding to VCON value 830 mV to 1.08 V. It is observed that the frequency of oscillation reduces as VCON increases. Figure 11b shows the fine-tuning curves for the frequency of the two popular bands of 1.9 GHz and 2.4 GHz. It is noticed that the frequency of oscillation increases in proportion to voltage VCAP in the range of 1.09 V to 1.3 V beyond which the curve is non-linear. The VCO gain (KVCO) is found to be 646 MHz/V concerning the voltage VCAP.

The noise characteristics curve of FAI is shown in Fig. 12. The input-referred noise of the FAI is found to be 7.9 nV/Hz at 2.4 GHz frequency and the noise corner frequency is less than 200 Hz. The best phase noise of the proposed VCO varies from −85.3 dBc/Hz to −102.4 dBc/Hz at 1 MHz offset frequency (Fig. 13) for a center frequency range of 1.7G to 2.6 GHz. The phase noise is found to be −93.7 dBc/Hz and −92.4 dBc/Hz at center frequencies of 1.9 GHz and 2.4 GHz respectively.

Figure 14a shows the effect of process and temperature variation on the frequency of oscillation. It is observed that for the FNSP and SNFP process corners, the frequency difference is more than 40%. Figure 14b shows the phase noise plot with the process and temperature variation at 1 MHz offset frequency for a center frequency of 2.4 GHz. The difference between the extreme corners FNSP and SNFP is around 8 dBc/Hz with 5.1% variation throughout the temperature range of −40 °C to 125 °C. Due to both process tolerance and component mismatch, there is quite a high difference in the frequency result. Hence, the Monte-Carlo simulation is further performed for the stability issue.

Figure 15a and b show the Monte-Carlo simulation results for the two frequency bands 1.9 GHz and 2.4 GHz. The simulation is performed by taking 1000 samples with σ = 3 and taking VCON as the global parameter of values 905 mV and 847 mV respectively. The mean frequencies are found to be 2.02 GHz and 2.41 GHz with the Gaussian distribution for the band 1.9 GHz and 2.4 GHz respectively.

The total power consumed by the VCO for different values of the control voltages VB and VCON is shown in Fig. 16. The minimum power consumed for VB = 1.2 V, VCON = 1 V, which is 6.28 mW, and the maximum power consumed for VB = 1.45 V, VCON = 760 mV, which is 8.62 mW. Table 3 presents the comparison of the proposed work with related works.

The proposed VCO requires an area of 0.0038 mm.2 in 0.18 µm technology without the I/O pads. It has the lowest gain of 646 MHz/V and has a phase noise of -102.4 dBc/Hz for a center frequency of 2.47 GHz at an offset frequency of 1 MHz. The Figure of merit (FoM) of the VCO can be calculated by [3]

where L is the phase noise, PDC is the power consumption, fosc is the frequency of oscillation, and foffset is the offset frequency at which the phase noise is measured. Using (17) the FOM is calculated to be −160.64.

It may be noted that in comparison to other designs reported in Table 3, the proposed design has better phase noise and VCO gain performance. Considering the overall performance of all designs from FOM it is found that our proposed VCO is more promising as compared to others.

Conclusions

A low-power wideband cross-coupled LC VCO is designed with the proposed high-Q FAI. The maximum power consumed by the VCO is 8.6 mW with a reasonable phase noise of −92.4 dBc/Hz for 1.9 GHz and −93.7 dBc/Hz for 2.4 GHz at an offset frequency of 1 MHz. The proposed VCO has a tuning range of 235 MHz to 2.83 GHz, that covers the whole L-band and lower C-band. It can be used in DECT, advanced wireless services (AWS-2), fixed microwave services, Bluetooth™, Wi-Fi, and unlicensed part 15 devices. This research work is part of a frequency synthesizer using a phase lock loop (PLL) of a transceiver architecture. After completion of the entire design, we will go for real-world implementation after due fabrication and subsequent testing.

References

L.E. Larson, Integrated circuit technology options for RFICs-present status and future directions. IEEE J. Solid-State Circuits 33(3), 387–399 (1998)

F. Herzel, H. Erzgraber, N. Ilkov, A new approach to fully integrated CMOS LC-oscillators with a very large tuning range, in Proceedings of the IEEE 2000 Custom Integrated Circuits Conference, (IEEE, Orlando, FL, USA, 2000), pp. 573–576

F. Haddad, I. Ghorbel, W. Rahajandraibe, Design of reconfigurable inductorless RF VCO in 130 nm CMOS. BioNanoScience 9(2), 285–295 (2019)

K.A. Karthigeyan, S. Radha, Single event transient study on PMOS-NMOS cross-coupled LC-VCO using PLL. Int. J. Electron. 108(3), 378–394 (2020)

D.R. Pehlke, A. Burstein, M.F. Chang, Extremely high-Q tunable inductor for Si-based RF integrated circuit applications, in International Electron Devices Meeting. IEDM Technical Digest, (IEEE, Washington, DC, USA, 1997), pp. 63–66

F. Yuan, A fully differential VCO cell with active inductor load for GBPS serial links, in The 3rd International IEEE-NEWCAS Conference, 2005, (IEEE, Quebec, QC, Canada, 2005), pp. 183–186

D. Zito, D. Pepe, A. Fonte, High-frequency CMOS active inductor: design methodology and noise analysis. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 23(6), 1123–1136 (2015)

F. Yuan, CMOS Active Inductors and Transformers (Springer, New York, 2008)

D.M. Zaiden, J.E. Grandfield, T.M. Weller, G. Mumcu, Compact and wideband MMIC phase shifters using tunable active inductor-loaded all-pass networks. IEEE Trans. Microw. Theory Tech. 66(2), 1047–1057 (2018)

J. Xu, C.E. Saavedra, G. Chen, An active inductor-based VCO with wide tuning range and high DC-to-RF power efficiency. IEEE Trans. Circuits Syst. II Express Br. 58(8), 462–466 (2011)

C.H. Chun et al., Compact wideband LC VCO with active inductor harmonic filtering technique. Electron. Lett. 47(3), 190 (2011)

G. Szczepkowski, G. Baldwin, R. Farrell, Wideband 0.18 μm CMOS VCO using active inductor with negative resistance, in 2007 18th European Conference on Circuit Theory and Design, (IEEE, Seville, Spain, 2007), pp. 990–993

H.B. Kia, A.K. A’ain, A wide tuning range voltage controlled oscillator with a high tunable active inductor. Wirel. Pers. Commun. 79(1), 31–41 (2014)

S. Singh, R. C. Gurjar, A low power, low phase noise VCO using cascoded active inductor, in 2017 International Conference on Information, Communication, Instrumentation and Control (ICICIC). (IEEE, Indore, India, 2017)

L.-H. Lu, H.-H. Hsieh, Y.-T. Liao, A wide tuning-range CMOS VCO with a differential tunable active inductor. IEEE Trans. Microw. Theory Tech. 54(9), 3462–3468 (2006)

M.M. Reja, I.M. Filanovsky, K. Moez, Wide tunable CMOS active inductor. Electron. Lett. 44(25), 1461–1463 (2008)

Y.-J. Jeong, Y.-M. Kim, H.-J. Chang, T.-Y. Yun, Low-power CMOS VCO with a low-current, high-Q active inductor. IET Microw. Antennas Propag. 6(7), 788–792 (2012)

R. Mehra, V. Kumar, A. Islam, Floating active inductor based class-C VCO with 8 digitally tuned sub-bands. AEÜ Int. J. Electron. Commun. 83, 1–10 (2018)

A.K. Hota, K. Sethi, Pseudo-differential active inductor-based modified gilbert cell mixer. Iran. J. Sci. Technol. Trans. Electr. Eng. 46(1), 245–256 (2021)

O. Faruqe, A.I. Lim, M.T. Amin, Tunable active inductor based VCO and BPF in a single integrated design for wireless applications in 90 nm CMOS process. Eng. Rep. 2(8), e12220 (2020)

M. Mehrabian, A. Nabavi, N. Rashidi, A 4∼7GHz ultra wideband VCO with tunable active inductor, in 2008 IEEE International Conference on Ultra-Wideband. (IEEE, Hannover, Germany, 2008), pp. 21–24

R. Mukhopadhyay et al., Reconfigurable RFICs in Si-based technologies for a compact intelligent RF front-end. IEEE Trans. Microw. Theory Tech. 53(1), 81–93 (2005)

T.H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, 2nd edn. (Cambridge University Press, Cambridge, UK, 2004)

P. Andreani, S. Mattisson, On the use of MOS varactors in RF VCOs. IEEE J. Solid-State Circuits 35(6), 905–910 (2000)

T. Ding, X. Fan, D. Zhao, Ka-band wideband VCO with LC filtering technique in 65-nm CMOS. Electron. Lett. 55(10), 581–583 (2019)

A.K. Hota, K. Sethi, Design of 635 MHz bandpass filter using high-Q floating active inductor, in Communications in Computer and Information Science. (Springer, Singapore, 2019), pp.115–125

K. Kimura, Some circuit design techniques using two cross-coupled, emitter-coupled pairs. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 41(5), 411–423 (1994)

M.M. Reja, “Design of Active CMOS Multiband Ultra-Wideband Receiver Front-End (University of Alberta, Edmonton, AB, Canada, 2011)

B. De Muer, M. Borremans, M. Steyaert, G. Li Puma, A 2-GHz low-phase-noise integrated LC-VCO set with flicker-noise upconversion minimization. IEEE J. Solid State Circuits 35(7), 1034–1038 (2000)

I. Bloom, Y. Nemirovsky, 1/f noise reduction of metal-oxide-semiconductor transistors by cycling from inversion to accumulation. Appl. Phys. Lett. 58(15), 1664–1666 (1991)

Funding

No funds, grants, or other support was received.

Author information

Authors and Affiliations

Contributions

All authors contributed equally to the study conception and design. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors have no conflict of interest to declare that are relevant to the content of this article.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Hota, A.K., Sethi, K., Sooksood, K. et al. A High-Q Floating Active Inductor Based VCO for L-Band and Lower C-Band Applications in 180 nm CMOS Technology. J. Inst. Eng. India Ser. B 104, 1023–1033 (2023). https://doi.org/10.1007/s40031-023-00910-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40031-023-00910-2