Abstract

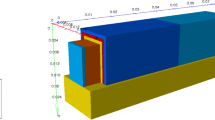

The fabrication complexity, leakage current, low-power operation, and cost of nano-scale devices are major concerns. To address these challenges, we propose a dual oxide-based approach to enhance the performance of the dual oxide electrically doped junction-less tunnel field-effect transistor (DO-ED-JL-TFET). For this purpose, the oxide layer (\(T_{ox}\)) is vertically segmented into two sections. The lower section comprises \(\mathrm {SiO_{2}}\) (low-K dielectric), while the upper section incorporates \(\mathrm {HfO_{2}}\) (high-K dielectric). This segmentation enhances the capacitive coupling between the gate and channel area, resulting in a reduced tunneling width near the source-channel region. Moreover, a polarity gate bias (electrically doped) of PG = -1.2 V is applied to create a P\(^{+}\) source region over the thin silicon body. The proposed device addresses challenges such as random dopant fluctuation, thermal budget, and fabrication complexity issues compared to conventional TFETs. The performance of the proposed device has been assessed in terms of variations in carrier concentrations, electric field, energy band diagram, transfer (I\(\mathrm {_{ds}}\) - V\(\mathrm {_{gs}}\)) characteristics, subthreshold swing (SS), and switching ratio (I\(\mathrm {_{on}}\)/I\(\mathrm {_{off}}\)). Moreover, analog/RF performance parameters such as transconductance (g\(_{m}\)), cutoff frequency (f\(\mathrm {_{T}}\)), and gain bandwidth product (GBP) are also analyzed and compared with conventional ED-JL-TFET. Furthermore, the impact of trap charges at the oxide-semiconductor interface on device performance is investigated for reliability. Simulated results demonstrate that DO-ED-JL-TFET exhibits greater immunity to various types of ITCs compared to conventional ED-JL-TFET, making it a more reliable choice for applications in radioactive environments.

Article PDF

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

Availability of data and materials

Data and documents pertaining to the manuscript may be made accessible upon request.

References

Colinge JP (2008) FinFETs and other multi-gate transistors. Springer, New York, USA

Sharma D, Vishvakarma SK (2013) Precise analytical model for short channel Cylindrical Gate (CylG) Gate-ALL-Around (GAA) MOSFET. Solid State Electron 86:68–74

Sharma D, Vishvakarma SK (2013) Precise Analytical Model for Short Channel Quadruple Gate-All-Around MOSFET. IEEE Trans Nanotechnol 12(3):378–385

Kim SH, Yokoyama M, Nakane R, Ichikawa O, Osada T, Hata M, Takenaka M, Takagi S (2014) High-performance tri-gate extremely thin-body in as-on-insulator MOSFETs with high short channel effect immunity and Vth tunability. IEEE Trans Electron Devices 61(5):1354–1360

Kumar MJ, Maheedhar M, Varma PP (2015) Bipolar I-MOS an impact-ionization MOS with reduced operating voltage using the open-base BJT configuration. IEEE Trans Electron Devices 62(12):4345–4348

Hur J, Moon DI, Choi JM, Seol ML, Jeong US, Jeon CH, Choi YK (2015) A core compact model for multiple-gate junctionless FETs. IEEE Trans Electron Devices 62(7):2285–2291

Seabaugh AC, Zhang Q (2010) Low-voltage tunnel transistors for beyond CMOS logic. Proc IEEE 98(12):2095–2110

Krishnamohan T, Kim D, Raghunathan S, Saraswat KC (2008) Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and 60 mV/dec subthreshold slope, in Proc. IEDM Tech. Dig., San Francisco, CA, USA, 2008, pp. 947–949

Wang PF, Hilsenbeck K, Nirschl T, Oswald M, Stepper C, Weis M, Landsiedel DS, Hansch W (2004) Complementary tunneling transistor for low power application. Sold-State Electron 48(12):2281–2286

Boucart K, Ionescu AM (2007) Double gate tunnel FET with high k gate dielectric. IEEE Trans Electron Devices 54(7):1725–1733

Goswami PP, Khosla R, Bhowmick B (2019) RF analysis and temperature characterization of pocket doped L-shaped gate tunnel FET. Appl Phys A 125:733. https://doi.org/10.1007/s00339-019-3032-8

Dharmender and K. Nigam (2020) Low-K dielectric pocket and work function engineering for DC and analog/RF performance improvement in dual material stack gate oxide double gate TFET. SILICON 13:2347–2356. https://doi.org/10.1007/s12633-020-00822-6

Nigam K, Kondekar P, Sharma D (2016) DC characteristics and analog/RF performance of novel polarity control GaAs-Ge based tunnel field effect transistor. Superlattices Microstruct 92:224–231

Dharmender Nigam K, Yadav P, Kumar A (2023) Investigation of \(Si_{1-X}Ge_{X}\) Source Dual Material Stacked Gate Oxide Pocket Doped Hetero-Junction TFET for Low Power and RF Applications. Int J Electron. https://doi.org/10.1080/00207217.2023.2173804

Howldar S, Balaji B, Rao KS (2023) Design and analysis of hetero dielectric dual material gate underlap spacer tunnel field effect transistor. IJE TRANSACTIONS C: Aspects 36:2137–2144

Talukdar J, Rawat G, Mummaneni K (2020) A novel extended source TFET with \(\delta \)p\(^+\) - SiGe layer. Silicon 12:2273–2281

Raad B, Nigam K, Sharma D, Kondekar P (2016) Dielectric and work function engineered TFET for ambipolar suppression and RF performance enhancement. Electron Letter 52:770–772

Garg S, Saurabh S (2018) Suppression of ambipolar current in tunnel FETs using drain-pocket: proposal and analysis. Superlattices Microstruct 113:261–270. https://doi.org/10.1016/j.spmi.2017.11.002

Hraziia A, Andrei C, Vladimirescu A, Amara A, Anghel C (2012) An analysis on the ambipolar current in Si double-gate tunnel FETs. Solid-State Electron 70:67–72

Vijayvargiya V, Vishvakarma SK (2014) Effect of drain doping profile on double-gate tunnel field-effect transistor and its influence on device RF performances. IEEE Trans. Nanotechnology 13:978–981

Damrongplasit N, Shin C, Kim SH, Vega RA, King Liu T-J (2011) Study of random dopant fluctuation effects in germanium-source tunnel FETs. IEEE Trans Electron Devices 58:3541–3548

Ghosh B, Akram MW (2013) Junctionless tunnel field effect transistor. IEEE Electron Device Letter 34:584–586

Kumar MJ, Janardhanan S (2013) Doping-less tunnel field effect transistor: design and investigation. IEEE Trans Electron Devices 16:3285–3290

Nigam K, Kondekar P, Sharma D, Raad BR (2016) A new approach for design and investigation of junction-less tunnel FET using electrically doped mechanism. Superlattices and Microstructure 98:1–7

Sahu C, Singh J (2014) Charge-plasma based process variation immune junctionless transistor. IEEE Electron Device Lett 35(3):411–413

Kondekar PN, Nigam K, Pandey S, Sharma D (2017) Design and analysis of polarity controlled electrically doped tunnel FET with bandgap engineering for analog/RF applications. IEEE Trans Electron Devices 64(2):412–418

Goswami PP, Bhowmick B (2019) Optimization of Electrical Parameters of Pocket Doped SOI TFET with L-Shaped Gate. SILICON 12:693–700. https://doi.org/10.1007/s12633-019-00169-7

ATLAS device simulation software (2015) Silvaco Int. Santa Clara, CA USA

Shen C, Yang LT, Samudra G, Yeo YC (2011) A new robust non-local algorithm for band-to-band tunneling simulation and its application to Tunnel-FET. Solid State Electron 57:23–30

Zervas M, Sacchetto D, Micheli GD, Leblebici Y (2011) Top-down fabrication of very-high density vertically stacked silicon nanowire arrays with low-temperature budget. Microelectron Eng 88:3127–3132

Marchi MD, Sacchetto D, Frache S, Zhang J, Gaillardon PE, Leblebici Y, Micheli GD (2012) Polarity control in double-gate, gate-all-around vertically stacked silicon nanowire FETs, In Proc. IEEE Electronic Device Meeting(IEDM) 8.4.1–8.4.4

Joshi T, Singh Y, Singh B (2020) Extended-Source Double-Gate Tunnel FET With Improved DC and Analog/RF Performance. IEEE Trans Electron Devices 67:1873–1879. https://doi.org/10.1109/TED.2020.2973353

Nigam K, Dharmender Tikkiwal VA, Bind MK (2023) Theoretical investigation of dual material stacked gate oxide-source dielectric pocket TFET based on interface trap charges and temperature variations. Journal of Circuits, Systems, and Computers 32:2350252. https://doi.org/10.1142/S0218126623502523

Ahish S, Sharma D, Vasantha MH, Kumar YBN (2016) Device and circuit level performance analysis of novel InAs/Si heterojunction double gate tunnel field effect transistor. Superlattices Microstruct 94:119–130. https://doi.org/10.1016/j.spmi.2016.04.008

Lim TC, Bernard E, Rozeau O, Ernst T, Guillaumot B, Vulliet N, Buj-Dufournet C, Paccaud M, Lepilliet S, Dambrine G, Danneville FÇ (2009) Analog/RF performance of multichannel SOI MOSFET. IEEE Trans Electron Devices 56(7):1473–1482

Chandan BV, Nigam K, Sharma D, Pandey S (2018) Impact of Interface Trap Charges on dopingless tunnel FET for enhancement of linearity characteristics. Appl Phys A 124:503

Madan J, Chaujar R (2016) Interfacial charge analysis of heterogeneous gate dielectric-gate all around-tunnel FET for improved device reliability. IEEE Trans Device Mater Reliab 16(2):227–234

Fan ML, Hu VPH, Chen YN, Su P, Chuang CT (2013) Analysis of single-trap-induced random telegraph noise and its interaction with work function variation for tunnel FET. IEEE Trans Electron Devices 60:2038–2044

Jiao GF et al (2009) New degradation mechanisms and reliability performance in tunneling field effect transistors. Proc. IEEE IEDM, Baltimore, MD, USA, pp 1–4

Singh P, Yadav DS (2021) Impact of temperature on analog/RF, linearity and reliability performance metrics of tunnel FET with ultra–thin source region. Appl Phys A 127:671. https://doi.org/10.1007/s00339-021-04813-1

Nigam K, Kumar S, Dharmender (2022) Temperature sensitivity analysis of dual material stack gate oxide source dielectric pocket TFET. J Comput Electron 21:802–813. https://doi.org/10.1007/s10825-022-01902-z

Acknowledgements

Not applicable

Funding

The authors affirm that they did not receive any financial resources, grants, or other forms of assistance during the process of preparing this paper.

Author information

Authors and Affiliations

Contributions

1. Bandi Venkata Chandan: Resource, Simulations, preparation of the Manuscript 2. Dharmender: Drafting and Formal Analysis 3. Kaushal Nigam: Concept and Methodology

Corresponding author

Ethics declarations

Competing interests

No Competing of interests

Ethics approval

The manuscript follows all the ethical standards

Consent to participate

Yes

Consent for publication

Yes

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Chandan, B.V., Dharmender & Nigam, K. A Theoretical Performance and Reliability Investigation of a Vertical Hetero Oxide Based JL-TFET under Ideal Conditions. Silicon 16, 4397–4413 (2024). https://doi.org/10.1007/s12633-024-03010-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-024-03010-y