Abstract

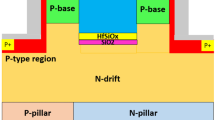

Investigation of the proposed Silicon gate all around dielectric window spaced-multi-channel (Si-GAA-DWS-multi-channel) MOSFET is carried out through 3D-ATLAS TCAD simulator. The proposed device parameter has been compared with the existing devices, mainly with Silicon-Nanowire-Dielectric Pocket Packed MOSFET (Si-NW-DPP FET) and Silicon-Nanowire MOSFET (Si-NW FET). The Si-GAA-DWS-Multi-channel FET is found to be the better device than the other two structures with a threshold voltage of 0.40 V, an on current of 0.326 × 10–3 A, off current of 5.9 × 10–13 A, on/off current ratio of 5.52 × 108, sub-threshold swing of 63.4 mV/dec and DIBL of 26.25 mV/V. Impact of interface fixed charges and multi state defects have been studied for the Si-GAA-DWS-multi-channel MOSFET. Presence of fixed negative charges and multi state defects at semiconductor-oxide interface causes a step in the potential profile which results in the shift of threshold voltage, degradation of drain current, and Ion/Ioff ratio.

Article PDF

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

Data Availability

The article submitted is an original work and has neither been published in any other peer-reviewed journal nor is under consideration for publication by any other journal.

References

Mishra S, Bhanja U, Mishra GP (2019) Variation of source gate work function on the performance of dual material gate rectangular recessed channel SOI-MOSFET. Int J Numer Model Electron Networks Devices Fields 32:e2487

Wong HY, Braga N, Mickevicius RV (2018) Enhancement-mode recessed gate and cascode gate junction-less nanowire with low-leakage and high-drive current. IEEE Trans Electron Devices 65(9):4004–4008

Jena B, Dash S, Mishra GP (2016) Electrostatic performance improvement of dual material cylindrical gate MOSFET using work-function modulation technique. Superlattices Microstruct 97:212–220

Duarte JP, Choi S, Moon D, Choi Y (2011) Simple analytical bulk current model for long-channel double-gate junctionless transistors. IEEE Electron Device Lett 32(6):704–706

Ramakrishna BS, Jena B, Dash S, Mishra GP (2017) Investigation of electrostatic performance for a conical surrounding gate MOSFET with linearly modulated work function. Superlattices Microstruct 101:152–159

Jena B, Dash S, Mishra GP (2017) Effect of underlap length variation on DC/RF performance of dual material cylindrical MOS. Int J Numer Model Electron Networks Devices Fields 30:1–12

Jena B, Dash S, Mishra GP (2018) Impact of metal grain work function variability on ferroelectric insulation-based GAA MOSFET. IET Micro Nano Letters 13:1378–1381

Zhu H et al (2012) Self-aligned multi-channel silicon nanowire field-effect transistors. Solid-State Electron 78:92–96

Purwar V, Gupta R, Tiwari PK, Dubey S (2021) Investigating the impact of Self-heating Effects on some Thermal and Electrical Characteristics of Dielectric-Pocket Gate-All-Around (DPGAA) MOSFETs. SILICON 14:1–11

Kumar A, Bhushan S, Tiwari PK (2017) Analytical modeling of subthreshold characteristics of ultra-thin double gate-all-around (DGAA) MOSFETs incorporating quantum confinement effects. Superlattices Microstruct 109:567–578

Wang T, Chang T, Chiang LP, Wang CH, Zous NK, Huang C (1998) Investigation of oxide charge trapping and detrapping in a MOSFET by using a GIDL current technique. IEEE Trans Electron Devices 45(7):1511–1517

Zhao P (2018) Understanding and Engineering Surface and Edge Defects of Transition Metal Dichalcogenides. University of California, Berkeley

Cohen YN, Shappir J, Frohman-Bentchkowsky D (1985) Measurement of Fowler-Nordheim tunneling currents in MOS structures under charge trapping conditions. Solid-State Electron 28(7):717–720

Wirth GI, da Silva R, Kaczer B (2011) Statistical model for MOSFET bias temperature instability component due to charge trapping. IEEE Trans Electron Devices 58(8):2743–2751

Wang QH, Kalantar-Zadeh K, Kis A, Coleman JN, Strano MS (2012) Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat Nanotechnol 7(11):699–712

Bhol K, Jena B, Nanda U (2022) Silicon nanowire GAA-MOSFET: A workhouse in nanotechnology for future semiconductor devices. SILICON 14(7):3163–3171

Awasthi H, Kumar N, Purwar V, Gupta R, Dubey S (2021) Impact of temperature on analog/RF performance of Dielectric Pocket Gate-all-around (DPGAA) MOSFETs. SILICON 13:2071–2075

Purwar V, Gupta R, Tiwari PK, Dubey S (2022) Investigating the impact of self-heating effects on some thermal and electrical characteristics of Dielectric Pocket Gate-all-around (DPGAA) MOSFETs. SILICON 14:7053–7063

Sun Y et al (2021) The past and future of multi-gate field-effect transistors: Process challenges and reliability issues. J Semicond 42:023102

Adhikari MS, Singh Y (2017) High performance multi-channel MOSFET on InGaAs for RF amplifiers. Superlattices Microstruct 102:79–87

Lim TC et al (2009) Analog/RF performance of multichannel SOI MOSFET. IEEE Trans Electron Devices 56:1473–1482

Kumar S, Jha S (2013) Impact of elliptical cross-section on the propagation delay of multi-channel gate-all-around MOSFET based inverters. Microelectron J 44:844–851

Myeong I et al (2019) Analysis of self heating effect in DC/AC Mode in multi-channel GAA-field effect transistor. IEEE Trans Electron Devices 66:4631–4637

Ozawa O, Aoki K (1976) A multi-channel FET with a new diffusion type structure. Jpn J Appl Phys 15:171

Akbar C, Li Y, Sung WL (2021) Machine learning aided device simulation of work function fluctuation for multichannel gate-all-around silicon nanosheet MOSFETs. IEEE Trans Electron Devices 68:5490–5497

Yajula UAS, Sahoo GS, Mishra GP (2023) Dielectric-Pocket based Multi-channel Nanowire Field Effect Transistor for High-speed Operations, In proc. IEEE Devices for Integrated Circuit, pp. 100–103

Gautam R, Saxena M, Gupta RS, Gupta M (2011) Impact of interface fixed charges on the performance of the channel material engineered cylindrical nanowire MOSFET. Int J VLSI Des Commun Syst 2:225–241. https://doi.org/10.5121/vlsic.2011.2319

Silvaco ATLAS User’s Manual (2023)

Funding

None.

Author information

Authors and Affiliations

Contributions

Dr. Girija Shankar Sahoo conceived and designed the simulation and written the manuscript; Ushodaya A performed the simulation study and generated the output; Dr. Girija Shankar Sahoo, and Dr. G P Mishra modified the manuscript and analyzed the data; Dr. Guru Prasad Mishra contributed by providing the Silvaco tool; all authors reviewed the entire manuscript.

Corresponding author

Ethics declarations

Ethics Approval

For the submission of an article to “Silicon”, I hereby certify that:

a) I have been granted authorization by my co-authors to enter into these arrangements.

b) I hereby declare, on behalf of myself and my co-authors, that:

I am/we are the sole author(s) of the article and maintain the authority to enter into this agreement and the granting of rights to “Silicon” does not infringe any clause of this agreement.

c) This study does not contain any human or animal subjects for data analysis.

I hereby certify that I am authorized to sign this document in my own right. And authors declare no conflicts of interest.

Consent to Participate

All authors have been personally and actively involved in substantial work leading to the paper, and will take public responsibility for its content.

Consent for Publication

A) The manuscript submitted has been prepared according to the journal’s “Aims & Scope” and “Instructions for Authors” and checked for all possible inconsistencies and typographical errors.

b) On submission of the manuscript, the authors agree not to withdraw the manuscript at any stage prior to publication.

Competing Interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Sahoo, G.S., Ushodaya, A. & Mishra, G.P. Effect of Defects on the Switching Performance of Silicon-Gate All Around Dielectric Window Spaced-Multi-channel MOSFET. Silicon 16, 3317–3323 (2024). https://doi.org/10.1007/s12633-024-02924-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-024-02924-x