Abstract

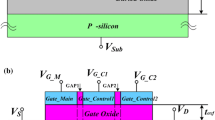

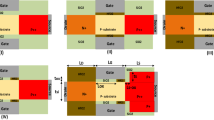

In this article, a Heterogeneous Gate-Dielectric Nanosheet Tunnel Field Effect Transistor (HD-NSH-TFET) with three channels is investigated using the 3-D Visual TCAD simulator. The HD layer of the proposed TFET consists of a high-k (HfO2) placed over the extended source and channel interface and a low-k (SiO2) at the extended drain and channel interface. An extensive comparison is outlined between the performance metrics of HD-NSH-TFET, conventional gate stack (GS)-NSH-TFET and negative capacitance nanosheet TFET(NC-NSH-TFET) configurations. The HD transistor exhibits an incredible leakage current of order 1e-18 A, while the gate stack demonstrates a leakage current of order 1e-16 A. The HD-NSH-TFET architecture ameliorates subthreshold swing (SS) and DIBL by 41.90 and 43.87 percent, respectively, over the GS structure. The HD-NSH-TFET device achieves a significant Ion/Ioff ratio (5.5e + 13), as well as an optimal subthreshold swing (13.88 mv/decade), while consuming minimal power and retaining excellent switching drivability. The effect of work function and oxide length on HD-NSH-TFET is investigated. The impact of temperature on DC and analogue parameters has been evaluated to ensure the device's reliability.

Article PDF

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

Data Availability

Not applicable.

Code Availability

Not applicable.

References

Yoon J-S, Jeong J, Lee S, Baek R-H (2018) Systematic DC/AC performance benchmarking of Sub-7-nm node FinFETs and nanosheet FETs. IEEE J Electron Devices Soc 6:942–947. https://doi.org/10.1109/jeds.2018.2866026

Nagy D, Espineira G, Indalecio G, Garcia-Loureiro AJ, Kalna K, Seoane N (2020) Benchmarking of FinFET, nanosheet, and nanowire FET architectures for future technology nodes. IEEE Access 8:53196–53202. https://doi.org/10.1109/access.2020.2980925

Pundir YP, Bisht A, Saha R, Pal PK (2022) Effect of temperature on performance of 5-nm node silicon nanosheet transistors for analog applications. SILICON. https://doi.org/10.1007/s12633-022-01800-w

Sreenivasulu VB, Narendar V (2021) A comprehensive analysis of junctionless Tri-Gate (TG) FinFET towards low-power and high-frequency applications at 5-nm gate length. Silicon 14(5):2009–2021. https://doi.org/10.1007/s12633-021-00987-8

Sreenivasulu VB, Narendar V (2022) Circuit analysis and optimization of GAA nanowire FET towards low power and high switching. SILICON. https://doi.org/10.1007/s12633-022-01777-6

BarraudS et al. (2017) Performance and design considerations for gate-all-around stacked-NanoWires FETs. 2017 IEEE International Electron Devices Meeting (IEDM). https://doi.org/10.1109/iedm.2017.8268473

Jain G, Sawhney RS, Kumar R et al (2022) Performance analysis of vertically stacked nanosheet tunnel field effect transistor with ideal subthreshold swing. Silicon 14:5067–5074. https://doi.org/10.1007/s12633-021-01302-1

Venkateswarlu S, Nayak K (2020) Hetero-interfacial thermal resistance effects on device performance of stacked gate-all-around nanosheet FET. IEEE Trans Electron Devices 67(10):4493–4499. https://doi.org/10.1109/ted.2020.3017567

Valasa S, Tayal S, Thoutam LR (2022) Optimization of design space for vertically stacked junctionless nanosheet FET for analog/RF applications. SILICON. https://doi.org/10.1007/s12633-022-01793

Dahiya AS, Sporea RA, Poulin-Vittrant G, Alquier D (2019) Stability evaluation of ZnO nanosheet based source-gated transistors. Sci Rep 9(1). https://doi.org/10.1038/s41598-019-39833-8

ChenH, Wu Y, Chang C, Han M, Lu N, Ch Y (2013) Performance of GAA Poly-Si nanosheet (2nm) channel of junctionless transistors with ideal subthreshold slope. In Symposium on VLSI Technology

Singh S, Raj B (2020) Analysis of ONOFIC technique using SiGe heterojunction double gate vertical TFET for low power applications. SILICON. https://doi.org/10.1007/s12633-020-00634-8

Choi WY, Park B-G, Lee JD, Liu T-JK (2007) Tunneling Field-Effect Transistors (TFETs) with Subthreshold Swing (SS) less than 60 mV/dec. IEEE Electron Dev Lett 28(8):743–745. https://doi.org/10.1109/led.2007.901273

Hong J, Park J, Lee J, Ham J, Park K, Jeon J (2019) Alpha particle effect on multi-nanosheet tunneling field-effect transistor at 3-nm technology node. Micromachines 10(12):847. https://doi.org/10.3390/mi10120847

Yu J et al (2019) Investigation on ambipolar current suppression using a stacked gate in an L-shaped tunnel field-effect transistor. Micromachines 10(11):753. https://doi.org/10.3390/mi10110753

Jain G, Sawhney RS, Kumar R, Wadhwa G (2021) Analytical modeling analysis and simulation study of dual material gate underlap dopingless TFET. Superlattices Microstruct 153:106866. https://doi.org/10.1016/j.spmi.2021.106866

Jain G, Sawhney RS, Kumar R (2021) Design and investigation of triple metal gate engineering of charge plasma based TFET for biomolecule detection. Mater Today Proc. https://doi.org/10.1016/j.matpr.2021.05.630

Wadhwa G, Singh J, Raj B (2020) Design and investigation of doped triple metal double gate vertical TFET for performance enhancement. SILICON 13(6):1839–1849. https://doi.org/10.1007/s12633-020-00585-0

Singh S, Nr R, Wadhwa G, Singh S (2022) Linearly work-function modulated gate metal for hetero gate dielectric TFET with Si0.5Ge0.5-pocket at source/channel junction. Silicon. https://doi.org/10.1007/s12633-021-01557-8

Kaur A, Mehra R, Saini A (2019) Hetero-Dielectric oxide engineering on dopingless gate all around nanowire MOSFET with Schottky contact source/drain. AEU-Int J Electron C 111:152888. https://doi.org/10.1016/j.aeue.2019.152888

Pindoo IA, Sinha SK, Chander S (2021) Performance analysis of heterojunction tunnel FET device with variable Temperature. Appl Phys A 127(10). https://doi.org/10.1007/s00339-021-04891-1

Loubet N et al. (2017) Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. 2017 Symposium on VLSI Technology. https://doi.org/10.23919/vlsit.2017.7998183

Genius Semiconductor Device Simulator Reference Manual

Banerjee P, Das J (2020) Gate work function engineered trigate MOSFET with a dual-material bottom gate for biosensing applications: a dielectric-modulation based approach. SILICON. https://doi.org/10.1007/s12633-020-00823-5

Dutta U, Soni MK, Pattanaik M (2018) Design & optimization of gate-all-around tunnel FET for low power applications. Int J Eng Technol 7(4):2263. https://doi.org/10.14419/ijet.v7i4.12352

PathakY, Malhotra BD, Chaujar R (2021) A numerical study of analog parameter of negative capacitance field effect transistor with spacer. 2021 7th International Conference on Signal Processing and Communication (ICSC). https://doi.org/10.1109/icsc53193.2021.9673324

Pahwa G, Agarwal A, Chauhan YS (2018) Numerical investigation of short-channel effects in negative capacitance MFIS and MFMIS transistors: subthreshold behavior. IEEE Trans Electron Devices 65(11):5130–5136. https://doi.org/10.1109/ted.2018.2870519

Abdi DB, Jagadesh Kumar M (2014) Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J Electron Devices Soc 2(6):187–190. https://doi.org/10.1109/jeds.2014.2327626

Yoon J-S, Jeong J, Lee S, Baek R-H (2018) Multi-Vth strategies of 7-nm node nanosheet FETs with limited nanosheet spacing. IEEE J Electron Devices Soc 6:861–865. https://doi.org/10.1109/jeds.2018.2859799

Chander S et al (2017) Temperature analysis of Ge/Si heterojunction SOI-Tunnel FET. Superlattices Microstruct 110:162–170. https://doi.org/10.1016/j.spmi.2017.08.048

Sahu SA, Goswami R, Mohapatra SK (2019) Characteristic enhancement of hetero dielectric DG TFET using SiGe pocket at source/channel interface: proposal and investigation. SILICON 12(3):513–520. https://doi.org/10.1007/s12633-019-00159-9

Dash S, Sahoo GS, Mishra GP (2016) Improved cut-off frequency for cylindrical gate TFET using source delta doping. Procedia Technol 25:450–455

Kamal M, Yadav DS (2021) Effects of linearity and reliability analysis for HGO-DW-SCTFET with temperature variation for high frequency application. SILICON. https://doi.org/10.1007/s12633-021-01421-9

Sahoo S, Dash S, Routray SR, Mishra GP (2020) Performance improvement of heterojunction double gate TFET with Gaussian doping. SILICON 13(12):4275–4283. https://doi.org/10.1007/s12633-020-00736-3

Yadav DS, Sharma D, Raad BR, Bajaj V (2016) Impactful study of dual work function, underlap and hetero gate dielectric on TFET with different drain doping profile for high frequency performance estimation and optimization. Superlattices Microstruct 96:36–46. https://doi.org/10.1016/j.spmi.2016.04.027

Acknowledgements

We thank the Group, department of Electronics Technology, Guru Nanak Dev University, Amritsar for their interest in this work and useful comments to draft the final form of the paper. The support of CADRE Design Systems is gratefully acknowledged. We would like to thank Guru Nanak Dev University, Amritsar and Cadre Design Systems for lab facilities and research environment to carry out this work.

Author information

Authors and Affiliations

Contributions

All authors contributed to the design and simulation. Material preparation, data collection and analysis were performed by Garima Jain, Dr. Ravinder Singh Sawhney, Dr. Ravinder Kumar and Amit Saini. The first draft of the manuscript was written by Garima Jain and all authors commented on previous versions of the manuscript. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Ethical Approval

This study was approved by the university research ethics committee. All procedures per-formed in this study follow the ethical standards of the institutional and research committee.

Research Involving Human Participants and/or Animals

Not applicable.

Consent for Publication

Yes.

Competing Interests

The authors have declared that no competing interests exist.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Jain, G., Sawhney, R.S., Kumar, R. et al. Design and Comparative Analysis of Heterogeneous Gate Dielectric Nanosheet TFET with Temperature Variance. Silicon 15, 187–196 (2023). https://doi.org/10.1007/s12633-022-02013-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-02013-x