Abstract

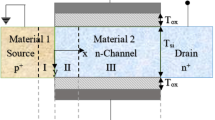

A 2-D compact analytical model for the device potential of double metal double gate hetero-oxide Tunnel FET (DM DG Hetero-oxide TFET) has been developed in this work. The hetero-oxide (HfO2 + SiO2) and the double metal double gate allows improvement in current in the ON state of TFET as well as suppresses the ambipolar current in TFET curtailing both the limitations of TFET. Parabolic approximation method with required boundary conditions has been utilized to solve Poisson’s equation. Depletion region plays vital role in altering the potential of device in its proximity. Therefore, the depletion regions at drain and source are also considered for the modeling of the device. For this the effect of fringing field has been considered using the technique of conformal mapping in the depletion regions. The incorporation of the depletion region in potential modeling allows a precise modeling of the potential near channel-drain and source-channel junctions. The model results considering source and drain depletion region shows better match with simulation results. Validation of proposed model has done against simulation data using ATLAS TCAD SILVACO software. The compact analytical model developed here is found to have good agreement with the simulation framework.

Article PDF

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

Availability of data and material

No associated data.

References

Priyadarshani KN, Singh S, Singh K (2020) A novel self-aligned dopingless symmetric tunnel field effect transistor (DL-STFET): A process variations tolerant design. Silicon: 1–9

Priyadarshani KN, Singh S, Singh K (2021) Analog/RF performance estimation of a dopingless symmetric tunnel field effect transistor. J Electron Mater: 1–12

Hu C, Patel P, Bowonder A, Jeon K, Kim SH, Loh WY, Kang CY, Oh J, Majhi P, Javey A, Liu TJK (2010) Prospect of tunneling green transistor for 0.1 V CMOS. In: IEEE 2010 International electron devices meeting (IEDM), pp 16–1

Khatami Y, Banerjee K (2009) Steep subthreshold slope n-and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans Electron Devices 56(11):2752–2761

Zhang Q, Zhao W, Seabaugh A (2006) Low-subthreshold-swing tunnel transistors. IEEE Electron Device Lett 27(4):297–300

Choi WY, Park BG, Lee JD, Liu TJK (2007) Tunneling fieldeffect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28(8):743–745

Luisier M, Klimeck G (2009) Performance comparisons of tunneling field-effect transistors made of InSb, Carbon, and GaSbInAs broken gap heterostructures. In: IEEE International electron devices meeting (IEDM), pp 1–4

Avci UE, Rios R, Kuhn KJ, Young IA (2011) Comparison of power and performance for the TFET and MOSFET and considerations for P-TFET. In: 11th IEEE International conference on nanotechnology, pp 869–872

Esaki L (1974) Long journey into tunneling. Science 183(4130): 1149–1155

Tomioka K, Fukui T (2014) Current increment of tunnel field-effect transistor using InGaAs nanowire/Si heterojunction by scaling of channel length. Appl Phys Lett 104(2):0735 07–4

Beneventi GB, Gnani E, Gnudi A, Reggiani S, Baccarani G (2014) Dual-metal-gate InAs tunnel FET with enhanced turn-on steepness and high on-current. IEEE Trans Electron Devices 61(3):776–784

Krishnamohan T, Kim D, Raghunathan S, Saraswat K (2008) Double gate strained-Ge heterostructure tunneling FET (TFET) With record high drive currents and < 60mV/dec subthreshold slope, in IEDM Tech. Dig.: 1–3

Hou YT, Li MF, Low T, Kwong DL (2004) Metal gate work function engineering on gate leakage of MOSFETs. IEEE Trans Electron Devices 51(11):1783–1789

Kim SH, Agarwal S, Jacobson ZA, Matheu P, Hu C, Liu TJK (2010) Tunnel field effect transistor with raised germanium source. IEEE Electron Device Lett 31(10):1107–1109

Patel N, Ramesha A, Mahapatra S (2008) Drive current boosting of n-type tunnel FET with strained SiGe layer at source. Microelectron J 39(12):1671–1677

Saurabh S, Kumar MJ (2009) Impact of strain on drain current and threshold voltage of nanoscale double gate tunnel field effect transistor: Theoretical investigation and analysis. Jpn J Appl Phys 48 (6R):064503–1–064503-7

Kumar S, Goel E, Singh K, Singh B, Kumar M, Jit S (2016) A compact 2-D analytical model for electrical characteristics of double-gate tunnel field-effect transistors with a SiO2/High- k stacked gate-oxide structure. IEEE Trans Electron Devices 60(8):3291–3299

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling fieldeffect transistors. IEEE Trans Electron Devices 57(9):2317–2319

Leonelli D, Vandooren A, Rooyackers R, Verhulst AS, De Gendt S, Heyns MM, Groeseneken G (2010) Performance enhancement in multi gate tunneling field effect transistors by scaling the fin-width. Jpn J Appl Phys 49(4S):04DC10

Kumar P, Bhowmick B (2018) Suppression of ambipolar conduction and investigation of RF performance characteristics of gate-drain underlap SiGe Schottky barrier field effect transistor. Micro Nano Lett 13 (5):626–630

Krishnaraja A, Svensson J, Lind E, Wernersson LE (2019) Reducing ambipolar off-state leakage currents in III-V vertical nanowire tunnel FETs using gate-drain underlap. Appl Phys Lett 115(14):143505

Shaker A, El Sabbagh M, El Banna MM (2017) Influence of drain doping engineering on the ambipolar conduction and high-frequency performance of TFETs. IEEE Trans Electron Devices 64(9):3541–3547

Priyadarshani KN, Singh S, Naugarhiya A (2021) RF & linearity distortion sensitivity analysis of DMG-DG-Ge pocket TFET with hetero dielectric, Microelectronics Journal, 108, Art no 104973

Priyadarshani KN, Singh S, Naugarhiya A (2021) Dual metal double gate Ge-Pocket TFET (DMG-DG-Ge-Pocket TFET) with hetero dielectric: DC & analog performance projections. Silicon: 1–12

Bardon MG, Neves HP, Puers R, Van Hoof C (2010) Pseudo two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans Electron Devices 57(4):827–834

Pan A, Chui CO (2012) A quasi-analytical model for double-gate tunneling field-effect transistors. IEEE Electron Device Letter 33(10):1468–1470

Verhulst AS, Sore B, Leonelli D, Vandenberghe GW, Groeseneken G (2010) Modeling the single-gate, double-gate, and gate-allaround tunnel field-effect transistor. Japanese J Appl Phys 107 (2):024518–1–024518-8

Vishnoi R, Kumar MJ (2014) Compact analytical model of dual material gate tunneling field-effect transistor using interband tunneling and channel transport. IEEE Trans Electron Devices 61(6):1936–1942

Vishnoi R, Kumar MJ (2015) An accurate compact analytical model for the drain current of a TFET from subthreshold to strong inversion. IEEE Trans Electron Devices 62(2):478– 484

Pan A, Chen S, Chui CO (2013) Electrostatic modeling and insights regarding multigate lateral tunneling transistors. IEEE Trans Electron Devices 60(9):2712–2720

Kumar S, Raj B (2015) Compact channel potential analytical modeling of DG-TFET based on Evanescent-mode approach. J Comput Electron 14(3):820–827

Sarkhel S, Bagga N, Sarkar SK (2016) Compact 2D modeling and drain current performance analysis of a work function engineered double gate tunnel field effect transistor. J Comput Electron 15(1):104–114

Kumar S, Singh K, Baral K, Singh PK, Jit S (2021) 2-D analytical model for electrical characteristics of dual metal heterogeneous gate dielectric double-gate TFETs with localized interface charges. Silicon 13(8):2519–2527

Gupta SK, Kumar S (2019) Analytical modeling of a triple material double gate TFET with hetero-dielectric gate stack. Silicon 11(3):1355–1369

Vimala P, Samuel TA, Nirmal D, Panda AK (2019) Performance enhancement of triple material double gate TFET with heterojunction and heterodielectric. Solid State Electron Lett 1(2):64–72

ATLAS AUM (2015) Silvaco International, Santa Clara, CA

Kumar S, Goel E, Singh K, Singh B, Singh PK, Baral K, Jit S (2017) 2-D analytical modeling of the electrical characteristics of dual-material double-gate TFETs with a SiO2/HfO2 stacked gate-oxide structure. IEEE Trans Electron Devices 64(3):960–968

Bardon MG, Neves HP, Pures R, Hoof CV (2010) Pseudo two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans Electron Devices 57(4):827–834

Acknowledgements

Authors are thankful to National Institute of Technology, Patna for granting the computational resources.

Funding

No funding is availed.

Author information

Authors and Affiliations

Contributions

Kumari Nibha Priyadarshani has developed the model and the computational framework. Sangeeta Singh has devised the idea, helped while preparing the final draft and supervised.

Corresponding author

Ethics declarations

Ethics approval and consent to participate

We comply to the ethical standards. We provide our consent to take part.

Consent for Publication

All the authors are giving consent to publish.

Conflict of Interests

No conflict of interest to disclose.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Priyadarshani, K.N., Singh, S. Double Metal Double Gate Hetero-oxide Tunnel FET: An Analytical Model. Silicon 14, 7017–7024 (2022). https://doi.org/10.1007/s12633-021-01476-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01476-8