Abstract

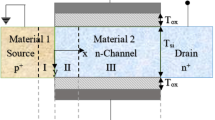

In this work a piecewise Surface Potential based analytical model for a Hetero-Dielectric p-n-i-n Double Gate Tunnel FET has been developed which captures the device performance in all regions of operation i.e. Accumulation, Depletion and Inversion Region. Moreover, a comparative study among single High-k dielectric, single Low-k dielectric and Hetero-Dielectric TFET has been done. Here Vgs and Vds dependent explicit equations for surface potential have been derived which are subsequently been made to be channel length dependent. Furthermore, the electrostatic behavior of the device is studied in terms of Lateral Electric Field and Energy Band Diagram. The efficacy of the model has been validated through simulated results obtained using ATLAS device simulation software.

Access provided by Autonomous University of Puebla. Download to read the full chapter text

Chapter PDF

Similar content being viewed by others

References

W. Y. Choi, B.-G. Park, J. D. Lee, and T.- J. K. Liu, IEEE Electron Device Letters, 28, 743 (2007).

B. Syamal, C. Bose and C. K. Sarkar, IEEE International Conference of Electron Devices and Solid-State Circuits, 1 (2010).

N. Cui, R. Liang, and J. Xu, Appl. Phys. Letters, 98, 142105 (2011).

C. Shen, S.-L. Ong, C.-H. Heng, G. Samudra and Y.-C. Yeo, IEEE Electron Device Letters, 29, 1252 (2008).

ATLAS Device simulation Software, Silvaco Int., Santa. Clara, CA, Version 5.14.0.R, 2010.

M. G. Bardon, H. P. Neves, IEEE Transactions on electron Devices, 57, 827 (2010).

A. Ortiz-Conde, F. J.G. Sanchez and S. Malobabic, IEEE Transactions on electron Devices, 52, 1669 (2005).

J. He, L. Zhang, R. Zheng and M. Chan, Molecular Simulation, 35, 448 (2009).

Acknowledgments

Authors would like to thank Ministry of Science and Technology, Department of Science and Technology, Government of India and University of Delhi. One of the authors Upasana, would like to thank University Grants Commission, Govt. of India for providing necessary financial assistance during the course of this research work.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2014 Springer International Publishing Switzerland

About this paper

Cite this paper

Upasana, Narang, R., Saxena, M., Gupta, M. (2014). Surface Potential Based Analytical Model for Hetero-Dielectric p-n-i-n Double-Gate Tunnel-FET. In: Jain, V., Verma, A. (eds) Physics of Semiconductor Devices. Environmental Science and Engineering(). Springer, Cham. https://doi.org/10.1007/978-3-319-03002-9_75

Download citation

DOI: https://doi.org/10.1007/978-3-319-03002-9_75

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-03001-2

Online ISBN: 978-3-319-03002-9

eBook Packages: Earth and Environmental ScienceEarth and Environmental Science (R0)