Abstract

This article proposes a generic approach for modelling threshold voltage of oxide thin film transistors (TFTs). Threshold voltage has always been ambiguous in TFTs due to the disordered nature of semiconducting thin films, and in operation in accumulation mode. This differs from the situation with metal oxide field-effect transistors (MOSFETs), wherein strong inversion can be specifically defined. The proposed model considers double exponential distribution of deep state and tail state densities in the bandgap with the multiple-trapping-and-release (MTR) transport model. In this surface potential-based approach, pinned surface potential is defined as the surface potential at which free carrier densities exceed deep state carrier density in the deep state-dominated region. The threshold voltage is defined using pinned surface potential and carrier densities obtained at that surface potential. The model is validated using data from fabricated oxide based TFTs with silicon dioxide (SiO2) and other dielectrics. This article develops and reports a systematic approach for fitting an oxide based TFT analytical model with experimental devices, thus ensuring the flexibility needed for compatibility with various devices.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

Applications of thin film transistors (TFTs) in transparent and flexible electronics, including displays, pixel circuits and various types of sensors, have gained a significant boost in recent years. Among various TFTs, oxide TFTs exhibit particularly interesting characteristics such as high mobility, flexibility, wide bandgap and optical transparency.1 Accordingly, oxide TFTs have emerged as a superior alternative to existing a-Si and poly-Si TFTs for large area electronic applications. TFTs include three basic elements: (1) a semi-conducting channel layer; (2) a gate dielectric layer; and (3) three electrodes (gate, source and drain). In an attempt to improve device performance, various architectures have been proposed. Bottom gate gallium indium zinc oxide (GIZO) TFTs have good threshold voltage control.2 Other configurations such as double gate TFTs find use in high performance pixel circuits. In TFTs, top gate structure provides protection to the channel, whereas coplanar structures offer enhanced performance due to less parasitic capacitance.3 Another architecture called the source gated TFT has shown improved device characteristics and parameters.4

Compact models play an important role in circuit design. Importance of compact models has been highlighted in Ref. 5 with descriptions of TFT models and charge transport properties. In the design and implementation of circuits, it is important to have a detailed understanding of the device behaviour for various conditions and parametric variations. Hence, it is essential to develop a non-iterative, simple and accurate mathematical model to represent the device parameters. Such a model not only describes the physics of the device, but is suitable for use in circuit simulators. Threshold voltage is a critical parameter for any field-effect device, as it determines characteristics such as switching, ratio of on and off currents (Ion/Ioff) and subthreshold slope. Unlike metal oxide semiconductor field-effect transistors (MOSFETs), TFTs do not operate by the mechanism of charge inversion at the surface to form a channel, therefore, it becomes difficult to model the threshold voltage. MOSFETs have a single crystalline silicon channel which is devoid of any traps. Also, MOSFETs operate in inversion mode for conduction, hence it is simpler to demarcate a clear threshold point at strong inversion. On other hand, oxide TFTs mainly operate in accumulation mode and have amorphous or polycrystalline channels. Ideally, for gate-to-source voltage beyond flat band voltage, TFTs should show the initiation of accumulation, and the active oxide layer should conduct, but the disordered channel gives rise to trap states, leading to mobility degradation, trapping and a decrease in free carrier density. It is quite challenging to consider the effect of disordered channels on carrier density, and have clear demarcation of the threshold point where there are enough free carriers accumulated in the channel for conduction.

Threshold voltage mainly depends on the material of the conducting film,6,7 the quality of the interface and the gate dielectric. Variations in threshold voltage in TFTs having the same channel material but different gate dielectrics like Hafnium Oxide (HfO2) and Aluminium Oxide (Al2O3) has been reported in Ref. 8. The accuracy of threshold voltage models may vary with device configurations and architecture, channel oxide, gate dielectric, process of fabrication, and transport model, as these parameters determine the trap state carriers and free carriers in the device. Many attempts have been made recently to address this issue. Efforts have been made to model the traps and consider their impact while modelling the threshold voltage. Scaled oxide can lower the threshold voltage, which can be modelled using a single grain boundary in a grain boundary transport model.9 In Ref. 10, line charge approximation of traps was considered due to single line grains (1-Dimension) and threshold voltage was modelled using potential due to this line charge. Single exponential distribution of trap densities with constant deep state density was considered in Ref. 11, and threshold voltage was defined at the interface of the dominant deep state and tail state regions. In Ref. 12 trap states were considered to have a Gaussian distribution. The authors in Ref. 13 defined threshold voltage at degenerate conduction with the help of free charge density and an empirical constant. In Ref. 14, four surface potentials were extracted using different approximations to find their relation with threshold voltage. However, there is a need for a model which takes into account the significant parameters which determine the threshold voltage in TFTs. To address the non-uniformity in existing models for TFTs, this study focuses on reporting a compact and closed form expression of threshold voltage, which can universally take into account the traps and carrier densities without posing a threat to computation time. This work proposes a threshold voltage model based on surface potential and multiple-trapping-and-release (MTR) transport. Using conditions involving a pinned surface potential, which is defined with the help of the free carrier density and deep state carrier density, the threshold voltage is derived, and validated with reported works. This paper is organized as follows: "Significance of Trap States" section discusses the significance of trap state densities and the MTR model. "Methodology to Extract the Threshold Voltage" section describes the methodology for extracting the threshold voltage. In "Validation" section, the model is validated based on experimental papers. "Conclusion" section concludes the paper. Table I defines the list of symbols used in the paper.

Significance of Trap States

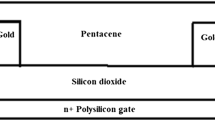

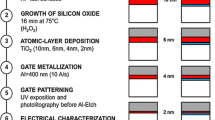

Oxide TFT uses an oxide semiconductor as the conduction layer between source and drain. Considering a bottom gate structure, the gate is placed on a substrate. The oxide channel layer and the gate are separated by a gate dielectric to generate the field-effect, as shown in Fig. 1.

During the growth of metal oxide film in an oxygen deficient environment, it is easier for the metal ions to occupy interstitial vacancies in the metal oxide lattice. The free electrons contributed by metal atoms roam freely in the crystal, giving rise to n-type conductivity. Also, there are O2+ vacancies giving rise to more electrons. The deposited channel oxide semiconductor is mostly either amorphous or polycrystalline in nature. In a polycrystalline material, presence of grain boundaries gives rise to a lot of defects, which, in turn, gives rise to trap states within the bandgap. Different charge transport models are prevalent to describe conduction in TFTs. Modelling of trap states, which determine the charge transport in polysilicon films, are depicted by the grain boundary model. Additionally, the hopping transport model accounts for charge transport in amorphous films. Materials like metal oxides form polycrystalline films. These semiconductors display regular arrangement, and delocalized orbitals partially overlap, thereby facilitating more efficient charge transfer and carrier mobility that is much larger than that of amorphous films. The charge transport properties of these materials cannot be explained by the grain-boundary trapping theory and hopping transport.5 As metal oxides like indium gallium zinc oxide (IGZO) become intrinsically n-type, therefore, there are already free electrons in the bulk. When we apply gate voltage \( V_{g}\), they are attracted towards the gate, and the Fermi level rises nearly to \( E_{C}\). As a result, more trap states in the bandgap become available for valence band electrons. As these electrons move easily from \(E_{V}\) to these trap states, they can further easily excite to conduction band from these trap states. The reduction in difference between \(E_{f}\) and \(E_{C}\) aids this phenomenon. These carriers get re-trapped in the trap states from \(E_{C}\) and are thermally excited back to \(E_{C}\) as shown in Fig. 2. At threshold voltage, abundant free carriers are accumulated (at the same time getting trapped and released) and we get trap limited conduction (TLC).11 Hence, the MTR model is suitable for modelling \(V_{{{\text{th}}}}\) for oxide TFTs having trap states. If \( V_{g}\) is reduced, the Fermi level moves down. Therefore, the carriers which are trapped find it difficult to rise up to \( E_{C}\); instead, they (the carriers initially trapped due to higher Fermi level) fall to back to \(E_{v}\) as Fermi level goes down. Considering the MTR, we assume that charge transport takes place in the delocalized states, which resembles conduction and valence bands for electrons and holes, respectively. The mobility edge separates localized and delocalized states (Fig. 2). There are two types of trap state densities in the region of localized states, namely deep states and tail states. These trap states account for both inter-grain and intra-grain defects in the film. Deep states are dominant near the centre of the bandgap, while tail states become dominant as we move towards the conduction or valence band (Fig. 3). The deep states are mainly due to oxygen vacancies and the tail states arise from metal. Conduction occurs due to free charge carriers in delocalized states above the mobility edge. We have considered a double exponential distribution model for distribution of density of states (DOS).15 These trap states play a critical role in predicting the device parameters and behaviour.

Methodology to Extract the Threshold Voltage

This section discusses the steps in arriving at the equation of threshold voltage through different subsections.

DOS and Charge Density

The double exponential distribution of deep and tail states is given by:

The exponential functions at low and high energy values represent the dominant distribution of deep and tail states in the energy gap, respectively. At flat band, the Fermi level is at \(E_{f0}\). As the gate voltage increases, the Fermi level begins to rise and bands start bending near the oxide-semiconductor interface. Consider the band bending due to surface potential within the channel thickness, \(t_{s}\).16 As the band bending starts, free charges begin to accumulate at a slow rate initially as per the MTR model. As the Fermi level rises, these trapped states become occupied by the carriers up until the Fermi level, at which point it becomes more feasible to excite them thermally. Initially, the Fermi level resides in the deep state dominated region near the middle of the band gap. The distribution of deep state carrier density is given by \(n_{d} = \mathop \smallint \limits_{Ef0}^{Ef} N_{{{\text{deep}}}} \left( E \right)f\left( E \right){\text{d}}E\) , where \(f\left( E \right) = \frac{1}{{1 + \exp \left( {\frac{{E - E_{f} }}{kT}} \right)}}\) is the probability function, and \(N_{{{\text{deep}}}} \left( E \right) = N_{d} {\text{exp}}\left( {\frac{{E - E_{C} }}{{kT_{d} }}} \right)\). When we substitute \(E = E_{f},\) we get

This can be approximated as \(n_{d} = N_{d} kT_{d} \ln \left( 2 \right)\exp - \left( {\frac{{E_{c} - E_{f} }}{{kT_{d} }}} \right)\). Trapped state charge density in deep states is given by:

If the Fermi level rises further, there is an increase in tail state trap densities and they start becoming dominant. Tail state carrier density is defined as \(n_{t} = \mathop \smallint \limits_{Ef0}^{Ef} N_{{{\text{tail}}}} \left( E \right)f\left( E \right){\text{d}}E\), where \(N_{{{\text{tail}}}} \left( E \right) = N_{t} \exp \left( {\frac{{E - E_{c} }}{{kT_{t} }}} \right)\). When we substitute \(E = E_{f},\) we get

where \(E_{f} = E_{f0} + q\Psi_{s}\) is the energy level corresponding to the gate voltage. Trapped state charge density in tail states is given by:

and similarly, free charge density can be defined as:

where

Threshold Voltage

Since TFTs work in the accumulation mode of conduction, it becomes inconvenient to define their threshold voltage equation in terms of the inversion-based model in MOSFETs. Although the concept of \(V_{fb}\) fits well for both accumulation and inversion mode devices, the major difference lies in defining the surface potential and charge density terms in the \(V_{{{\text{th}}}}\) equation. In MOSFET, surface potential condition at the threshold point is defined as \(\Psi_{s} = 2\emptyset_{f}\), where \(\emptyset_{f}\) is the bulk Fermi potential, which suggests that the inverted charge density at this surface potential equals the bulk charge density and is sufficient to shield the bulk charge density; so it is large enough for conduction. Further increase in gate voltage (\(V_{g}\)) increases inverted charge density without a further rise in surface potential.

In TFTs, threshold voltage can be defined as the gate voltage at which sufficient free carriers are available to conduct drain current. As the gate voltage is increased, the capacitance of the field-effect transistor varies based on charge variation in the bulk and in the channel (Fig. 4a for TFT; similar MOSFET analogy in Fig. 4b). For MOSFET, this depends on bulk charges, while for oxide TFTs it is determined by deep state, tail state and free carrier densities. The gate voltage at which free carrier density exceeds deep-state carrier density is defined as the threshold voltage. This transition point highly depends on properties of the film (largely on trap states), which in-turn depends on fabrication conditions and process. At gate voltages beyond the threshold voltage, there is a large rise in accumulation of free carriers as the gap between \(E_{f}\) and \(E_{c}\) reduces and trapped carriers are easily excited to \(E_{c}\) , further shielding the trap states. The surface potential at which threshold voltage is attained is defined as the pinned surface potential,\({{ \Psi }}_{sp},\) as shown in Fig. 5. Since at this surface potential, the Fermi level is in the deep state-dominated region, tail state carrier density is less significant, although their effects are considered in the model. Process variation has significant impact on trap densities and, in turn, on pinned surface potential. So, there is no fixed condition for pinned surface potential in TFT as there is in MOSFET. While modelling \(V_{th}\), these variations in pinned surface potential due to fabrication conditions and processes have been accounted for by considering a parameter for modelling the traps (\(N_{d} , T_{d} , N_{t} , T_{t}\)). This serves as a fitting parameter to bring the modelled properties in line with the fabricated device as shown in "Validation" section. The threshold voltage in Eq. 9 has been defined using surface potential as defined in Eq. 8 from Ref. 17, and corresponding carrier densities.

Carrier density versus surface potential for the fabricated TFT (data from Ref. 17).

Figure 5 shows variation in carrier densities with surface potential, plotted for device parameters given in Ref. 17 (Sr no. 2 in Table II). It can be seen that at pinned surface potential (\({\Psi }_{sp} =\) 0.05V), the plot for free carrier density crosses the plot for deep state carrier density, which gives the threshold voltage point.

where \(Q_{s} = qn_{tot} t_{s}\) and \(n_{{{\text{tot}}}}\) is obtained as

Using this pinned surface potential, we can find the relation between deep state charge density and tail state charge density at the threshold voltage. From Eqs. 3 and 5 we can get the values of deep and tail state charge density. Also, charge density of accumulated free carriers can be obtained at threshold using Eq. 6.

Validation

The proposed threshold voltage model has been verified and validated using data from experimental papers as shown in Table II. In some cases1,22,23,24,25 where information about trap densities (\(N_{d} , T_{d} , N_{t} , T_{t}\)) has not been given in the paper, typical values have been assumed as used in the experimental papers. In experimental papers17,18,19,20,21 these parameters were extracted from software and used as fitting parameters to validate the simulated model with a fabricated device. Mismatch between reported \(V_{th}\) and modelled \(V_{th}\) in this work is mainly due to small variations in \(n_{tot}\) calculated from the model, which are small with respect to the order of carrier density.

This mismatch in \(n_{tot}\) is accounted for by allowed variations in \(N_{d} , T_{d} , N_{t}\) and \(T_{t}\). Since these are physical entities and can be used as fitting parameters, we can tune them to vary \(n_{tot}\) , and consequently the modelled \(V_{th}\). Graphs in Figs. 6 and 7 show variation of \(V_{th}\) and absolute deviation of \(V_{th}\) from reported values with \(n_{tot}\). It can be seen that at the minima of absolute deviation, we get the \(n_{tot}\) (which is a function of \(N_{d} , T_{d} , N_{t} , T_{t} \) and \(\Psi_{sp}\)) required to get reported \(V_{th}\) value of the fabricated device. Modelled \(V_{th}\) lies within a permissible range of \(n_{tot}\) variation i.e., ± 4 × 1016 cm− 3 for devices with SiO2 dielectric and ± 4 × 1017 cm− 3 for devices with other dielectrics as per the tuning of \(N_{d} , T_{d} , N_{t}\) and \(T_{t}\). Interestingly, the proposed model is able to universally validate the results from fabricated devices through the typical range of \(n_{tot}\) used.

Threshold voltage and absolute deviation versus total carrier density for devices with SiO2 dielectric: (a) TFT1, TFT2, TFT3; (b) TFT4, TFT5, TFT6; (c) TFT7, TFT8, TFT9, TFT10, where TFTn represents TFT corresponding to serial number ‘n’ in Table II.

Threshold voltage and absolute deviation versus total carrier density for devices with (a) La2O3/ La2OA/ La2OB dielectrics and (b) HfO2/ ZrO2/ AlOx dielectrics, where TFTn represents TFT corresponding to serial number ‘n’ in Table II.

Conclusion

In this paper, we have developed a simple yet robust mathematical model for computing the threshold voltage of oxide TFT. We have demonstrated the impact of charge density in determining the threshold voltage. With the help of surface potential, values of free and trapped carrier densities at threshold voltage can be deduced. As free carrier density exceeds deep state carrier density, corresponding pinned surface potential defines the threshold voltage point. The model defines the threshold voltage in oxide TFTs with reference to the MTR transport model. The dependence of threshold voltage on the fundamental parameters and material properties makes the model compact. The proposed threshold voltage model holds valid for all oxide TFTs with SiO2 as well as other dielectrics. Hence, this generic model can be tuned with trap density parameters as per requirements, which is verified with several fabricated devices.

References

J. Lee, S. Chang, S. Koo, and S. Lee, IEEE Electron Device Lett. 31, 225 (2010).

J. Kwon, K. Son, J. Jung, T. Kim, M. Ryu, K. Park, B. Yoo, J. Kim, Y. Lee, K. Park, S. Lee, and J. Kim, IEEE Electron Device Lett. 29, 1309 (2008).

L. Zhang L, W. Xiao, W. Wu, B. Liu (2019) Appl. Sci. (Switzerland) 9:1

A. Ma, M. Benlamri, A. Afshar, G. Shoute, K. Cadein and D. Barlage, CS Mantech 385 (2014).

N. Lu, W. Jiang, Q. Wu, D. Geng, L. Li, and M. Liu, Micromachines 9, 1 (2018).

C. Chang, and Y. Wu, J. Electron. Mater. 37, 1653 (2008).

C. Tsay, M. Wang, and S. Chiang, J. Electron. Mater. 38, 1962 (2009).

P. Carcia, R. McLean, and M. Reilly, Appl. Phys. Lett. 88, 30 (2006).

N. Gupta, Phys. Scr. 76, 628 (2007).

K. Kandpal, N. Gupta, J. Singh, and C. Shekhar, J. Electron. Mater. 49, 3156 (2020).

S. Lee, and A. Nathan, Sci. Rep. 6, 1 (2016).

F. Hossain, J. Nishii, S. Takagi, A. Ohtomo, T. Fukumura, H. Fujioka, H. Ohno, H. Koinuma, and M. Kawasaki, J. Appl. Phys. 94, 7768 (2003).

L. Qiang, and R. Yao, IEEE Trans. Electron Devices 61, 2394 (2014).

C. Chen, W. Chen, L. Zhou, W. Wu, M. Xu, L. Wang, and J. Peng, AIP Adv. 6, 035025 (2016).

F. Torricelli, J. Meijboom, E. Smits, A. Tripathi, M. Ferroni, S. Federici, G. Gelinck, L. Colalongo, Z. Kovacs-Vajna, D. De Leeuw, and E. Cantatore, IEEE Trans. Electron Devices 58, 2610 (2011).

S. Lee, S. Jeon, and A. Nathan, IEEE/OSA J. Disp. Technol. 9, 883 (2013).

P. Migliorato, M. Chowdhury, J. Um, M. Seok, M. Martivenga, and J. Jang, IEEE/OSA J. Disp. Technol. 11, 497 (2015).

H. Choi, J. Lee, H. Bae, S. Choi, D.H. Kim, and D.M. Kim, IEEE Trans. Electron Devices 62, 2689 (2015).

H. Hsieh, T. Kamiya, K. Nomura, H. Hosono, and C. Wu, Appl. Phys. Lett. 92, 10 (2008).

Y. Jeon, S. Kim, S. Lee, D.M. Kim, D.H. Kim, J. Park, C. Kim, I. Song, Y. Park, U. Chung, J. Lee, B. Ahn, S. Park, J. Park, and J. Kim, IEEE Trans. Electron Devices 57, 2988 (2010).

W. Chen, G. Qin, L. Zhou, W. Wu, J. Zou, M. Xu, L. Wang, and J. Peng, AIP Adv. 8, 065319 (2018).

L. Qian, P. Lai, and W. Tang, Appl. Phys. Lett. 104, 1 (2014).

P. Gogoi, R. Saikia, D. Saikia, R. Dutta, and S. Changmai, Physica Status Solidi (A) ApplMater. Sci. 212, 826 (2015).

L. Ji, C. Wu, T. Fang, Y. Hsiao, T. Meen, W. Water, Z. Chiu, and K. Lam, IEEE Sens. J. 13, 4940 (2013).

M. Furuta, T. Kawaharamura, D. Wang, T. Toda, and T. Hirao, IEEE Electron Device Lett. 33, 851 (2012).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Desai, M.S., Kandpal, K. & Goswami, R. A Multiple-Trapping-and-Release Transport Based Threshold Voltage Model for Oxide Thin Film Transistors. J. Electron. Mater. 50, 4050–4057 (2021). https://doi.org/10.1007/s11664-021-08907-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-021-08907-7