Abstract

In this paper, a new memristor-less fractional-order meminductor emulator has been presented based on two operational transconductance amplifiers (OTAs), and a current differencing buffered amplifier (CDBA). The integer and fractional capacitors have been utilized in the proposed design of floating and grounded types. It also offers the freedom of conversion between incremental and decremental in both the types i.e., grounded, and floating. The pinched hysteresis loops have been obtained up to 3 MHz for both incremental and decremental setups of the proposed fractional-order meminductor emulator. The simulation results were achieved using the LTSpice tool with 180 nm CMOS technology specifications. The suggested meminductor emulator's performance has also been compared to that of existing emulators reported in the literature. To test the effectiveness of the suggested fractional-order meminductor emulator, an adaptive learning circuit has been simulated.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

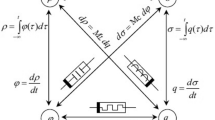

The theory of arbitrary order, real or complex, integrations, and derivatives is known as fractional calculus, and it generalizes the traditional notations for differentiation and integration. It's an extremely handy mathematical tool that was obscured and used very less, but, by the 1980s it was realized that fractional calculus translates the reality of nature better since it has more flexibility in differential order. This feature offers us a language through which we can communicate with nature. Recent years have seen the use of fractional calculus in a variety of disciplines, including engineering, material theory, biology, diffusion theory, economics, electromagnetic, control theory, robotics, signal, and image processing [1]. Fractional-order capacitors, also referred to as constant phase elements (CPEs), are becoming increasingly important in a wide range of applications where Cα stands for pseudo-capacitance and for order, also known as the dispersion coefficient. It offers an impedance of 1/Cαsα and a constant phase angle of -απ/2. The effective manufacturing of this device has recently been investigated by utilizing several materials. A few examples of the many methods used to create CPEs include the usage of graphene most recently in [7], fractal patterns on silicon [2], electrolytic process [3], submerging a polymer-coated capacitive type probe inside a polarizable solution [4,5,6], and electrolytic technique. All of these options, however, are commercially unavailable and lack the benefit of dynamic customization. Passive RC trees are now being used to simulate CPEs, for which the components may be produced using a variety of approaches, including continuing fraction expansion [8,9,10,11]. The Foster form is used to implement the circuit, which uses 5 resistors and 4 capacitors, and the fractional capacitor utilized in this study has been approximated by using continued fraction expansion (CFE) up to the fourth order [12]. The fractional element is halfway between a capacitor and a resistor, as we have a resistor at α = 0 and a capacitor at α = 1. The ideal CPE has a constant phase at all frequencies, but in practice, the phase is only constant over a small frequency range, which is referred to as the constant phase zone (CPZ). Because the phase oscillates somewhat even within the CPZ, actually realized CPEs are occasionally referred to as pseudo-CPEs. One of the key factors influencing interest in fractional calculus in applications is the nonlocality trait. Several intriguing physical phenomena have what are known as memory effects, which means that their current state depends not only on time and position but also on past states. For instance, in 1971, Professor Chua envisioned one such passive device. The circuit elements signify the relationship between pairs of the 4 electromagnetic entities of voltage, flux, charge, and current as shown in Fig. 1. The resistor relates voltage (v) with current (i) whereas the capacitor signifies the relationship between voltage (v) and charge (q). The inductor on the other hand relates the electromagnetic quantities of flux (ɸ) and current (i). However, the relationship between flux (ɸ) and charge (q) was not represented by any device. Therefore, in 1971, Professor Chua envisioned one such passive device. He postulated the existence of the memristor [13], a fourth essential circuit component that links flux and charge and whose resistance is determined by the total amount of charge that has travelled through it over a specific time period. He discussed the generalized concept of the memristor in 1976 [14]. But it was only after 2008, when, in HP-lab, Mr. Williams with his team realized the first memristor in physical form using TiO2, which drew the attention of many researchers towards this novel element [15]. It can be extremely difficult to describe and analyze systems with memory effects, such as the memristor, using conventional differential equations. Yet, nonlocality provides fractional derivatives with an inherent ability to include memory effects. Thus, fractional calculus may be a highly helpful technique for analysing this family of systems [16].

Relation between circuit elements [8]

Following the successful implementation of the memristor, quick development occurred, and the concept was expanded to include inductors and capacitors having memories inside them, which resulted in two other components namely the meminductor and memcapacitor [17].

However, due to the unavailability of commercially available memelements, scholars began to realize various emulators in order to combat this issue. By extensive literature review, it was realized that there are two ways in which meminductance has been realized. Firstly, various emulators were designed to convert memristors into meminductors and memcapacitors using mutator circuits [17, 18]. In [19,20,21,22] memristors have been converted to memcapacitor and meminductors using operational amplifiers, current conveyors, resistors, and capacitors. Meminductors have also been made using memristors, trans-impedance op amps, multipliers, and a few resistors and capacitors [23,24,25]. The SPICE model to convert memristor into meminductor has been given in [26]. The disadvantage of this strategy is that the characteristics of the developed meminductor emulator are heavily reliant on the memristor emulator's features. The alternative method is to make meminductor emulators without using memristors. The meminductors using this method do not use memristors but various active and passive building blocks are employed instead. VDTAs, CDBAs, and capacitors have been used to create high-frequency memristor-less meminductor emulators [27, 28]. Multipliers, current conveyors, op-amps, and OTAs along with resistors and capacitors have been used to realize memristor-less meminductors [21, 29,30,31,32,33]. These meminductor emulators use a lot of active and passive components, which makes the circuit very complex and error prone.

The above-discussed meminductor and memcapacitor emulators realize integer-order emulators and provide less flexibility in terms of regulating various parameters when used in a variety of applications. As depicted in Fig. 2, the pinched hysteresis loops develop between current (i) and flux (ϕ) for the meminductor and between voltage (v) as well as charge (q) for the memcapacitor. To create varied applications and to better handle the numerous circuit parameters, fine control over the pinched hysteresis curves is required.

The relation between mem elements [17]

The researchers faced this dilemma and therefore they turned to the field of fractional order devices in order to find a solution. A lot of research has been carried out over fractional-order memristors, which yielded some promising results in finely controlling the various parameters of the circuit [34,35,36,37,38,39,40,41] but since the concept of meminductors and memcapacitors is relatively new, therefore equal emphasis has not been given to fractional-order meminductor (FOMI) and memcapacitor (FOMC). Abdelouahab et al. in [42] presents the mathematical model of fractional-order mem elements. Few papers have been reported on the fractional-order meminductor and memcapacitor emulators. Four new fractional-order circuits have been proposed in [43] that contain fractional-order memristor, memcapacitor and meminductor. These fractional-order memristive, memcapacitive, and meminductive systems (FOMMMSs) exhibit a wide range of behaviours. In [44], the fractal-fractional-order domain of Caputo-Fabrizio is used to examine the dynamical properties of memcapacitor and meminductor. Fractional order memelements have been designed in [45] and their application in an analogue controller has been discussed. A general emulator circuit for fractional-order memelements has been realized in [46] using a multiplier, current conveyors, capacitors and resistors, and multiple pinched points have been obtained. Four universal fractional-order memelements emulators have been proposed in [47] using CCII, DVCC and analogue multiplier, DOTA + , BOCC. These emulators have been used to create a chaotic oscillator that demonstrates their capabilities. In [48], a fractional-order current-controlled meminductor model with a nonlinear window function is investigated, and the amplitude-frequency response properties of the meminductor under various excitation signals are analysed in depth. In [49], various arrangements of memristor, fractional-order capacitor, and resistor were employed to achieve fractional-order meminductor and memcapacitor. It has been demonstrated how the pinched point and the hysteresis loop area fluctuate with changes in α and frequency. The effect of change in α has been observed in [50] on floating fractional-order memelements realized using memristor and current conveyors. Different implementations of the emulator have been proposed using different active blocks and impedances. A current/voltage controlled universal emulator realized using two switches, a CCII block, a multiplier and a fractional order capacitor has been featured in [51]. In order to realize a fractional-order meminductor emulator circuit, a fractional-order capacitor that was constructed using the CFE method and Foster-I method is used. With the aid of two OTAs and a CDBA, the meminductor emulator has been realized. It is shown that the fractional-order meminductor emulator performs better than an integral-order meminductor emulator in terms of frequency responsiveness. In comparison to existing FOMI realisations described in the literature, the suggested fractional-order meminductor emulator has a lot simpler architecture and a much better frequency response.

The introduction is the first of this paper's seven sections. In Sect. 2, the characteristics of OTA and CDBA are described. In Sect. 3, the proposed grounded and floating fractional-order meminductor emulator's mathematical analysis is described. The simulation outcomes for grounded/floating configurations using the suggested fractional-order meminductor emulator are displayed in Sect. 4. In Sect. 5, the suggested fractional meminductor emulator is contrasted with current meminductor emulators. Section 6 discusses the use of the suggested meminductor emulators, and Sect. 7 provides the conclusions.

2 Characteristics of Voltage-Tunable OTA and CDBA

Figure 3 depicts the operational transconductance amplifier (OTA) symbol, which is voltage-tunable. It contains five terminals, including two input terminals (+ and −), two output terminals (+ and −), and a fifth terminal (VB) for regulating the OTA's transconductance gain (gm). Due to their extremely high input impedance, the two input terminals drain essentially no current as indicated by Eq. (1). When applied to the two high impedance input terminals of the OTA, " + " and "-," a differential voltage (Vin+—Vin-) results. This voltage is then converted to current (Ix+ and Ix-) at the output terminals "X", where the transconductance gain "gm" of the OTA depends on the bias voltage VB as given in Eq. 5. Figure 4 illustrates the CMOS implementation of an OTA [53].

where,

CMOS based Circuit diagram of OTA [53]

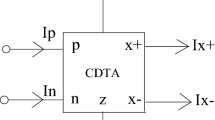

A current differencing buffered amplifier (CDBA), first described in [54], is represented by its symbol in Fig. 5. It is a 4-terminal analog building block having two output terminals (Z and W) and two input terminals (P and N). To apply the two currents IP and IN, two input terminals with low input impedance are used. It is possible to measure the difference between these currents at the ‘Z’ terminal. The ‘Z’ terminal is given an impedance to change IZ to VZ. To terminal W, an internal buffer replicates the voltage VZ. Equation 7 represents the terminal characteristics of a perfect CDBA. Figure 6 depicts CDBA's CMOS structure [55].

Circuit diagram of CDBA [55]

3 Design of the Proposed Fractional-Order Meminductor Emulator

In this section, the working principle of proposed fractional-order meminductor emulator along with realization of fractional-capacitor used in the design have been covered.

3.1 The Proposed circuit

Two OTAs and a CDBA are used in the proposed design of the incremental and decremental fractional-order meminductor emulator presented in Fig. 7. The " + " and "-" terminals of OTA1 accept the input voltage. The floating fractional-order meminductor emulator can be changed to a grounded fractional-order meminductor emulator by grounding the "-" terminal. The output of OTA1, “O1 + ”, is connected to the fractional capacitor C1. In the suggested design of the fractional meminductor emulator shown in Fig. 7a, the output terminals “O2-” and “O2+” of the second OTA (OTA2) are connected to the input terminals “ + ” and “-” of the first OTA (OTA1), respectively. The terminal “O2-” of OTA2 can be connected to terminal “P” or “N” of the CDBA in order to realize incremental or decremental meminductor emulators. By transferring the input current (IP = I02- + Iin or IN = IO2- + Iin) to the “Z” terminal, the capacitor C2 gets charged by CDBA. The transconductance (gm) of the OTAs is controlled to control the value of meminductance by transferring the voltage (VZ) to the CDBA's “W” terminal, which is connected to the OTA's VB terminal. A meminductor emulator is thus realized by adjusting the value of meminductance in accordance with the circuit's historical data (charge stored in C2).

The mathematical analysis of proposed fractional-order incremental meminductor emulator is presented below.:

where, \(\phi_{in}^{\alpha } = \frac{{V_{{\dot{i}n}} }}{{s^{\alpha } }} = \smallint V_{in} d^{\alpha } t\).

This is a fractional-order integral equation, which can be calculated by using the methods of [56] and [57]. Therefore, Eq. (7) can be written as:

As seen in Fig. 7, the terminal “O2-” is shorted to the CDBA's “P” terminal. The current Iz can therefore be expressed as,

The CDBA’s “Z” terminal will then have a voltage VZ,

Replacing the values of the current ‘V01-’ and ‘IO2’ from Eq. (8) and (9), respectively,

Taking \(\smallint \phi_{in}^{\alpha } dt = \frac{{\phi_{in}^{\alpha } }}{{s^{\alpha + 1} }} = \rho^{\alpha }\) and \(\smallint I_{in} dt = q\left( t \right)\)

The voltage VZ is transferred to CDBA's ‘W' terminal, which is coupled to the OTAs' ‘VB' terminal.

Since, \(G_{m1} = \frac{{K_{1} }}{\sqrt 2 }\left( {V_{B} - V_{ss} - 2V_{th} } \right)\), Therefore, replacing the value of ‘VB’ from Eq. 15 in Gm1

With the help of Eq. (8) and (9), we get,

Using the value of Gm1 from Eq. (14) in Eq. (15), we have,

The relation among flux \(\phi_{in}^{\alpha }\), current I(t) and meminductance (ML) is given by.

Equation 17 can be rearranged as,

Comparing Eq. (16) and (18), we get,

Connecting the terminal ‘O2-’ with the ‘N’ terminal of the CDBA in Fig. 6, we obtain,

Therefore, the values of meminductance for decremental and incremental meminductance is obtained as,

According to Eq. (22), meminductance for incremental meminductor emulators tends to increase whereas meminductance for decremental meminductor emulators decreases.

By connecting the ‘-' terminal of ‘OTA1' to the ground or any other node, respectively, it can be demonstrated that the proposed fractional meminductor emulator may be used in both grounded and floating configurations without affecting its functionality.

3.2 The Fractional Capacitor

Although it is well known that there is no such thing as an ideal fractional capacitor, there have been several attempts to approximate them in order to use them in fractional order systems. In 1964, Carlson used the regular Newton process to derive the rational approximation of s1/n and applied it using the RC ladder network [52]. Similar to this, Matsuda sought to approximate the irrational function to a rational one in [58] fitting the original function in a group of points that were logarithmically separated from one another. In order to obtain a function and an approximation of the fractional order capacitor, additional approximation approaches and identification procedures are also provided in [58].

One of the most well-known and often employed methods for approximating a fractional order impedance is called continuous fraction expansion (CFE). According to [59], it is:

in order to get a fractional capacitor's impedance function of the order of 0.5. We approximate till the fourth order in Eq. (23) by changing x and δ to (s-1) and -0.5, respectively, and to obtain the impedance function of the capacitor as

This gives us the impedance function for a fractional capacitor with 1F capacitance working best at an angular frequency (ω) of 1 rad/s.

By replacing ‘s’ by \(\frac{s}{{10^{6} }}\), and dividing Eq. (24) by the desired capacitance i.e., 10–6, we obtain the expression for a fractional capacitor (Eq. 25) with centre frequency as 106 and capacitance 1µF which has been used in the design of proposed fractional order meminductor.

Finding the roots and converting into partial fraction expansion form, we obtain:

Now, by solving this partial fraction and using the foster analysis, we know that we need 5 resistors and 4 capacitors with values as given in Fig. 7b.

4 Simulation Results

Using 180 nm CMOS technology characteristics, the suggested meminductor emulator was simulated using the LTSpice simulator. A 0.9 V supply is used to power the suggested circuit. The bias voltage (VB) of the CDBA is set to -0.1 V, and the bias currents are IB1 = IB2 = 20µA. Capacitor C2 is calibrated to 40pF. In Table 1 below, the aspect ratios utilised to create the OTAs and CDBA are listed.

4.1 Transient Analysis

An input sinusoidal signal with 100 mV amplitude and 100 kHz frequency was used to perform the transient analysis of the proposed decremental fractional-order meminductor emulator. Figure 8 depicts the transient waveforms for flux and current.

To produce the pinched hysteresis loop (PHL) for the proposed fractional-order meminductor emulator, a sinusoidal signal with amplitude 100 mV in a frequency range of 100 kHz to 3 MHz was used. The resultant PHL's area diminishes on increasing frequency, as illustrated in Fig. 9. Observing the values of flux (ɸ) on the x-axis of Fig. 9 can confirm this decrease in the hysteresis loop area. The hysteresis loop can last up to 3 MHz, but the pinched point shifts from the origin. As a result, for frequencies greater than 3 MHz, the loop deforms. The pinched hysteresis curves for integer-order decremental meminductor emulator have also been obtained in Fig. 10 but the pinched hysteresis loop deform much earlier as compared to fractional-order meminductor emulator.

In Fig. 11, the PHLs of the proposed incremental fractional meminductor emulator are exhibited for frequencies between 100 kHz and 3 MHz. The pinched hysteresis loops for integer-order incremental meminductor emulator have also been obtained in Fig. 12 but the pinched hysteresis loop also deform much earlier as compared to fractional-order meminductor emulator.

The temperature analysis was carried on a sinusoidal signal with 100 mV amplitude and frequency of 100 kHz, to assess the functioning of the proposed decremental/incremental fractional meminductor emulator. The temperature was adjusted between − 40 °C and + 40 °C. Figure 13 depicts the acquired results. The temperature study in Fig. 13 shows that the pinched hysteresis curves remain undistorted even when the temperature changes. As a result, the suggested decremental/incremental fractional meminductor emulator's temperature analysis is found to be satisfactory.

4.2 Pinched Hysteresis Loops at High Frequency

The pinched point (V = I = 0) is found to move further from the origin at higher frequencies. By appropriately scaling the value of the capacitor (C2) utilised in the construction of the fractional meminductor emulator, this shifting can be avoided. The pinched hysteresis loops are displayed in Fig. 14, at various frequencies, when the capacitor value is adjusted correctly to keep the pinched point near the origin.

4.3 Non-Volatility Test

Using a square pulse with a 100 mV amplitude, a pulse width of 2 µs, and a time period of 5 µs as the input signal, the non-volatility test for the suggested fractional-order meminductor emulator was carried out. The incremental order non volatility test is depicted in Fig. 15a, and it can be seen that when the pulse is high, the meminductance increases while in the non-pulse period the meminductor retains its value. Similarly, in Fig. 15b, the non-volatility test for decremental fractional-order meminductor is shown, and clearly there is negligible change in the meminductance during the non-pulse period while it decreases when the pulse is high.

5 Comparison of Proposed Fractional Order Meminductor Emulator with Other Meminductors in the Literature

The proposed fractional meminductor is contrasted with other meminductors in Table 2. The observations of Table 2 are given below,

-

1.

Many of the reported meminductor emulators employ memristors alongside various passive and active components [19,20,21,22,23,24,25, 27], while the proposed circuit is memristor-less.

-

2.

Many multipliers, current conveyors, operational amplifiers, as well as a significant amount of passive elements, are utilised by several meminductor;emulators; however, the proposed meminductor emulator is very simple in its design and makes use of minimal amount of components. [19, 22,23,24,25, 29,30,31,32,33, 46, 47, 49,50,51]

-

3.

For the fractional-order inverse meminductor in [46] and the FOMI in [47,48,49,50,51], the highest frequency for which PHLs are valid is only in the order of kHz, but the maximum frequency for the suggested fractional meminductor emulator is 3 MHz.

-

4.

The highest frequency for PHLs is limited to Hz and kHz for integral meminductor emulators reported in the literature [19, 20, 22,23,24,25, 29,30,31,32].

-

5.

The proposed fractional meminductor can be used both as a floating and grounded fractional meminductor emulator while many of the emulators in the literature are of either only grounded type. [19, 20, 23, 30, 31, 46, 47, 51]

6 Application of the Proposed Fractional Meminductor Emulator

To test the proposed fractional meminductor emulator's functionality, we designed an adaptive learning circuit [60,61,62] that simulates an amoeba's behavioural reaction. The amoeba mechanism is based on the current and previous states of the system, and it describes the associative learning process. The following statements reflect an amoeba's associative learning process:

-

1.

Remembering past events,

-

2.

Predicting the future based on the past, and

-

3.

To be able to recognise periodic event’s timing patterns.

This circuit, consisting of a capacitor, a resistor, and the fractional meminductor emulator (Fig. 16), represents the behaviour of the amoeba learning process.

The inductance of a meminductor fluctuates depending on the current that has flowed through it in the past, hence the meminductor adapts to the frequency of the temperature swings corresponding to the input voltage (Vin). It regulates the amoeba's movement, where the output voltage Vout, over the meminductor, indicates the amoeba's movement speed according to the temperature changes. The values of the components used in the adaptive learning circuit are R = 500Ω, C = 50nF and the fractional meminductor emulator.

From Fig. 17, we can clearly see that the output learns from the periodic behaviour of the input. After the low-temperature spike, it stays at low movement for some time in order to adapt quickly to the any other cold temperature spike. Only after sufficient time has passed, that it starts returning to the normal amount of activity, as can be seen after the first spike and between the 2nd and 3rd spike. This has shown that the designed adaptive learning circuit perfectly copies the behaviour of the amoeba learning.

7 Conclusion

A new design for an implementation of a grounded and floating incremental/decremental fractional meminductor emulator has been developed using two OTAs, a CDBA, a grounded capacitor, and a fractional capacitor. This emulator operates across a wide frequency range because the pinched hysteresis loops are not distorted up to 3-MHz frequency. The emulator's performance has also been confirmed to be satisfactory throughout a broad temperature range. There are several benefits to the proposed fractional meminductor emulator, including the absence of memristors, straightforward circuit design, and strong frequency response. By putting the suggested fractional meminductor emulator to use in an adaptive learning circuit, its performance was also verified.

Data Availability

Not applicable.

Code Availability

Not Applicable.

References

G. Tsirimokou, C. Psychalinos, A. Elwakil, “Design of CMOS Analog Integrated Fractional-Order Circuits: Applications in Medicine and Biology, Springer Briefs in Electrical and Computer Engineering (2017),” ISBN 978–3–319–55633–8.

Haba, T. C., Ablart, G., Camps, T., & Olivie, F. (2005). Influence of the electrical parameters on the input impedance of a fractal structure realized on silicon. Chaos, Solitons & Fractals, 24(2), 479–490.

Jesus, I. S., & Machado, J. A. (2009). Development of fractional order capacitors based on electrolytic process. Nonlinear Dynamics, 56(1), 45–55.

Biswas, K., Sen, S., & Dutta, P. (2006). Realization of a constant phase element and its performance study in a differentiator circuit. IEEE Transactions Circuits System II Express Briefs, 53(9), 802–806.

Mondal, D., & Biswas, K. (2011). Performance study of fractional order integrator using single component fractional order elements. IET Circuits, Devices and Systems, 5(4), 334–342.

Krishna, M. S., Das, S., Biswas, K., & Goswami, B. (2011). Fabrication of a fractional - order capacitor with desired specifications: A study on process identification and characterization. IEEE Transactions on Electron Devices, 58(11), 4067–4073.

Elshurafa, A. M., Almadhoun, M. N., Salama, K. N., & Alshareef, H. N. (2013). Microscale electrostatic fractional capacitors using reduced graphene oxide percolated polymer composites. Applied Physics Letters, 102(23), 232901–232904.

Krestinskaya, O., Irmanova, A., & James, A. P. (2020). Memristors: Properties, Models, Materials. In A. James (Ed.), Deep Learning Classifiers with Memristive Networks. Cham: Modeling and Optimization in Science and Technologies, Springer.

Steiglitz, K. (1964). An RC impedance approximation to s^ (-1/2). IEEE Trans. Circuits Syst., 11(1), 160–161.

Roy, S. C. D. (1967). On the realization of a constant-argument immittance or fractional operator. IEEE Transactions Circuits System, 14(3), 264–274.

Valsa, J., & Vlach, J. (2013). RC models of a constant phase element. International Journal of Circuit Theory and Applications, 41(1), 59–67.

Maundy, B., Elwakil, A., & Gift, S. (2010). On a multivibrator that employs a fractional capacitor. Analog Integrated Circuits and Signal Processing, 62, 99. https://doi.org/10.1007/s10470-009-9329-3

Chua, L. O. (1971). Memristor—The missing circuit element. IEEE Transaction on Circuit Theory, 18(5), 507–519.

Chua, L. O., & Kang, S. M. (1976). Memristive devices and systems. Proceedings of the IEEE, 64, 209–223.

Strukov, D. B., Snider, G. S., Stewart, D. R., & Williams, R. S. (2008). The missing memristor found. Nature, 453, 80–83.

Tarasov, V. E. (2018). No nonlocality, no fractional derivative. Communications in Nonlinear Science and Numerical Simulation, 62, 157–163.

Ventra, M. D., Pershin, Y. V., & Chua, L. O. (2009). Circuit elements with memory: Memristors, memcapacitors, and meminductor. Proceedings of the IEEE, 97, 1717–1724.

Ventra, M. D., Pershin, Y. V., & Chua, L. O. (2009). Putting memory into circuit elements: Memristors, memcapacitors, and meminductors. Proceedings of the IEEE, 97, 1371–1372.

Pershin, Y. V., & Ventra, M. D. (2009). Memristive circuits simulate memcapacitors and meminductors. Electronics Letters, 46, 517–518.

Biolek, D., & Biolkova, V. (2010). Mutator for transforming memristor into memcapacitor. Electronics Letters, 46, 1428–1429.

Pershin, Y. V., & Ventra, M. D. (2011). Emulation of floating memcapacitors and meminductors using current conveyors. Electronics Letters, 47, 243–244.

Yu, D. S., Liang, Y., Lu, H. H. C., & Hu, Y. H. (2014). Mutator for transferring a memristor emulator into meminductive and memcapacitive circuits. Chinese Physics B, 23, 070702.

M. P. Sah, R. K. Budhathoki, C. Yang and H. Kim, A mutator-based meminductor emulator circuit, 2014 IEEE International Symposium on Circuits and Systems (ISCAS) (IEEE, 2014), pp. 2249–2252.

D. S. Yu, H. Chen and H. H. C. Lu, A meminductive circuit based on floating memristive emulator, 2013 IEEE International Symposium on Circuits and SystemsInt. Symp. Circuits and Systems (ISCAS) (IEEE, 2013), pp. 1692–1695.

Yu, D., Liang, Y., Lu, H. H., & Chua, L. O. (2014). A universal mutator for transformations among memristor, memcapacitor, and meminductor. IEEE Transactions Circuits System II, Express Briefs, 61, 758–762.

Wang, H., Wang, X., Li, C., & Chen, L. (2013). SPICE mutator model for transforming memristor into meminductor. Abstract Applied Analysis, 2013, 281675.

Yadav, N., Rai, S. K., & Pandey, R. (2021). New grounded and floating memristor-less meminductor emulators using VDTA and CDBA. Journal of Circuits, Systems and Computers. https://doi.org/10.1142/S0218126621502832

Vista, J., & Ranjan, A. (2019). High frequency meminductor emulator employing VDTA and its application. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 39, 2020–2028.

Liang, Y., Chen, H., & Yu, D. S. (2014). A practical implementation of a floating memristor-less meminductor emulator. IEEE Transactions on Circuits and Systems II: Express Briefs, 61, 299–303.

Sah, M. P., Budhathoki, R. K., Yang, C., & Kim, H. (2014). Charge controlled meminductor emulator. Journal of Semiconductor Technology Science, 14, 750–754.

M. E. Fouda and A. G. Radwan, “Memristor-less current-and voltage-controlled meminductor emulators”, 2014 21st IEEE Int. Conf. Electronics, Circuits and Systems (ICECS) (IEEE, 2014), pp. 279–282.

Fouda, M. E., & Radwan, A. G. (2014). Simple floating voltage-controlled memductor emulator for analog applications. Radioengineering, 23, 944–948.

Sozen, H., & Cam, U. (2020). A novel floating/grounded meminductor emulator. Journal of Circuits, Systems and Computers, 29, 2050247.

Abro, K. A., & Atangana, A. (2020). Mathematical analysis of memristor through fractal-fractional differential operators: A numerical study. Mathematical Methods in the Applied Sciences. https://doi.org/10.1002/mma.6378

Yu, Y., Shi, M., Kang, H., et al. (2020). Hidden dynamics in a fractional-order memristive Hindmarsh-Rose model. Nonlinear Dynamics, 100, 891–906. https://doi.org/10.1007/s11071-020-05495-9

Wu, G. C., Luo, M., Huang, L. L., et al. (2020). Short memory fractional differential equations for new memristor and neural network design. Nonlinear Dynamics, 100, 3611–3623. https://doi.org/10.1007/s11071-020-05572-z

Qi, Y., Wu, C., Zhang, Q., Yan, K., & Wang, H. (2021, March). Complex dynamics behavior analysis of a new chaotic system based on fractional-order memristor. In Journal of Physics: Conference Series (Vol. 1861, No. 1, p. 012114). IOP Publishing.

Khalil, N. A., Hezayyin, H. G., Said, L. A., Madian, A. H., & Radwan, A. G. (2021). Active emulation circuits of fractional-order memristive elements and its applications. International Journal of Electronics and Communications. https://doi.org/10.1016/j.aeue.2021.153855

Wang, S. F., & Ye, A. (2020). Dynamical properties of fractional-order memristor. Symmetry, 12(3), 437. https://doi.org/10.3390/sym12030437

Fie, Y., Pu, BYu., & Yuan, X. (2021). "Ladder scaling fracmemristor: A second emerging circuit structure of fractional-order memristor. In IEEE Design & Test, 38(3), 104–111. https://doi.org/10.1109/MDAT.2020.3013826

N. A. Khalil, M. E. Fouda, L. A. Said, A. G. Radwan and A. M. Soliman, "Fractional-order Memristor Emulator with Multiple Pinched Points," 2020 32nd International Conference on Microelectronics (ICM), 2020, pp. 1–4, doi: https://doi.org/10.1109/ICM50269.2020.9331791.

Abdelouahab, M.-S., Lozi, R., & Chua, L. (2014). Memfractance: A mathematical paradigm for circuit elements with memory. Int J Bifurc Chaos, 24(9), 1430023.

Borah, M., & Roy, B. K. (2021). Hidden multistability in four fractional-order memristive, meminductive and memcapacitive chaotic systems with bursting and boosting phenomena. European Physical Journal Special Topics, 230, 1773–1783. https://doi.org/10.1140/epjs/s11734-021-00179-w

Abro, K. A., & Atangana, A. (2021). Numerical study and chaotic analysis of meminductor and memcapacitor through fractal-fractional differential operator. Arabian Journal for Science and Engineering, 46, 857–871. https://doi.org/10.1007/s13369-020-04780-4

Petráš and Y. Chen, "Fractional-order circuit elements with memory," Proceedings of the 13th International Carpathian Control Conference (ICCC), 2012, pp. 552–558, doi: https://doi.org/10.1109/CarpathianCC.2012.6228706.

Khalil, N., Fouda, M. E., Said, L., Radwan, A., & Soliman, A. M. (2020). A General Emulator for Fractional-Order Memristive Elements with Multiple Pinched Points and Application. AEU - International Journal of Electronics and Communications., 124, 153338. https://doi.org/10.1016/j.aeue.2020.153338

Khalil, N., Said, L., Radwan, A., & Soliman, A. M. (2020). Emulation circuits of fractional-order memelements with multiple pinched points and their applications. Chaos Solitons & Fractals., 138, 109882. https://doi.org/10.1016/j.chaos.2020.109882

Meng, L., Zhaohui, G., & Shiying, Z. (2019). Analysis of amplitude-frequency characteristics of fractional-order current-controlled meminductor. Journal of System Simulation, 31(6), 1179.

Khalil, N., Said, L., Radwan, A., & Soliman, A. M. (2019). General fractional order mem-elements mutators. Microelectronics Journal. https://doi.org/10.1016/j.mejo.2019.05.018

Khalil, N. A., Said, L. A., Radwan, A. G., & Soliman, A. M. (2019). A universal floating fractional-order elements/memelements emulator. Novel Intelligent and Leading Emerging Sciences Conference (NILES), 2019, 80–83. https://doi.org/10.1109/NILES.2019.8909296

Khalil, N. A., Fouda, M. E., Said, L. A., Radwan, A. G., & Soliman, A. M. (2019). A universal fractional-order memelement emulation circuit. Novel Intelligent and Leading Emerging Sciences Conference (NILES), 2019, 67–70. https://doi.org/10.1109/NILES.2019.8909307

Carlson, G. E., & Halijak, C. A. (1964). Approximation of fractional capacitors (1/s) ^(1/n) by a regular Newton process. IEEE Trans. Circuit Theory., 11(2), 210–213.

Yadav, N., Rai, S. K., & Pandey, R. (2020). New grounded and floating memristor emulators using OTA and CDBA. Int J Circ Theor Appl., 48, 1154–1179. https://doi.org/10.1002/cta.2774

Acar, C., & Ozoguz, S. (1999). A new versatile building block: Current differencing buffered amplifier suitable for analog signal-processing filters. Microelectronics Journal, 30, 157–160. https://doi.org/10.1016/S0026-2692(98)00102-5

Metin, B., Pal, K., & Cicekoglu, O. (2011). CMOS-controlled inverting CDBA with a new all-pass filter application. International Journal of Circuit Theory and Applications, 39(4), 417–425.

Hartley, T. T., & Lorenzo, C. F. (1998). “A solution to the fundamental linear fractional order differential equation.” Raport instytutowy 208693, National Aeronautics and Space Administration (NASA).

P.L. Butzer, U. Westphal, “An introduction to fractional calculus, in: Applications of Fractional Calculus in Physics”, World Scientific, 2000, pp. 1–85.

B.M. Vinagre, I. Podlubny, V. Feliu, Some approximations of fractional order operators used in control theory and applications, Journal of Fractional Calculus and Applied Analysis (2000).

Krishna, B. T., & Reddy, K. V. V. S. (2008). Active and Passive Realization of Fractance Device of Order 1/2. Active and Passive Electronic Components, 369421(5), 2008. https://doi.org/10.1155/2008/369421

Pershin, Y. V., La Fontaine, S., & Di Ventra, M. (2009). Memristive model of amoeba learning. Physical Review E, 80, 021926.

Pershin, Y. V., & Di Ventra, M. (2010). Experimental demonstration of associative memory with memristive neural networks. Neural Networks, 23, 881–886.

Wang, F. Z., Chua, L. O., Yang, X., Helian, N., Tetzlaff, R., Schmidt, T., Li, C., Carrasco, J. M. G., Chen, W., & Chu, D. (2013). Adaptive neuromorphic architecture (ANA). Neural Networks, 45, 111–116.

Funding

Not Applicable.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

All authors declare that there is no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Gupta, A., Rai, S.K. & Gupta, M. A Fractional-Order Meminductor Emulator Using OTA and CDBA with Application in Adaptive Learning Circuit. Wireless Pers Commun 131, 2675–2696 (2023). https://doi.org/10.1007/s11277-023-10566-2

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-023-10566-2