Abstract

Second generation current conveyor (CCII) is a versatile fundamental building block that is used nowadays for designing of almost all kinds of current mode devises. A wide variety of CCII configuration offering diverse characteristics have been proposed in literature. However, not much effort has been put to improve the output resistance of this block. High output resistance is a very essential parameter that makes CCII a versatile block to be used in integrated circuits, without affecting its performance parameters. In this paper, an extensive survey has been carried out to explore high performance CCII topologies. Among these configurations flipped voltage follower (FVF) based class-A CCII architecture has been chosen because of its compact design, low voltage and current/voltage matching characteristics. Output resistance of this configuration has been increased by using super-cascode (SC) configuration and replacing the biasing circuitry by low voltage cascode current mirror. Small signal analysis of the proposed circuit has been carried out to mathematically validate the improvement achieved by this circuit. The proposed FVF based class-A SC-CCII offers very high output resistance while maintaining all the characteristics of FVF based class-A CCII. However, a small sacrifice has to be made in the required in supply voltage of the proposed design. The proposed CCII is simulated in LtSpice using 0.18 µm CMOS technology and is compared with various CCII configurations available in literature. The simulated results validate the high performance operation of the proposed SC-CCII and show that this block offers around 70 times increase in output resistance. The characteristic of this proposed SC-CCII makes it a versatile block to be used in wide applications with diverse characteristics.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The conventional operational amplifier (opamp) has been predominant block in analog and signal processing domain. Since the inception of idea of opmap in 1940, it has been extensively used for circuit realization and signal processing tasks. Researchers have explored its utility in designing almost each and every analog, digital and mixed mode circuit that is based on voltage mode (VM) operation. Though, it has been proved to be an effective and ingenious component in designing of circuits, however, it faces some major limitations like restricted slew rate and fixed gain bandwidth product (GBP) [1]. These features limit its performance at high frequencies.

To overcome these drawbacks, current mode (CM) approach has been introduced by researchers. In this methodology, active variable is current instead of voltage. The circuits designed using this approach do not have any high impedance node and thereby operate at high frequencies. Moreover, operation of these circuits are not restricted by GBP limitations [2]. In literature, various building blocks have been devised time to time based on CM approach. Current conveyor (CC) is one of the important blocks amongst them and was proposed in 1970 by Sedra and Smith [3]. It has been observed that CC show considerable improvements in bandwidth, power consumption, signal linearity and slew rate. Therefore, a lot of circuits have been proposed using CCs since 1970. Later on different generations of CCs have been introduced, based on its terminal characteristics [4, 5]. Due to the versatility and usage in designing basic circuits, second generation CC (CCII) has been chosen as a topic of study and investigation in the paper.

Since the introduction of CCII by Sedra and Smith in 1970, a dozen of CCII structures have been introduced in literature. Some of them are Wideband CCII [6], Controlled CCII [7], Second generation differential voltage current conveyor (DVCCII) [8], Inverting second generation current conveyor (ICCII) [9], Fully differential second generation current conveyor (FDCCII) [10], Dual-X current conveyor (DXCCII) [11], Class A CCII [12], Fully balanced current conveyor II (FBCCII) [13], Voltage and current gain second generation current conveyor (VCG-CCII) [14], CCII with low parasitic resistance Rx [15], Current controlled fully balanced second generation current conveyor (CFBCCII) [16], Differential current conveyor (DCCII) [17].

In this paper, basics of CCII have been presented in next the section. Based on the functionality and importance of the structure, some of high performance CCII topologies have been chosen for analysis and comparison. All these topologies have been discussed in detail in section 3. It has been analysed that not much work has been done to improve the output resistance of these configurations. High output resistance is very essential feature of CCII, especially when it has to be used in cascaded devices. Motivation behind this work has been to design a high performance CCII having high output resistance that can avoid any loading effect irrespective of the circuit it is used. In section 4, development of a new FVF based class-A super-cascode CCII offering very high output resistance has been presented. This CCII has been designed using super-cascode configuration at output terminal of FVF based class-A CCII and replacing the biasing circuitry with low voltage cascode current mirror. Small signal analysis has been carried out to mathematically analyse the improvement obtained in the configuration. Section 5 summarizes the simulation results of the proposed CCII and other CCII configurations discussed in section 3. These results have been obtained using LtSpice 0.18 µm technology. Finally, in section 6, the conclusions are provided.

2 Second generation current conveyor (CCII)

A second generation current conveyor (CCII) is a 3-port building module. Figure 1 shows its block diagram depicting various input and output nodes. CCIIs are generally characterized by terminal Y, which ideally has infinite input resistance. In a CCII, if a signal is applied at Y port, an identical voltage appears at terminal X. Similarly, port Z which possesses high output resistance (ideally infinite), reflects equal amount of current (IZ) as fed at terminal X [4].

The port characteristics of CCII are expressed as:

The above matrix equation describes two types of CCII: (i) CCII+ and (ii) CCII-. Basically these CCIIs are categorized by the direction of current IZ. In CCII+ polarity of IZ is same as that of IX and in CCII- this polarity gets reversed [4]. Current conveyors have been widely used in applications based on filtering. Several efforts and studies have been made in recent years to improve the design of universal filter. One such implementation involves use of three circuits of multi-output current controlled conveyors [16]. All filters namely low pass, bandpass, highpass, notch and all pass filters can be designed using current conveyors. Moreover, recently the possibilities of efficiently implementing floating inductors and inductors connected to ground using current conveyors is being explored [2]. Other important applications of CCII are: current amplifiers, voltage to current convertors, voltage and current amplifiers, integrators and differentiators, current summers, instrumentation amplifiers, full wave precision rectifiers, oscillators, etc. [3–5].

3 Various CCII architectures present in literature

3.1 Wideband CCII

WIdeband CCII was proposed by Cha and Watanabe in 1996 [6]. For signal processing under current mode using low power operation, translinear loop based wideband CCII was proposed by Ismail and Soliman in [18]. It has been observed that these translinear circuits show an outstanding current mirroring behaviour at port Z from port X for a wide range of input current. Though, their voltage mirroring property at port X from port Y is not that good and possess a high offset voltage.

The circuit of translinear loop based wideband CCII is shown in figure 2. This circuit consists of two differential pairs (M2-M4 and M1-M3). Here, the MOSFETs M3-M6 constitute first generation current conveyor (CCI). Assuming that differential pairs are perfectly matched, CCI operation of MOSFETs M3-M6, imitates the potential at source voltage of MOSFET M4 at the source terminal of M3. This arrangement ensures current across MOSFET M4 to be same as that flowing across M3 and make it independent of voltage Vy, applied at gate terminal of M2. Moreover, equal currents across M1 and M2 (due to similar biasing of MOSFETs M7 and M8) and their similar source potentials lead to transfer of voltage Vy quite successfully at node X.

Wideband CCII circuit [18].

Furthermore, this arrangement causes current at node X to be mirrored at node Z without any help from current mirrors. Moreover, it is noticed that Vy is exactly followed by Vx and Vz is always greater than (Vds2,sat + Vy) for legitimate operation.

The circuit shown in figure 2, does not hold any high impedance node and thereby offers wide bandwidth. This wideband CCII circuit consists of a few transistors and has a very compact design. It consumes low power and is able to operate for a very wide range of frequencies. This wideband CCII is extensively used in high frequency applications, in designing of universal filters, sinusoidal oscillators, etc.

3.2 Flipped voltage follower based class-A CCII

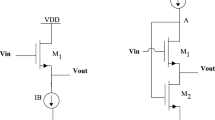

Class-A CCII circuit was proposed by Naik et al in 2010 [12]. The architecture of this CCII is based on flipped voltage follower (FVF) current mirror and is shown in figure 3. FVF is basically an enhanced buffer cell that is widely employed for low voltage operations. Applications of FVF include multipliers, CCIIs, mixers, etc.

FVF based Class-A CCII [12].

In CCII circuit shown in figure 3, MOSFETs MN1 and MN5 form the FVF cell. The required biasing current is provided by MOSFET MP1 and required gate voltage at MN5 is obtained via diode connected MOSFET MN4. Here, MOSFETs MN6 and MN7 are connected as current sink load. In this circuit, since MOSFETs MP1, MP2 and MP3 have same gate and source voltages, therefore they have same drain currents (say Ib). The architecture of this circuit ensures the same current (Ib) to flow across MN6 as well. This finally leads to similar current at nodes x and Z, that is Iz=Ix. Furthermore, this leads to Vx=Vy.

It is readily observed that complexity of the circuit is quite less and a precise voltage mapping is obtained from Y to X terminal. In this class A CCII circuit, current mirroring from node X to node Z is also satisfactory. Furthermore, this circuit offers numerous advantages like compact design, good slew rate, high output impedance and quite good operating range for both current and voltage. This circuit can readily be used to implement different types of filters, current amplifiers, instrumentation amplifiers, etc. [3, 12, 19].

3.3 Controlled current conveyor II (CCCII)

The controlled CCII (CCCII) was proposed by Fabre et al in 1995 [7]. CCCII has 3 nodes X, Y and Z. Its terminal current and voltage equations are given as:

The circuit of CCCII is shown in figure 4. In this configuration one can electronically change the resistance seen at X terminal, hence the name controlled current conveyor (CCCII) [4, 5]. The circuit of CCCII mainly consists of a translinear loop (M1-M4) and a few current mirrors. Routine analysis of the circuit, considering current mirror action at different places, offers:

Current controlled conveyor (CCCII) [7].

here, Ib is the biasing current flowing across MOSFETs M8 and M9 and Ix is current injected in terminal X. Now, current mirror formed by MOSFETs M12 and M13 leads to current at Z terminal equal to IX. Furthermore, the circuit configuration leads to Vx=Vy.

The circuit offers numerous advantages like: it requires low supply voltage, it operates on a wide range (for both current and voltage), it has good slew rate and it also offers low input impedance. This circuit can be used in high frequency applications, like in designing universal filters, sinusoidal oscillators, etc. [3, 5].

3.4 CCII implementation with low parasitic resistance Rx

Translinear loop based CCII shows the best high frequency performance while offering a high control on the design characteristics. To further improve the operating frequency of these translinear loop based CCII, a new implementation of CCII with low parasitic resistance at node X (Rx), was proposed by Dorra Sellami et al in 2004 [15]. Its circuit is given in figure 5.

CCII with low parasitic resistance at node X [15].

Here, signal path for current has been separated from CCII current conveying path. This has been done by generating a new current transfer signal path between X and Z terminals, with the help of a current mirror. A voltage amplifier is used to lower the impedance at port X. Care has been taken to make the gain of this voltage amplifier dependent on controlling current of translinear loop. This helps in providing greater flexibilities to the designed structure. The architecture of Controlled CCII is shown in figure 5, mainly consists of a translinear loop (M1-M4) and a few current mirrors. Due to current mirror configuration, current through MOSFETs M9, M10 & M15 is same and current through MOSFETs M11, M12, M13 & M14 is also same. Moreover, same current is achieved in M7-M8 and M5-M6. These current mirrors and translinear loop ensure Iz=Ix and Vx=Vy.

Along with providing low parasitic resistance at port X, this CCCII offers numerous advantages like low power consumption, low input impedance and very good performance at high frequencies. This circuit can be used for design applications operating at high frequencies, including current controlled oscillators and fully integrable tunable band pass filters, etc.

3.5 Differential CCII (DCCII)

DCCII was first proposed by Metin et al in 2012 [17]. It has a unique current differencing property extracted from CCII’s conventional models. DCCII architecture has been presented in figure 6 [17]. It has 3 input terminals (XP, XN and Y) and 1 output terminal (Z). In DCCII, difference of current at terminals XP and XN is replicated at Z terminal. Matrix equation describing the port behavior of DCCII is given by Eq. (4).

DCCII [17].

DCCII architecture is constituted by 3 sub-circuits. Mixed translinear loop formed by MOSFETs M8–M13 forms the core section of DCCII architecture. This loop helps in replicating the potential of terminal Y to other 2 inputs terminals (XN and XP). Current differencing is achieved through MOSFETs M14-M21. This sub-circuit replicates the difference of current flowing at XN and XP at terminal Z. Biasing required by the complete circuit is done by MOSFETs M1-M7.

This architecture of DCCII offers various advantages like providing an additional voltage terminal with high input resistance that makes it suitable for cascading operations. DCCII has been used in numerous applications like in square wave generators, various amplifiers, etc. [17].

4 Proposed FVF based class-A super-cascode CCII (SC-CCII)

FVF based class-A CCII shown in figure 3 is a compact current conveyor capable of performing at low supply voltage. It has a simple and compact structure that provides a precise voltage mapping from Y to X terminal. It also offers a satisfactory current mirroring from node X to node Z. Furthermore, this circuit offers numerous advantages like good slew rate, high output impedance and quite good operating range for both current and voltage.

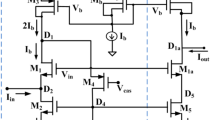

However, output impedance offered by this circuit is not very high. This impedance can be increased by employing negative feedback. Super cascode configuration proposed in [20] can be used to improve the output resistance, without increasing the required supply voltage. Complete circuit of the proposed FVF based class-A super cascode CCII (SC-CCII) is shown in figure 7. In this circuit, MOSFETs MN8 and MN9 constitute the super cascode configuration and form the biasing circuitry for these super-cascode MOSFETs. Here, MN9 is the output cascode MOSFET. MN8 helps in driving the gate terminal of this cascode MOSFET, by supplying the required polarity of the signal at its gate terminal [20, 21]. MOSFETs MP4, MP5, MP11 and MP12 help in proper biasing of these MOSFETs. In the proposed configuration, to achieve the required goal, biasing circuitry of FVF based class-A CCII has been replaced by low-voltage cascode current mirror [22]. This configuration has been chosen to obtain high output resistance of biasing circuitry when seen from ‘Z’ terminal. This is required to get the expected improvement in output resistance, as resistance of biasing circuitry will appear in parallel. Proposed configuration helps in achieving very high output resistance at the output terminal, while maintaining the class-A response of FVF based CCII. However, this circuit needs a slightly higher supply voltage due to cascode configuration of current mirror. To maintain nowadays demand of low supply voltage operation, in the proposed configuration low voltage cascode current mirror has been used. This current mirror helps in attaining high output resistance with small sacrifice in voltage headroom [22]. The improvement achieved in output resistance of the proposed architecture is directly proportional to the gain provided by feedback path formed by cascode MOSFET MN9 and driving MOSFET MN8. Mathematical analysis for this circuit has been presented in sub-section 4.1.

4.1 Output resistance

Equivalent small signal model for deriving output resistance of the proposed CCII configuration has been shown in figure 8.

The low-frequency small-signal model for calculating output resistance of the proposed Class-A SC-CCII, looking from Z terminal (Rz) is shown in figure 8. This equivalent circuit has been drawn considering zero input signals at Y and X terminals. For this, the signal sources present at Y and X terminals have been replaced by their effective internal resistances. Here, gm represents transconductance and r0 represents small signal output resistance of the corresponding MOSFET. RO_CAS represents the output resistance of cascode current mirror and can be given as:

Above equation has been derived assuming all PMOS transistors forming current mirror configuration are symmetrical and considering for a MOSFET, gmr0>> 1 [23].

In the circuit, terminals marked DN8 and DN3 are the drain terminals of MOSFETs MN8 and MN3, respectively. SN9 node represents source terminal of MOSFET MN9. All these nodes have been numbered as well, in order to write mathematical expressions related to the circuit with more clarity. Voltage difference between any 2 terminals is marked as Vij, where ‘i’ and ‘j’ represents the 2 nodes.

From small signal circuit shown in figure 8,

To calculate Rt, a test voltage source (Vt, shown dotted in figure) has been connected at Z terminal and analysis has been carried out to find current It. Routine analysis of this small signal model gives equations as follows:

Eq. (9) shows that if RO_CAS is very high, then no current will flow in this branch and V3 ≈ V2.

Simplifying Eqs. (7) – (10), Rt can be obtained as:

Considering for a MOSFET, gmr0>> 1 [23], Eq. 11 can be simplified to:

Combining Eqs. (5), (6) and (12), RZ can be calculated as:

Eq. (13) shows that output resistance seen from terminal Z, looking towards base circuit observes an improvement of approximately gmN9r0N9·gmN8r0N8, due to super cascode configuration and that looking towards biasing circuitry observes an improvement by a factor of gmPr0P. The component with lower value will dominate RZ. This improvement is very significant and will help the circuit designers to use CCII effectively in their devices. Further, it has been observed that if biasing circuitry has very high output resistance, then super cascode configuration used in the proposed CCII can provide output resistance in hundreds of MΩ. Since a lot of research has been done for improving output resistance of a current mirror, various current mirror configurations with high output resistance are available in literature [21, 24]. Choice of the current mirror to be used will depend on the requirement of the circuit designer and will greatly help in improving the overall output resistance of the proposed CCII architecture.

5 Simulation results and analysis

In this section, simulation results of various CCII architectures have been presented. All the CCII architectures have been simulated in Ltspice using 0.18µm CMOS technology. To get a fair comparison among the results of different circuits, they have been simulated using same technology with W/L ratios of all MOSFETs of various architectures are summarized in table 1.

5.1 DC analysis

In this sub-section, DC analysis of the proposed CCII architectures has been shown and its comparison with other CCII architectures reported in literature has been presented. The current characteristics of the proposed circuit has been analysed by applying a varying DC current at input port X (Ix) and observing the variations in current at output port Z (Iz). The simulation results obtained in this case has been shown in figure 9. From this figure it can be observed that in the proposed CCII, Iz follows Ix with high accuracy for input current range of −500 µA to +500 µA. For comparison with other CCII architectures present in literature and discussed in the paper, DC simulations for these configurations have been carried out using aspect ratios listed in table 1. The operating current range obtained through simulations for these topologies have been mentioned in table 2. It has been analysed that the operating current range is maximum for the proposed FVF (±500 µA) based class-A SC-CCII. Further, curve showing % error in output current (Iz) of the proposed FVF based class-A SC-CCII has been plotted in figure 10. This curve shows that the proposed CCII works for the entire operating current range with a maximum % error of ±0.9%. This error being maximum at input current (Ix) close to zero due to division by near zero values of Ix.

To verify the voltage operation of the proposed CCII, the variations in voltage at X terminal with that of voltage at Y terminal have been plotted in figure 11. This figure shows that Vx follows quite closely to Vy for a wide range of −500 mV to +500 mV. Similar curves for other CCII configurations have been obtained with the corresponding results tabulated in table 2. These results justify the wide operating voltage range of the proposed CCII architecture. To confirm the tracking of voltage at port X to the voltage applied at port Y, % error in Vx has been plotted in figure 12. This figure shows that Vx closely follows Vy with a maximum % error of ±0.9%. The error being maximum at input voltage (Vy) close to zero due to division by near zero values of Vy.

5.2 AC analysis

In this sub-section, AC analysis of the proposed CCII architecture has been presented and comparison with other CCII configurations discussed in the paper has been presented. AC Analysis has been done for a frequency range of 10 Hz to 5 GHz. Frequency plots for current gain and voltage gain of the proposed class-A SC-CCII have been shown in figures 13 and figure 14, respectively. From these curves it is observed that −3 dB bandwidth for the proposed CCII configuration is 20 MHz and 25.43 MHz for current gain and voltage gain, respectively. For comparison, respective bandwidths of other CCII architectures obtained through simulations have been listed in table 2. These values show that bandwidth of the proposed CCII architecture is lower in comparison to other CCII architectures. This is due to the high output resistance of the proposed architecture.

Main objective of the proposed CCII configuration has been to achieve a good design having high output resistance. Output resistance of the proposed architecture observes a significant boost compared to rest of the high performance architectures discussed in the paper. This improvement achieved in present design can be observed form the output resistance (Rz) waveforms shown in figure 15. This waveform clearly shows that the proposed design offers very high output resistance of the order of MΩ. The improvement observed in output resistance is due to super-cascode configuration used in the proposed configuration. Plot for input resistance looking through X terminal is shown in figure 16. This curve shows that input resistance of the proposed CCII is quite low (1.12 kΩ). Simulations for other CCII configurations have been carried out and the respective values of their output and input resistances have been summarized in table 2. From this table it can be analysed that the proposed architecture significantly increases the output resistance from a few kΩs to MΩ range. This has been the main contribution of the proposed CCII and is achieved due to super-cascode configuration used in this circuit.

5.3 Transient analysis

Transient analysis of the proposed CCII architecture has been shown in this sub-section. A pulse signal of 25 MHz frequency has been applied at X terminal. The output obtained for a capacitive load of 1pF for the proposed CCII has been shown in figure 17. Positive slew rate (SR+) is calculated by observing the slope of the rising edge as shown in the figure. Similarly, negative slew rate (SR−) is calculated by observing the slope of falling edge of the waveform. Slew rates for other CCII configurations have also been calculated with the help of simulations and all these resultant parameters are listed in table 2. These values show that the slew rate of all the CCII configurations discussed in the paper are approximately similar with DCCII having the lowest slew rate.

6 Conclusion

Various high performance CCII topologies have been analysed and implemented in this paper. It has been observed that output resistance of these topologies is not sufficient for CCII to be used as a versatile block for implementing different circuits. FVF based class-A SC-CCII configuration has been designed and proposed in this paper. This proposed circuit utilizes super cascode configuration at output terminal (Z) to increase resistance seen through this node. Moreover, to achieve the required goal in the proposed CCII, biasing circuit is replaced with low voltage cascode current mirror. Small signal analysis mathematically justifies the improvement in output resistance. Simulations for the proposed CCII have been carried out in LtSpice using 0.18 µm technology. Moreover, the proposed CCII is compared with the existing high performance CCIIs. It has been observed that the proposed CCII offers maximum output resistance of 2.44 MΩ. Further, the proposed CCII operates for ±500 µA current range and ±500 mV voltage range. It offers 20 MHz current-gain bandwidth 25.43 MHz voltage-gain bandwidth and 89.83 V/µs slew rate with CL of 1 pF. This proposed SC-CCII will prove to be an important block for designers working in the area of high performance integrated circuits.

Abbreviations

- CCII:

-

Second generation current conveyor

- FVF:

-

Flipped voltage follower

- SC:

-

Super-cascode

- Opamp:

-

Operational amplifier

- VM:

-

Voltage mode

- GBP:

-

Gain bandwidth product

- CM:

-

Current mode

- CC:

-

Current conveyor

- DCCII:

-

Differential second generation current conveyor

- CCCII:

-

Controlled current conveyor II

References

Franco S 2015 Design with operational amplifiers and analog integrated circuits. 4th edn. Mc Graw Hill Education, India, pp. 1–66

Salem S B, Fakhfakh M, Sellami D, Loulou M, Loumeau P and Masmoudi N 2006 A high performance CMOS CCII and high frequency applications. Analog Integr. Circuits Signal Process. 49: 71–78

Sedra A S and Smith K C 1970 A Second generation current conveyor and its application. IEEE Trans. Circuit Theory 17: 132–134

Senani R, Bhaskar D R and Singh A K 2015 Current conveyors: variants applications and hardware implementations. Springer, Switzerland, pp. 3-16, 255-313

Hassen N, Ettaghzouti T and Besbes K 2011 High performance second generation controlled current conveyor CCCII and high frequency applications. WASET Int. J. Electron. Commun. Eng. 5: 1764–1773

Cha H W and Watanabe K 1996 Wideband CMOS current conveyor. Electron. Lett. 32: 1245–1246

Fabre A, Saaid O, Wiest F and Boucheron C 1995 Current controlled bandpass filter based on translinear conveyor. Electron. Lett. 31: 1727–1728

Pal K 1989 Modified current conveyors and their applications. Microelectron. J. 20: 37–40

Awad I A 1999 Inverting second generation current conveyors: the missing building blocks, CMOS realizations and applications. Int. J. Electron. 86: 413–432

El-Adawy A A, Soliman A M and Elwan H O 2000 A novel fully differential current conveyor and applications for analog VLSI. IEEE Trans. Circuits Syst. II 47: 306–313

Zeki A and Toker A 2003 The dual-X current conveyor (DXCCII): a new active device for tunable continuous-time filters. Int. J. Electron. 89: 913–923

Naik A P and Devashrayee N M 2010 A compact second generation current conveyor (CCII). In: International conference on advances in recent technologies in communication and computing, pp. 20–24

Alzaher H A, Elwan H and Ismail M 2003 A CMOS fully balanced second-generation current conveyors. IEEE Trans. Circuits Syst. II 50: 278–287

De Marcellis A, Ferri G, Guerrini N C, Scotti G, Stornelli V and Trifiletti A 2009 The VCG-CCII: a novel building block and its application to capacitance multiplication. Analog Integr. Circuits Signal Process. 58: 55–59

Masmoudi D S, Salem S B, Loulou M and Kamoun L 2004 A radio frequency CMOS current controlled oscillator based on a new low parasitic resistance CCII. In: International conference on electrical, electronic and computer engineering, ICEEC '04, pp. 563–566

Chunhua W, Yang L, Qiujing Z and Yu F 2010 Systematic design of fully balanced differential current-mode multiple-loop feedback filters using CFBCCII. Radioengineering 19: 185–193

Metin B, Herencsar N and Vrba K 2012 A CMOS DCCII with grounded capacitor based cascadable all-pass filter application. Radioengineering 21: 718–724

Ismail A M and Soliman A M 1998 Wideband CMOS current conveyor. Electron. Lett. 34: 1245–1246

Surakampontorn W, Riewruja V and Cheevasuvit F 1991 Integrable CMOS-base realization of current conveyors. Int. J. Electron. 71: 793–798

Torralba A, Carvajal R G, Ramirez-Angulo J and Munoz E 2002 Output stage for low supply voltage, high-performance CMOS current mirrors. Electron. Lett. 38: 1528–1529

Aggarwal B, Gupta M, Gupta A K and Bansal S 2013 A novel very high performance current mirror for CMOS technology. Analog Integr. Circuits Signal Process. 75: 67–74

Razavi B 2008 Design of analog CMOS integrated circuits. 2nd edn. Tata Mc-Graw Hill, New Delhi, pp. 134-172

Gregorian R and Temes G C 2008 Analog MOS integrated circuits for signal processing. Wiley, New Delhi, pp. 64-120

Aggarwal B, Gupta M and Gupta A K 2016 A comparative study of various current mirror configurations: topologies and characteristics. Microelectron. J. 53: 134–155

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Rights and permissions

About this article

Cite this article

Aggarwal, B., Yogi, N., Ahmad, I. et al. A new very high output resistance FVF based class-A super-cascode CCII. Sādhanā 47, 23 (2022). https://doi.org/10.1007/s12046-021-01803-0

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s12046-021-01803-0