Abstract

In this work, both the Al-(p-Si) (MS) and Al-(Al2O3:PVP)-(p-Si) (MPS) structures were grown onto the same p-type Si wafer in the same conditions to determine the (Al2O3:PVP) organic-interlayer whether the MPS build improves performance or not. For this aim, first, X-ray diffraction (XRD) and field-emission scanning electron microscopy (FE-SEM) was used to investigate the structure of the (Al2O3-PVP) inter-layer. Secondly, both the current–voltage (I–V) and capacitance/conductance-frequency (C/G)-f measurements of them were performed at ambient temperature to the comparison of their electric and dielectric properties. Energy-dependence profile of surface states (Nss) was extracted from the positive bias I–V data by considering the voltage-dependence of BH and n. We found that the (Al2O3: PVP) inter-layer leads to a decrease in surface-states (Nss), ideality-factor (n), leakage-current, series-resistance (Rs), and increase in barrier (BH), shunt resistance (Rsh), rectification-ratio (RR = Ifor./Irev. at ± 6 V). Dielectric permittivity and loss (ε′, ε″), loss-tangent (tan δ), real & imaginary components of electric modulus (M′, M″), and ac-conductivity (σac) were extracted from the C-f and G-f measurements in the wide frequency range of 200 Hz-1 MHz at 1.5 V. The observed higher values in the ε′ and ε″ at lower frequencies for MS and MPS structures were attributed to the Nss and easy polarization of interlayer under electric field.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

It is essential to improve cost-effective and high-performance semiconductor devices rather than traditional metal–semiconductor (MS) type structures using an inter-layer at the M-S interface by growing various simple and cheap methods. Therefore, a recent publication from research groups concentrates on the increase in the performance of MS structures by combining doped metal and metal-oxide materials with an interfacial polymer layer [1,2,3,4,5,6,7,8]. Drop-coating, dip-coating, ink printing, spraying, electrospinning, sol–gel, and spin coating are all methods for growing a thin polymer film [6,7,8]. Among them, polyvinyl-pyrrolidone (PVP) and polyvinyl-alcohol (PVA) has essential and valuable properties like easy processability, low toxicity, high water-solubility, and good chemical, thermal, and mechanical stability [9,10,11,12,13,14]. Because nanoparticles have a large aspect ratio, the substantial inter-layer area at the matrix/nano-filler interface is also a field of research in nanocomposites. The grown organic (polymer) inter-layer at the M/S interface, MS transforms to MPS type structure. It is anticipated that the chosen high-dielectric polymer or its composites as interfacial-layer can minimize the Nss, leakage current, Rs, and high BH, Rsh, RR, and controllable the current-transport-mechanism (CTMs) [1, 4, 5, 7,8,9, 15].

In this study, sapphire (Al2O3) is also a unique optical material with a large transmittance window from ultraviolet to mid-infrared [16]. Therefore, it is utilized in photonics, optoelectronic devices, and nano-optics because of its robust and outstanding dielectric properties [17]. Alumina also has various polymorphs, such as γ, θ, and α, and is the most widely used α-Al2O3. The crystalline α phase is the most stable among other polymorphs, but metastable phases such as γ and θ also occur during phase transitions and reactions. Therefore, in this study, the (Al2O3:PVP) interlayer was performed on the p-Si wafer by the sol–gel method, which has a low cost, low temperature process, and accessible technology preferred to synthesize the high purity Al2O3 composite. This method has low cost, low temperature process, and accessible technology to perform high purity Al2O3 composite [18, 19].

In this work, we utilized and performed the electric and dielectric characteristics of the Al-p-Si (MS) and Al-(Al2O3:PVP)-p-Si (MPS) structures on the same p-Si wafer to determine the effect of (Al2O3:PVP) interlayer on these characteristics. First, the structural analysis of the (Al2O3-PVP) nanocomposite was analyzed using XRD and FE-SEM. Then, these two structures’ I–V and (C/G)-f measurements were performed at ambient temperature. According to experimental data, the chosen (Al2O3:PVP) interlayer reduces Nss, leakage current, and Rs while increasing BH, Rsh, RR, and more significant electrical charges or energy storage. The results contribute to improving the performance of the MPS diode. Our findings show that the use of (Al2O3-PVP) organic interfacial layer can effectively replace traditional insulator layers and also it has many advantages: low cost, low energy consumption during growing processes, low molecular weight, high-dynamic stress, charge storage capability, and flexibility.

2 Experimental details

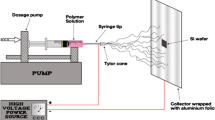

In this paper, Al-p-Si (MS) and Al-(Al2O3:PVP)-p-Si (MPS) structures were grown onto a p-Si wafer (Boron doped) with < 100 > orientation, 2-inch diameter, ∼300 μm thickness, and 1–10 Ω cm resistivity. Firstl, the wafer was cleaned in acetone at 60 °C, methanol, and rinsed in distilled water for five min. in an ultrasonic bath. Then, it was cleaned in an 80 °C solution of H2O, H2O2, and NH4OH (7:1:1) and finally cleaned using (HF: H2O) (1:7) solution and rinsed in distilled water, and then the wafer was placed in the deposition chamber. Second, for the fabrication processes, high pure (99.999%) Al with 100 nm thickness was thermally evaporated onto the whole back-side of the wafer at 10–6 Torr. Afterward, the p-Si/Al wafer was annealed at 500 °C in nitrogen ambient to achieve a better ohmic contact. The p-type Si wafer was divided into four quarters with a crystal cutter to perform both MS and MPS structures. The high pure Al-dots (with 1.4 mm radius and 100 nm thickness) were thermally grown onto the first piece of p-Si wafer. Hence, the fabrication of Al/p-Si (MS) structures was completed. After that, the MPS with MS structures and Al2O3 nanostructures were synthesized to compare. For this purpose, the Aluminum-nitrate (Al(NO3)3.9H2O) and Ammonia solution (NH3) purchased from the Loba Chemie were used.

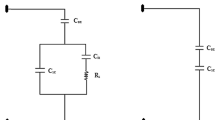

A thin layer of (Al2O3:PVP) was produced and then placed on the p-Si wafer using a spin coating process to prepare Al/(Al2O3:PVP)/p-Si structures [20]. In an ultrasonic bath, 10 mg of Al2O3 nano-powder was dissolved in 5 ccs of PVP solution, yielding a thin (Al2O3:PVP) 5 percent solution of PVP polymer. Then, the produced (Al2O3:PVP) composite was coated on the top-surface p-Si wafer using a spin coating process. The fabrication of Al/(Al2O3:PVP)p-Si (MPS) structures was then completed by thermally evaporating high-purity Al dots with the same area and thickness onto (Al2O3:PVP)/p-Si wafers. Figure 1a, b depicts the synthesis stages for Al2O3 nanostructures and the processing methods for Al/(Al2O3:PVP)/p-Si structures.

The produced MS and MPS structures were mounted on the Cu holder using a silver (Ag) paste, and the electrical probes were made with silver-coated Cu wires to perform I–V and (C/G)-f measurements. XRD (Philips X pert, Netherlands) was used to study the structural properties of produced nanostructures using Cu K radiation (= 1.5406) as an X-ray source, with 2θ ranging from 10° to 80°. Surface topography examined FE-SEM (Tescan-Mira III, Czech Republic). More information on the XRD and FE-SEM can be found in [21]. Optical Analysis of Al2O3 nanostructures was done using an Ultraviolet–visible spectroscope (UV-1800, Shimadzu, Japan). The distinctive spectrum absorption peak at 265 nm/4.7 eV in the range can be attributed to Al2O3 intrinsic band-gap absorption. The energy gap was also determined from the (αhν)2-hν plot, and the band-gap value of Al2O3 nanostructures for direct transitions was found as 4.9 eV. The I–V measurements were done by a Keithley 2400 I–V source meter, and Z–f including C–f and G/ω–f measurements were done by a KEYSIGHT (E4980Al 20 Hz–1 MHz).

3 Results–discussion

3.1 Electrical properties

The semi-logarithmic I–V curves of the MS and MPS structures are given in Fig. 2. This figure shows that these two structures have linear regions at moderate bias voltage and then deviate from the linearity owing to Rs and interfacial layer at the semiconductor/metal (S/M) interface. Due to the depletion layer, RS, and the interlayer will share the voltage provided to the diode. However, in the reverse bias region, the current increases gradually with the voltage bias, and this is an undesirable situation. This non/soft-saturation behavior was attributed to the tunneling via surface states, image-force lowering of BH, barrier in-homogeneities between semiconductor and metal, and lower shunt resistance values (Rsh) [5, 7, 13].

Since the applied voltage is higher than 3 (kT/q) and the diode has both a series resistance and ideality factor higher than unity, the charge carries flow through the BH of the diode obeys the TE theory at room or above temperature as given below [7, 22].

In Eq. 2, A*, ФBo, k, T, and q, are the Richardson constant (= 32 A(cm K)2) for p-Si [23, 24], respectively, the effective barrier height (BH), Boltzmann’s-constant, the temperature (in Kelvin), and the electron charge, respectively. Here, the term in front of the square brackets is the saturation current (Is) and can be determined from the intercept of the ln(I)–V plot at V = 0. On the other hand, the value of the ideality factor (n) can also be calculated from the slope ln(I)–V curve by applying relation [7, 22, 25].

After the obtained value of Is, the value of ΦBo can be calculated using the Schottky contact area (A) following relation [22, 23].

Thus, the obtained Is, n, ФBo values from the linear sections ln(I)–V plot and RR at ± 6 V of the fabricated MS and MPS structures were calculated using forward bias I–V data based on TE theory and have also been reported in Table 1. The electrical properties or current-transport mechanisms (CTMs) of the MS, MIS, or MPS type Schottky-diodes/structures depend on many factors such as the barrier-inhomogeneity, native or deposited an interlayer at the M/S interface, surface-states (Nss), the concentration level of doping atoms into semiconductor or depletion layer width (Wd). Surface-states with energies located in the band gap of semiconductors act as recombination centers that can capture or release some electrons. According to Card and Rhoderick, these traps may be occurred by unsaturated dangling bonds of the surface atoms and some organic contaminations in a laboratory environment [23, 26]. According to Eq. 2, the value of n may be approximated to the ideal case (n = 1) using a high-dielectric interlayer and so passivated the level of Nss. The existence of barrier inhomogeneity at the M/S interface with many lower barriers, patches, or pinch-off at around mean BH is also more effective on the CTMs through the barrier. Thus, the value of current and so n become increased. Therefore, as seen in Table 1, the obtained values of n are much higher than the ideal case. The higher value of n was attributed to the inter-layer thickness (δ) and its permittivity (εi), surface-states (Nss) located at the junction, and depletion-layer thickness (WD), as shown in Eq. 3. BH formation in-homogeneity is another reason for a higher value of n [26,27,28,29,30].

The non-linear region in the forward bias of these diodes I–V characteristics (Fig. 3) results from Rs and interlayer. However, in both linear and non-linear forward bias regions, the BH and n are critical. Because they are dependent on voltage as well as temperature/illumination. Moreover, if the I–V curve is not sufficiently linear, the accuracy and reliability of these calculated parameters become questionable. Therefore, Cheung & Cheung proposed a new method utilizing the following relations to obtain the n, BH, and Rs values in a second way [24, 26].

The dV/dln(I) vs. I and H(I) vs. I curves of the fabricated MS and MPS structures, respectively, are shown in Fig. 3a and b. As seen in Fig. 3, these figures have good linear parts in a broad range of forwarding currents. According to Eq. 4a and b, the intercept and slope of the dV/dln(I)-I plot gave us the n.(kT/q) and Rs, respectively. The H(I) vs. I plot was generated for these two diodes that use this value of n in Eq. 4b. After that, the intercept and slope of this plot gave us the value of (n.ФB) and the second value of Rs, respectively. In this way, the obtained values of n, BH, and Rs are also tabulated in Table 1. These essential electrical characteristics acquired from the TE and Cheung & Cheung functions are in agreement and suitable for MIS or MPS type structures, as illustrated in Table 1. The voltage and the computation method account for the little discrepancies between these parameters [5, 22, 23, 31] (Fig. 4).

In MS, MIS, and MPS type diodes/structures, the Norde method can also calculate the Rs and BH value [32]. For cases where the ideality factor is considerably more significant than the ideal case (n > > 1), Bohlin has modified the Norde function as follows [33]. The F(V)–V plots for MS and MPS type diodes were obtained from Eq. 5a. According to the Norde method, the F(V)–V curve must pass through a minimum at moderate forward bias voltages if the diode has a series resistance.

Here, γ is a dimensionless constant and must be chosen bigger than n. As shown in Fig. 6, F(V) vs. V plots for two different structures have a minimum point corresponding to Imin or Io current and Vmin or Vo voltage. The values of Rs and BH (ΦB) were calculated via relations by these equations:

Using Eq. (5b) and (c); the values of Vo, Fo, ФB, and Rs were found as 0.680 V, 0.630 eV, 0.702 eV, and 3.2 kΩ for MS structure and 0.635 V, 0.700 eV, 0.801 eV, and 15.8 kΩ for MPS structure, respectively.

As shown in Table 1, the electrical parameters of the MS and MPS type structures depend on the calculation method equaled to the different forward applied bias voltage. In other words, all these electrical parameters are dependent on voltage and temperature. Because while standard TE theory is valid for intermediate bias voltage, Norde and Cheung functions are valid around the concave curvature of the semi-logarithmic I–V plots, as shown in Fig. 2. In addition, the values of Io, leakage current, and n for the MPS structure are less than that for the MS structure, Rsh, RR, and BH values are higher. On the other hand, Rs for the MPS structure is higher than MS structure and its effect in the linear part of the lnI–V plot can be ignored. Rs is active in enough high forward voltage regions and causes the lnI–V curve to deviate from highly non-linearity. The applied voltage in this region will be shared by the depletion layer, polymer interface layer, and Rs. In other words, the high series resistance value can be rooted in the interfacial layer, its homogeneity, space-charge injection, and interface states or dislocations.

These results show that the high-dielectric (Al2O3:PVP) inter-layer between semiconductor and Schottky contacts increases MPS structure performance compared to MS structure.

Surface states are usually rooted in the dangling bonds at the interlayer-semiconductor and during the cleaning and fabrication processes and their energy levels in the band-gap (Eg) of semiconductors. They affect both the I–V and Z–f characteristics. These states/traps act as recombination centers. So that they can capture some electrons if they are empty and release them if they are trapped under appropriate forward applied bias. Therefore, these states regulate the charge transfer between metal and semiconductors depending on interfacial layer thickness. They are in equilibrium metal if the interfacial layer thickness is less than 3 nm, and they are in equilibrium semiconductors if it is greater than 3 nm [5,6,7, 23]. The Nss–(Ev–Ess) profile was also obtained from the forward current and voltage data in this investigation by taking voltage-dependent n(V) and ФB(V) into account, as shown below [23]:

Here, α is equal to dΦe/dV or (1–n(V)−1), Фe is the efficient BH and \(\varepsilon_{i}\) is the permittivity of the interlayer. Thus, the Nss − (Ess − Ev) profile of the MS and MPS type structures was plotted using Eq. (6a)–(c) and given in Fig. 5. As shown in Fig. 5, the Nss values substantially increased from the mid-gap of p-Si to the top of the valance band (Ev). The value of Nss for MPS is considerably lower than the conventional MS structure because of the passivation of some surface states using (Al2O3:PVP) organic interlayer between Al and p-Si semiconductor.

The forward double-logarithmic IF–VF and reverse ln(IR) vs. √VR plots were generated and given in Fig. 6a and b, respectively, to investigate the current-transport mechanisms (CTMs) in the MS and MPS type structures. As illustrated in Fig. 6a, the double logarithmic IF–VF for the Al/(Al2O3:PVP)/p-Si structure has three different segments with different slope (m) and intercept points which is proportional to the I ~ Vm power law. The value of m was obtained as 1.10, 3.18, and 1.87, corresponding to low, intermediate, and higher bias voltages, respectively. At lower forward bias voltages, m (= 1.10) is considerably lower than 2, so the dominant CTM for low forward bias voltages is ohmic voltages.

Surface states fill up as the number of injected electrons increases. At higher bias voltage, m (= 1.87) is closer to 2, so the dominant CTM is space charge limited-current (SCLC) due to the strong electron injection. On the other hand, the ln(IF)–ln(VF) plot has only two linear segments at low and higher voltages. The value of m was found as 1.12 and 2.32 in these regions, which indicated that ohmic and SCLC mechanisms are dominated in these regions, respectively. These results show that the CTM may depend considerably on applied bias voltage, interfacial layer, and Rs. As a result, to investigate the effective CCMs of MS, MIS, or MPS type Schottky diodes (SDs) in the whole forward bias voltage, the ln(IF)–ln(V) plot should be drawn as shown in Fig. 6a. As shown in Fig. 6a, both the MS and MPS type SDs have different linear parts with different slopes (m) and intercepts. This linearity indicates the power-law behavior, which is the I ~ Vm relationship between V and I. The m value is corresponding to the double-logarithmic IF–VF. This difference between MS and MPS SDs is the result of interlayer and a special distribution Nss at the native/deposited interlayer/semiconductor interface. These obtained m values for each region can be explained as follows [1,2,3, 34, 35]: (a) When the value of m is close to unity (~ 1), then Ohmic behavior is effective CCM due to the thermally generated carriers. (b) When the value of m for two SDs is closer to two, then the strong electron injection may occur and hence they contribute to the SCLC. (c) When the value of m is considerably greater than two, then dominant CCM has been interpreted as TCLC because many injected electrons lead to the filling of surface states or traps.

Additionally, to investigate the CTMs in the reverse bias region, semi-logarithmic ln(IR)–(VR)0.5) plots for the MS and MPS type structures are given in Fig. 7b. Generally, Poole Frenkel (PF) or Schottky emission (SE) mechanism CTMs may dominate. The reverse current for the PF and SE is given as follows, respectively [34, 36].

In Eq. (7a) and (7b), βPF is the PF field decreasing coefficient; βSC is the SE field decreasing coefficient; d is the interlayer’s thickness, and εr is its permittivity. According to Eq. (7c), the βPF is twice βSC, and the value of \(\beta\) can be derived from the ln(IR)–√VR curve for two types of diodes. The theoretical values of βPF and βSC were determined to be 3.89 × 10–5 and 1.95 × 10–5 (m.V)0.5/eV for MS, 2.53 × 10–5 and 1.26 × 10–5 (m.V)0.5/eV for MPS type diodes, respectively. Figure 7b shows that the semi-logarithmic IR-(VR)0.5 plot has a strong linear regime for the MS and MPS type SD. The field-lowering coefficient of the MS and MPS type diodes were calculated to be 1.32 × 10–5(m.V)0.5/eV, 2.32 × 10–5 (m.V)0.5/eV, respectively. These values are indicated that SE governs the dominant CCM for MS diode because the experimental value of the field-lowering coefficient is quite closer to the theoretical value. βSC theoretical value. On the other hand, CCM for the MPS diode is governed by PF since the experimental value is extremely near to the theoretical value.

CCM is usually dependent on various parameters such as the fabrication or surface processes, the nature of height, the interfacial layer at the M/S interface, surface states localized in the forbidden band-gap of semiconductor, sample temperature, applied voltage, and the doping concentration of donor or acceptor atoms [24, 26]. But a number of them such as TE, TFE, FE, GR, tunneling via surface states or dislocations, and Gaussian distribution (GD) of BHs compete unusually, one of them may dominate over the others in a certain temperature, and applied bias voltage region [37, 38]. Among them, the tunneling mechanism (FE and TFE) is important at low temperature and high doping concentration levels, and hence these two mechanisms are ruled out in this study. Therefore, obtained high value of n and the deviation linearity of lnI vs V plot at enough high forward bias voltage can be attributed to the existence of barrier inhomogeneity, Nss, native or deposited interfacial layer, and Rs, and among them, Nss and barrier inhomogeneity are effective at moderate forward bias voltage, but interfacial layer and Rs are effective at higher forward bias voltage, respectively.

3.2 Dielectric properties

In recent years, the investigation of real and imaginary parts of complex-dielectric (ε* = ε′–jε″), complex-dielectric modulus (M* = M′ + jM″), and AC conductivity in a wide frequency range for technological applications have had tremendous interest in. On the other hand, to get an ultra-capacitive with more charges/energy storage capacity, it is necessary to perform flexible, higher values of ε′, lower values of dielectric loss (ε″), lover values of tangent-loss (tanδ = ε″/ε′), thin, cheap, environmentally friendly, and light-weight an inter-layer between semiconductor and metal. As a result, the impedance spectroscopy (IS) technique is a critical and reliable approach for revealing the electrical and dielectric properties of metal–semiconductor (MS) devices with an interfacial layer such as oxide/insulator, polymer, or ferroelectric materials at the M/S interface [36, 39,40,41,42]. The values of ε′, ε″, tanδ, M′, M″, and ac electrical-conductivity (σac) can be used to derive the measured real and imaginary components of admittance (Y* = 1/Z* = G + jωC) as given following relations, respectively [36, 39, 40]:

Here, the Co(= εoA/di), A, j, ω(= 2πf), and di quantities are the geometrical/empty capacitance, rectifier contact area, angular frequency, j is the square root of −1, and inter-layer is the thickness. As illustrated in Fig. 7a, b, the value of C and G at 1.5 V decreases with increasing frequency for MS and MPS type structures. The capacity of the charge carriers to follow the ac signal causes this phenomenon. It is associated with the Nss and their lifetime (τ) between native/deposited interfacial layer and Schottky metal contacts. Because Nss and polarization (surface/dipole) can easily follow the ac signal at lower frequencies and provide an excess C and G compared to their real values [41], the charges at states/traps cannot follow the ac signal at higher levels of frequencies. So they cannot contribute to the measured real value of them. Similar to C vs. ln(f) and G/ω vs. ln(f), as indicated in Fig. 8a and b, the Nss and interfacial layer are the cause of altering the frequency dispersion property in the value of ε′ and ε″ especially at lower frequencies.

Therefore, the observed decrease in these values with increasing frequencies in the fabricated MS and MPS type structures can be explained by the existence of Nss and easy polarization of the interlayer layer under an electric field. These results indicate that the (Al2O3-PVP) interlayer can be successfully used in place of the conventional native or deposited SiO2 insulator layer by growing traditional techniques such as thermal oxidation and sputtering methods, and such high dielectric it has some advantages in respect of low cost, low energy consumption all through growing processes, low weight per molecule, high-dynamic stress, high-charge storages capability, and flexibility [43].

Figure 9 shows the tangent-loss vs. log(f) curves of the MS and MPS type structures obtained in Eq. 8c. The value of tan\(\delta\) declines with increasing frequency, and it approaches the optimal outcome at sufficiently high frequencies because both Nss and polarization effects can be ignored at high frequencies [40,41,42, 46]. As shown in Fig. 9, the value of tanδ increases with increasing frequency until at about 600 Hz and then decreases with an increasing frequency almost exponentially for MPS type structure depends on frequency-dependent values of \(\varepsilon^{\prime}\) and \( \varepsilon^{\prime\prime}\). In general, at low frequencies, Maxwell–Wagner type interfacial polarization and hoping mechanisms of charges can occur between traps or conduction bands under an external electric field can be used to explain the peak in the loss tangent. Because, at low frequencies, surface states can easily follow the ac signal and dipoles have enough time to rotate around themselves [44].

In Fig. 10a, the computed resistivity (Ri) for two types of structures using the Nicollian and Brews method [47] declines with increasing frequency, and it approaches the actual value Rs at a sufficiently high frequency. The increasing value of σac with frequency rise is attributed to the space charge polarization. It is also almost frequency independent at low frequencies. As the frequency decreases, charge accumulation occurs at the polymer-semiconductor interface. Due to the utilized polymer interlayer, the MS has a lower ac electrical conductivity than MPS. The low value of Rs in the MPS relative to the MS diode is what causes this behavior. Therefore, the conductivity value is low at low frequencies. This result is also compatible with the literature, where it is suggested in [48].

In addition, as shown in Fig. 10b, electrical conductivity often rises with increasing frequency due to a decrement in Rs with rising frequency [42, 46].

Double-logarithmic σac–f plots of the tan(δ) Al/p-Si and Al/(Al2O3:PVP)/p-Si structures are given in Fig. 10b, and the log(σ)log(f) plot for forwarding bias demonstrates plateau for low and high-frequency regions related to σdc and σac, respectively. The dual logarithmic σac–f plot is acceptable with a power-law frequency dependency which is shown in Fig. 10b [39, 40]:

In Eq. (9), σdc represents dc electrical conductivity with a total electrical conductivity that is nearly constant at low and intermediate frequencies, A represents a constant, and s represents the slope of the ln(σac)–ln(f) plots for a given bias voltage. When s is less than 1, it is assumed that the jumping motion consists of a translational motion followed by an abrupt jumping. In the event of a value greater than 1, however, the mobility includes confined jumping without the species leaving its neighbors [41, 42, 46, 47].

The change of M’ and M" with frequency at 1.5 V at room temperature is shown in Fig. 11a and b. Due to the short-range mobility of carriers, the value of M’ clearly increases as frequency increases. M"- log (f) plots for the dielectric relaxation process should give a peak for MPS structure corresponding to the ωτ = 1 point due to the transition between short and long-range charge carrier mobility. Moreover, it is shown that the relaxation frequencies shift towards higher frequencies. In recent years, the literature has reported similar results [49, 51].

4 Conclusion

In this study, either the MS or MPS type structures were grown onto the same pSi wafer in identical conditions to see the effects of the high-dielectric (Al2O3-PVP) organic inter-layer on the electrical and dielectric characteristics at room temperature. Some critical basic electrical parameters were first extracted from the forward and reverse bias I–V data using TE, Norde, and Cheung functions. They were discovered to be a function of voltage and the computed method utilized. While the MPS type structure has smaller Io, leakage current, and n than the MS structure, the MPS structure has higher Io, leakage current, and n, and the Rsh, RR, and BH values have higher. These results show that using a high-dielectric (Al2O3:PVP) interlayer between semiconductor and Schottky contacts leads to increased MPS structure performance compared to MS structure. Considering BH’s dependence, the energy-dependent profile of Nss was derived from the forward bias I–V data. The magnitude of Nss for the MPS structure is also lower than the MS structure because of the passivation effect of the (Al2O3:PVP) interfacial layer. To investigate the effects of polarization, Dit, and the (Al2O3-PVP) inter-layer on these parameters, the values of ε’, ε", tanδ, σac, M’, and M’’ were acquired from C–f and G/ω–f data over a significant frequency of range of 100 Hz–1 MHz.These parameters were found to have a vital function of frequency. Using this, sapphire interfacial layer increases the performance of the MS-type SBDs concerning drops in n and leakage current and a rise in rectifying rate (RR), BH, ε′. As a result, the used (Al2O3-PVP) interlayer can be successfully fabricated in place of the traditional insulator layer by growing traditional techniques such as thermal oxidation and sputtering techniques, and it has many advantages such as low cost, low energy consumption during growing processes, low weight per molecule, high-dynamic stress, high-charge storages capability, and flexibility.

Data availability

The datasets analyzed during the current study are available from the corresponding author on reasonable request.

References

H.G. Çetinkaya, S. Demirezen, S.A. Yerişkin, Electrical parameters of Au/(%1Ni-PVA)/n-Si (MPS) structure: surface states and their lifetimes. Physica B Condens. 621, 413207 (2021)

E.E. Tanrıkulu, S.A. Yerişkin, On the changes in the dielectric, electric modulus, and ac electrical-conductivity in the Al/(C29H32O17)/p-Si (MPS) structures in a wide range of frequency and voltage. Physica B Condens. 623, 413345 (2021)

Ş Altındal, A. Barkhordari, S. Özçelik, G. Pirgholi-Givi, H. Reza Mashayekhi, Y. Azizian-Kalandaragh, A comparison of electrical characteristics of Au/n-Si (MS) structures with PVC and (PVC: Sm2O3) polymer interlayer. Phys Scr. 96, 125838 (2021)

M.S.P. Reddy, K. Sreenu, V.R. Reddy, C. Park, Modified electrical properties and the transport mechanism of Ti/p-InP Schottky structure with a polyvinyl-pyrrolidone (PVP) polymer interlayer. J Mater Sci. 28, 4847–4855 (2017)

S.A. Yerişkin, The investigation of effects of (Fe2O4-PVP) organic interlayer, surface states, and series resistance on the electrical characteristics and sources of them. J Mater Sci. 30, 17032–17039 (2019)

V.R. Reddy, Electrical properties of Au/polyvinylidene fluoride/n-InP Schottky diode with polymer interlayer. Thin Solid Films 556, 300–306 (2014)

M. Sharma, S.K. Tripathi, analysis of interface states and series resistance for Al/PVA:n-CdS nanocomposite metal-semiconductor and metal-insulator-semiconductor diode structures. Appl Phys A. 113, 491–499 (2013)

S.A. Yerişkin, Y.Ş Asar, Influence of graphene doping rate in PVA organic thin film on the performance of Al/p-Si structure. Mater Sci 32, 22860–22867 (2021)

A. Eroğlu, S. Demirezen, Y. Azizian-Kalandaragh, Ş Altındal, A comparative study on the electrical properties and conduction mechanisms of Au/n-Si Schottky diodes with/without an organic interlayer. J. Mater Sci. 31, 14466–14477 (2020)

V. Bühler, Polyvinylpyrrolidone excipients for pharmaceuticals: povidone, crospovidone, and copovidone (Springer Science & Business Media, 2005)

A. Tataroğlu, Ş Altındal, Y. Azizian-Kalandaragh, Electrical characterization of Au/n-Si (MS) diode with and without graphene-polyvinylpyrrolidone (Gr-PV) interface layer. J. Mater Sci.: Mater. Electron. 32, 3451–3459 (2021)

S. Demirezen, S.A. Yerişkin, Frequency and voltage-dependent dielectric spectroscopy characterization of Al/(Coumarin-PVA)/p-Si structures. J. Mater Sci.: Mater. Electron. 32, 25339–25349 (2021)

A. Tataroglu, A.B. Ulusan, Ş Altındal, Y. Azizian-Kalandaragh, A Compare Study on Electrical Properties of MS Diodes with and Without CoFe2O4-PVP Interlayer. Inorg Organomet Polym Mater J 31, 1668–1675 (2021)

G. Pirgholi-Givi, Ş Altındal, M.A. Shahedi, A.S. Namini, J. Farazin, Y. Azizian-Kalandaragh, The effect of cadmium impurities in the (PVP-TeO2) interlayer in Al/p-Si (MS) Schottky barrier diodes (SBDs): exploring its electrophysical parameters. Physica B Condens. 604, 412617 (2021)

Ö. Güllü, A. Türüt, Electrical analysis of organic interlayer-based metal-interlayer- semiconductor diode structures. J. Appl. Phys. 106, 103717–103722 (2009)

B. Akin, R.M. Linford, A. Ahmadivand, Ş Altindal, All-dielectric fabry-pérot cavity design for spectrally selective mid-infrared absorption. Phys Status Solidi Basic Res. 259, 2100464 (2022)

P.A. Prashanth, R.S. Raveendra, R.H. Krishna, S. Ananda, N.P. Bhagya, B.M. Nagabhushana, K. Lingaraju, H.R. Naika, Synthesis, characterizations, antibacterial and photoluminescence studies of solution combustion-derived α-Al2O3 nanoparticles. J. Asian Ceram. Soc. 3, 345–351 (2015)

A.K. Harman, S. Ninomiya, S. Adachi, Optical constants of sapphire (alpha-Al2O3) single crystals. J App Phys. 76, 8032–8036 (1994)

R.E. Dobrovinskaya, L.A. Leonid, V. Pishchik, Properties of sapphire: micro- and optoelectronic materials, in Structures and systems. ed. by V. Pishchik, L.A. Lytvynov, E.R. Dobrovinskaya (Springer, Boston, 2009), pp.55–176

B. Akin, G. Pirgholi-Givi, J. Farazin, Y. Azizian-Kalandaragh, S¸. Altindal, Utilization of Al2O3/PVP nanocomposite as an interfacial layer for Schottky structures. Thirteenth International Congress on Artificial Materials for Novel Wave Phenomena (Metamaterials), IEEE. X-017-X-019 (2019).

L. Cao, N. Yang, S. Li, X. Ye, X. Yuan, H. Li, H. Tong, Alumina film deposited by spin-coating method for silicon wafer surface passivation. J. Mater. Sci. Mater. Electron. 31, 2686–2690 (2020)

S.M. Sze, Physics of semiconductor devices, 2nd edn. (Wiley, New York, 1981)

H.C. Card, E.H. Rhoderick, Studies of tunnel MOS diodes I: interface effects in silicon Schottky diodes. J. Phys. D Appl. Phys. 4, 1589–1601 (1971)

S. Cheung, N. Cheung, Extraction of Schottky diode parameters from forward current-voltage characteristics. Appl. Phys. Lett. 49, 85–87 (1986)

D.E. Yıldız, Electrical properties of Au–Cu/ZnO/p-Si diode fabricated by atomic layer deposition. J Mater Sci. 29, 17802–17808 (2018)

M. Sharma, S. Tripathi, Analysis of interface states and series resistance for Al/PVA: n-CdS nanocomposite metal-semiconductor and metal-insulator-semiconductor diode structures. Appl. Phys. A 113, 491–499 (2013)

A.S. Namini, M. Asl, G. Pirgholi-Givi, S.A. Delbari, J. Farazin, Ş Altındal, Y. Azizian-Kalandaragh, On the electrical characteristics of Al/p-Si diodes with and without (PVP: Sn-TeO2) interlayer using current-voltage (I–V) measurements. Appl. Phys. A 26, 935 (2020)

Ş Altındal, A. Barkhordari, G. Pirgholi-Givi, M. Ulusoy, H. Mashayekhi, S. Özçelik, Y. Azizian-Kalandaragh, Comparison of the electrical and impedance properties of Au/(ZnO Mn: PVP)/n-Si (MPS) type Schottky-diodes (SDs) before and after gamma-irradiation. Phys. Scr. 96, 125881 (2022)

I. Taşçıoğlu, W.A. Farooq, R. Turan, Ş Altındal, F. Yakuphanoğlu, Current transport mechanisms and density of interface traps in MgZnO/p-Si diodes. J. Alloys Compd 590, 157–161 (2014)

R.T. Tung, Recent advances in Schottky barrier concepts. Mater. Sci. Eng. R. 35, 1 (2001)

S.A. Yerişkin, M. Balbaşı, İ Orak, The effects of (graphene doped-PVA) interlayer on the determinative electrical parameters of the Au/n-Si (MS) structures at room temperature. J Mater Sci Mater Electron. 28, 14040–14048 (2017)

H. Norde, A modified forward I–V plot for Schottky diodes with high series resistance. J. Appl. Phys. 50, 5052–5053 (1979)

K.E. Bohlin, Generalized Norde plot including determination of the ideality factor. J. Appl. Phys. 60, 1223 (1986)

H. Schroeder, Poole-Frenkel-effect as dominating current mechanism in thin oxide Films-An illusion. J. Appl. Phys. 117, 215103 (2015)

V.R. Reddy, V. Manjunath, V. Janardhanam, Y.H. Kil, C.-J. Choi, Electrical properties and current transport mechanisms of the Au/n-GaN Schottky structure with solution-processed high-k BaTiO3 Interlayer. J. Electron. Mater. 43, 3499–3507 (2014)

Z. Wanga, W. Zhou, L. Dong, X. Sui, H. Cai, J. Zu, Q. Chen, Dielectric spectroscopy characterization of relaxation process in Ni/epoxy composites. J. Alloys Compd. 682, 738–745 (2016)

D.E. Yildiz, A. Kocyigit, M.O. Erdal, M. Yıldırım, Dielectric characterization of Al/PCBM:ZnO/p-Si structures for wide-range frequency. Bull Mater Sci 44, 25 (2021)

H.H. Gullu, D.E. Yildiz, L. Toppare, A. Cirpan, Electrical characteristics of organic heterojunction with an alternating benzotriazole and fluorene containing copolymer. J Mater Sci: Mater Electron. 31, 18816–18831 (2020)

S. More, R. Dhokne, S. Moharil, Dielectric relaxation and electric modulus of polyvinyl alcohol–Zinc oxide composite films. Mater. Res. Express. 4, 055302 (2017)

Ş Altındal, M. Ulusoy, S. Özçelik, Y. Azizian-Kalandaragh, On the frequency-dependent complex-dielectric, complex-electric modulus and conductivity in Au/(NiS: PVP)/n-Si structures. J Mater Sci Mater Electron. 32, 20071–20081 (2021)

J. Werner, A.F.J. Levi, R.T. Tung, M. Anzlowar, M. Pinto, Origin of the excess capacitance at intimate Schottky contacts. Phys. Rev. Lett. 60, 53–56 (1988)

M.H. Abdellatif, A.A. Azab, A.M. Moustafa, Dielectric spectroscopy of localized electrical charges in ferrite thin film. J. Electron. Mater. 47, 378–384 (2017)

D.E. Yıldız, H.H. Gullu, H.K. Cavus, Effect of TiO2 thin film with different dopants in bringing Au-metal into a contact with n-Si. J Inorg Organomet Polym. 32, 1067–1077 (2022)

M. Singh, A. Dogra, R. Kumar, Nucl. Inst. Meth. B. 196, 315 (2002)

H.H. Gullu, D.E. Yildiz, Capacitance, conductance, and dielectric characteristics of Al/TiO2/Si diode. J Mater Sci Mater Electron 32, 13549–13567 (2021)

H.G. Çetinkaya, M. Yıldırım, P. Durmuş, Ş Altındal, Diode-to-diode variation in dielectric parameters of identically prepared metal-ferroelectric-semiconductor structures. J. Alloys Compd. 728, 896–901 (2017)

J.R.B.E.H. Nicollian, E.H. Nicollian, MOS (metal oxide semiconductor) physics and technology (Wiley, New York, 1982)

A. Buyukbas, A. Tataroğlu, Effects of temperature on dielectric parameters of metal-oxide-semiconductor capacitor with thermal oxide layer. J. Nanoelectron. Optoelectron. 10(5), 675–679 (2015)

Ş Altındal, A. Barkhordari, Y. Azizian-Kalandaragh, B.S. Çevrimli, Dielectric properties and negative-capacitance/dielectric in Au/n-Si structures with PVC and (PVC: Sm2O3) interlayer. Mater Sci Semicond Proc. 147, 106754 (2022)

S.O. Tan, O. Çiçek, Ç.G. Türk, Ş Altındal, Dielectric properties, electric modulus, and conductivity profiles of Al/Al2O3/p-Si type MOS capacitor in large frequency and bias interval. Int. J. Eng. Sci. Technol. 27, 101017 (2022)

Ş Altındal, B. Akın, On the frequency and voltage-dependent main electrical parameters of the Au/ZnO/n-GaAs structures at room temperature by using various methods. Phys. B: Condens. Matter. 594, 412274 (2020)

Funding

The author declares that no funds, grants, or other support was received during the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

All authors contributed to the study conception and design. Material preparation, data collection and analysis were performed by the corresponding author Dr. Buket Akin. The first revised draft of the manuscript was written by Dr. Buket Akin and all authors commented on previous versions of the manuscript. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Informed consent

The research is not involving Human Participants and/or Animals and informed consent.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Akin, B., Farazin, J., Altındal, Ş. et al. A comparison electric-dielectric features of Al/p-Si (MS) and Al/ (Al2O3:PVP)/p-Si (MPS) structures using voltage–current (V–I) and frequency–impedance (f–Z) measurements. J Mater Sci: Mater Electron 33, 21963–21975 (2022). https://doi.org/10.1007/s10854-022-08984-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-022-08984-2