Abstract

In this study, I investigated the effect of work function (ϕm) of AuxAg1−x (x = 0, 0.22, 0.37, 0.71 and 1) on the Au–Ag/n-GaAs Schottky diode (SD) parameters. Ag, Au metals and three alloys with different compositions deposited on n-GaAs substrates by the thermal evaporation method. Surface morphologies of the samples were investigated by an atomic force microscope (AFM). Elemental compositions of Schottky contact metals were conducted by energy dispersive X-ray spectroscopy (EDX). Current–voltage (I–V) and capacitance–voltage (C–V) measurements were performed at room temperature. SD parameters such as barrier height (Φb0), ideality factor (n), series resistance (Rs), and interface state density (Dit) of the SD’s were calculated from the obtained I–V and C–V data. Experimental results showed that all calculated SD parameters depend on the alloy composition. The lowest mean barrier height value was found as 0.789 ± 0.022 eV for Au/n-GaAs SDs and the highest value was determined 0.847 ± 0.008 eV for Au0.71Ag0.29/n-GaAs SDs from I–V measurements. Weak dependencies of barrier height to ϕm existed and gap state parameter (S) determined as 0.0526. The S value was close to the Bardeen limit (S = 0) and indicates that the Fermi level was strongly pinned in Au–Ag/n-GaAs SDs. Also, main SD parameters like series resistance (Rs), ideality factor (n), reverse bias barrier height (ΦbRB), doping density (Nd) and density of interface states (Dit) were calculated via using different methods from I–V and C–V measurement results. Also, to determine the leakage current mechanism Poole–Frenkel emission (PFE) and Schottky emission (SE) models applied on reverse bias I–V data.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Barrier formation mechanisms of metal–semiconductor contacts have been a major research topic since the first discovery of these contacts [1,2,3,4]. To accurately identify the current flowing through the contact and determine the operating conditions of the devices, the basic parameter, barrier height (Φb), must be defined correctly. The first attempt was realized by Schottky to understand the rectifying behavior of metal–semiconductor contacts [5]. Schottky and Mott subsequently proposed a model for barrier formation and calculating the barrier height [5,6,7]. According to the Schottky–Mott rule [7], under the ideal condition, the factors affecting this barrier height was an electron affinity of the semiconductor (χs) and the work function of metal (ϕm), and it was simply expressed as follows;

Since the Schottky–Mott rule is rarely verified experimentally, it can be concluded that; interface dipoles do not disappear and play a major role in determining the properties of the metal–semiconductor interface [8]. The ϕm value of the metal depends on two components; volume term and surface dipole term, which starts just below the surface of the metal and represents where all bulk properties are the same. Both dipole terms strongly correlate with surface charge distribution and depend on the condition of the surface [9]. Moreover, it was commonly known that, when metal and semiconductor are brought into contact without any interface layer, the atomic sites and charge distributions change, so that the contribution of the surface dipole changes. Louie et al. overcome this situation using the metal's electronegativity instead of the function of the metal [10]. Besides, known that the presence of states at the interface has a significant effect on the formation of barrier height and investigated in many studies [2, 7, 8, 11,12,13,14,15,16].

Although the Schottky–Mott rule provides accurate estimation of band bending in a semiconductor, the validity of the proposed model, due to the presence of states at the interface between the metal and the semiconductor and the "Fermi level pinning" caused by these finite states, is a matter of discussion especially for some semiconductors [2, 17]. According to this model, if the thin insulating layer exists between a semiconductors and a metal, interface states of semiconductor are occupied by the electrons, create an additional space charge region, and create the potential difference. This potential difference reduces the effect of metals work function on barrier height [17]. Experimentally observed barrier height has a very limited relation to the results of this theory [8, 14, 18]. Few models were proposed to reveal the formation of barrier height in a metal semiconductor contact [2, 11, 19]. Some of these models associate the independence of the barrier height from the ϕm with the fermi level pining mechanism caused by high density interface states [2]. Some other models are closely interested in interfacial chemistry and address the interaction of interfacial dipole with bond polarization [11]. However, all proposed models haven’t yet emerged to explain the properties of metal–semiconductor contacts precisely, are not complete and usually change with the substrate, metal, substrate cleaning method, metal deposition method, etc. [9]. It is possible to determine the diode parameters (tuning) during the production of diodes to serve a specific purpose. It is sufficient to use metals or semiconductors with different work functions [9, 13, 20, 21].

GaAs has high thermal strength, high electron mobility and high resistance to radiation damage. It also has a direct band gap that allows efficient absorption of light emission and absorption, allowing transistors to operate at very high frequencies, reducing the noise at which higher frequencies tend to reduce electrical signal distortion in electronic circuits. Also, ternary and quaternary alloys created from GaAs utilizing elements like Al, In, P, and SB have properties that complement those of GaAs, which allows adaptability. GaAs is an important substrate material for devices, which is used in both micro- and optoelectronic applications. Also, GaAs is a suitable substrate for a basic component for high-speed and low-power electronics. On the condition that the properties of the semiconductor remain the same (assuming the effect of interface states to be invariant), modifications in the composition of metal should be expected to change the barrier height. Studies using metals with different business functions have shown that, electrical parameters are closely related to these metals [9, 22]. Especially Au and Ag metals are preferred because of their good conductivity properties and good contacts with semiconductor substrates [23,24,25]. Both Au and Ag have very similar properties such as conductivity, molar heat capacity, crystal structure, atomic and covalent radius. The miscible in all portions and known as good contact properties with GaAs.

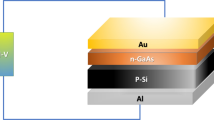

In this study, the effect of modification in the ϕm of Schottky contact metal was investigated depending on the composition of alloys. For this purpose, electrical measurements (current–voltage and capacitance–voltage) were performed at room temperature on produced 20 Schottky barrier diodes (SDs) which it was fabricated by using two metals (Ag, Au) and three different alloys on n-GaAs. The characteristic diode parameters of SDs have been determined and compared with each other. The pinning position of the Fermi level and density of interface states (Dit) have been determined and the validity of the Schottky–Mott rule for the Au–Ag/GaAs was tested.

2 Experimental procedures

The n-type GaAs substrate used in this study was grown by the LEC method and Te-doped with a carrier concentration of 2–5 × 1017 cm3. To remove organic contaminations on GaAs substrate was cleaned with some solvents (acetone, methanol, trichloroethylene, deionized water) 5 min using ultrasonic agitation in each step. Then, GaAs substrate was immersed in an HCl:H2O (1:1) etching solution to eliminate the thin native oxide layer on the surface, rinsed with de-ionized water (18 MΩ) and high purity nitrogen gas used for drying. After the etching process, the GaAs substrate was inserted into the metal deposition chamber immediately.

The Ohmic contacts and transfer length method (TLM) patterns were built by thermal evaporation of Au–Ge alloy (wt% 12), on the non-polished side of the substrate with a thickness of 200 nm, at 2 × 10–6 Torr base chamber pressure and thermally annealed at 350 °C for 2 min. in flowing high purity (5 N) nitrogen gas in a tube furnace. TLM method [26] was used to characterize the electrical contacts, with gaps of 0.25, 0.50, 0.75 mm between 0.7 × 3.5 mm pads. Specific contact resistance (ρc), contact resistance (Rc), and the effective length (Leff) derived from the measured I–V data and the calculated total resistance versus gap spacing by TLM and values was 9.899 × 10–6 Ωcm2, 0.510 Ωcm and 0.770 μm, respectively.

The substrate was divided into five parts and the area of each part was approximately 1 cm2. Each part was immediately inserted into the vacuum chamber of NVTS-400 to form Schottky contacts by thermal evaporation of metals and alloys. The AuxAg1−x alloys made at tungsten crucibles, using high purity Au (4N5) and Ag (5 N) parts, repeating the melt-cooling cycle at least five times and under vacuum. Alloy composition (x = 0, 0.22, 0.37, 0.71 and 1) was verified by EDX measurements and given in Table 1. Schottky contact metals/alloys thermally evaporated through a tungsten shadow mask on the front side of the wafers with a diode area was 0.785 mm2. Electrical characteristics of Au–Ag/n-GaAs SDs studied from dc current–voltage (I–V) measurements (measured with the HP4140B picoammeter) and frequency dependent capacitance–voltage (C–V) measurements (measured with Agilent E4980A LCR meter) in the dark and 300 K. The forward and reverse bias I-V measurements evaluated using the standard thermionic emission theory, and Poole–Frenkel and Schottky emission theory. C–V measurement results were also evaluated using diode capacitance, and single frequency approximation for interface state density distribution model. All measurements and calculations were performed with our SeCLaS-PC program [27, 28].

3 Results and discussions

3.1 Work functions and surface morphology of binary Au–Ag alloy

The work function was one of the most basic properties of material surfaces and it directly affects the electrical properties of metal–semiconductor contacts. Although the work functions of metals are well documented for various elements, information about the work functions of alloy surfaces and their dependence on composition is limited [29]. Segregation, especially in alloys, makes it difficult to determine of the work function of the alloys [30]. Generally, Gelatt and Ehrenreich's model was used for determine the work function of the alloy [31,32,33,34] in the experimental studies. According to this method, the work function of an alloy in the form of AxB1−x was,

where \({\rho }_{A}\) and \({\rho }_{B}\) are total densities of states \({\phi }_{m,A}\) and \({\phi }_{m,B}\) are the work functions, and of metal A and B, respectively. The density of states at Fermi level depends on electronic specific heat constant \({C}_{e}=(1/3){\pi }^{2}\rho {k}^{2}T\). Ce values of Au and Ag are 0.948 and 0.645 mJmol−1 K−2, respectively [31]. Contrary to the model proposed by Fain et al. [31], since these electronic specific heat constant values were not close to each other, so work functions could not show a linear variation. When the work functions were considered as 5.22 eV and 4.30 eV for Au and Ag [34], respectively, obtained work functions of alloys were given in Table 1 with the corresponding atomic composition.

The grain size of Schottky contact metals and the condition of the surface of this metal/alloy play an important role in determining the electrical properties [32, 33]. Atomic force microscopy was used to examine the surface morphology of the Au–Ag Schottky contacts on n-GaAs. Figure 1 shows the AFM images of the Au/n-GaAs and Ag/n-GaAs SDs. As shown in Figure, the surface morphology of the SDs was fairly smooth. Root mean square (RMS) roughness of films was found from 20 × 20 μm image area and values were 45.9 nm for Au, 37.8 nm for Au0.71Ag0.29, 46.2 nm for Au0.37Ag0.63, 29.5 nm for Au0.22Ag0.78 and 26.1 nm for Ag. A correlation was not observed between the RMS values of the alloys and metals. However, relatively high RMS values are the result of the island-type metallization process observed during the metallization process [34,35,36]. The phenomenon of island formation of metals is typically observed between low and high surface energy materials. To minimize the total surface energy of the system, the metals/alloys agglomerates to minimize its surface area and exposes more surface area of the low surface energy materials (surface energies were determined as 0.86 J m−2, 1.51 J m−2 and 1.97 J m−2 for GaAs, Ag and Au, respectively) [37].

3.2 Forward bias I–V characteristics of the Au–Ag/n-GaAs SDs

The semi-logarithmic forward and reverse I–V characteristics of one Au–Ag/n-GaAs SDs are shown in Fig. 2. As can be seen in Fig. 2, the rectifying properties of the SD depend on the alloy composition and therefore they depend on the work function. These experimental plots analyzed by using thermionic emission theory, assuming the barrier was homogeneous. According to the theory, the flowing current through the diode in the forward bias region (for V ≥ 3kT/q) is as follows [7, 38];

and

where I0, V, n, k, T, A*, A, q, and ΦbIV are the saturation current at zero bias, the applied bias voltage, the ideality factor, the Boltzmann constant, the temperature in Kelvin, the effective Richardson constant (8.16 Acm−2 K−2 for n-GaAs), the effective diode area, the electron charge, and the barrier height, respectively.

In Eq. (4), n is a dimensionless parameter and it is an indicator for the deviation from the theory (ideally equals unity). The experimental values of the n and the Φb were determined from slopes and intercepts of the linear regions of the forward bias lnI-V plots by using Eqs. (3 and 4). Other calculations and all least square fittings were performed via our computer program SeCLaS-PC. The values of the Φb and n of the Au–Ag/n-GaAs SD varied with alloy compositions (Table 1). As can be seen in Table 1, the ideality factors of Au–Ag/n-GaAs SDs were higher than the 1. This high value of the ideality factors was generally attributed to the existence of a thin oxide layer between metal and semiconductor, surface preparation techniques, Fermi level pinning, and homogeneity of the surface of the semiconductor [33, 39].

Ideally, when the metal and semiconductor are combined to form a contact, the boundary between the metal and the semiconductor is assumed sharp, but in a real situation is different. As stated in previous studies, even if the metallization process was carried out at room temperature, solid-state reactions occur between the metal and the semiconductor [34, 36, 39, 40]. This was more clearly seen in Au/GaAs SDs. Gallide phases formed at the interface were known and have a significant effect on both the n and the ΦbIV [40]. In this study, similar results were obtained for n and the ΦbIV and these values vary depending on the contact metal/alloy. The ideality factor of SDs decreases when the ratio of silver increased in the alloys. The possible reason for this change may be silver prevents the formation of the gallide phases.

It was a well-known method to incorporate very thin barrier metal films to allow metals of such diffusive nature to make better contact with semiconductors or to achieve diffusion in a controlled manner.

The obtained mean value of barrier height and ideality factor for twenty Au/n-GaAs SDs was 0.789 ± 0.022 eV and 1.171 ± 0.022, respectively. These values are considerably lower than the expected barrier height value. However, many studies have obtained different values for the barrier height of these SDs [21, 42,43,44,45,46,47]. For example; Tunhuma et al. found these values 0.85 eV and 1.10 for Au/n-GaAs SDs at room temperature [44]. Özdemir et al. found these values 0.742 eV and 1.247 and, Korucu et al. found that 0.79 eV and 1.034 for Au/n-GaAs SDs around the room temperature [45, 46].

The electrical parameters of the diodes depend on the method of cleaning of the substrates [48], the metallization method [49], the etching method [33, 50], etc. Tsukamato et al. worked on photocatalytic properties of alloy (Au–Ag)/TiO2 junctions [20]. They founded that the work function of the Au–Ag alloy lies at the level intermediate between the monometallic Au and Ag and calculated theoretical energy-band diagram of alloy/TiO2 junction. According to their results, barrier heights change from 0.2 to 1.3 eV for Ag/TiO2 and Au/TiO2, respectively. The alloy/TiO2 junction, therefore, creates a barrier that is larger than Ag/TiO2 but smaller than Au/TiO2. This theoretical calculation does not take into account many parameters that have significant effects on the height of the barrier, such as the presence of interface states, inhomogeneity, interface compounds, doping density, etc. and defines the parameters in an ideal state. However, it is expected/founded to be compatible with the parameters obtained from the experiments. Therefore, it would be more appropriate to evaluate our diodes, which are prepared in identical form and built on the same substrate with the approach that they are consistent among themselves.

When this information was taken into consideration, the change in barrier heights depending on the ϕm was given in Fig. 3. Here, the data related to Au/n-GaAs SD not taken into consideration when evaluating the relationship between metal's ϕm and Φb values (please see inset in Fig. 3). The expected barrier height values could not be observed due to alloying behavior. This behavior causes the AuGa compounds to change the interface chemistry of the Au-GaAs interface as a result of some Ga out-diffusion and solid-state reactions with Au, and the remaining As atoms make the semiconductor highly doped [40, 51, 52]. The exact alloying mechanism that causes the degradation of the SDs was not very clear. This will result in significant field emissions along the barrier and increase the flow through it [51].

This behavior is also observed in studies on AlGaN or GaN substrates [34]. In this study, although there is no annealing process, Ga migration due to solid-state reactions also observed on the contact surface by EDX measurements.

On the other hand, the presence of a small amount of Ag prevents this diffusion and prevents the gallide phases to occur at the interface [35, 36]. There are many examples in the literature (especially in SD on ternary and quaternary semiconductor substrates) where a thin layer of metal barrier is used to prevent these diffusion/out-diffusion processes [53].

According to the Cowley-Sze’s model, barrier height is affected by the density of states at the interface between the metal and the semiconductor and causes a deviation from the Schottky–Mott rule [2]. As mentioned earlier, the slope of linear fit in Φb versus ϕm graph was an indicator of Fermi level pinning and called as “interface behavior parameter” or “gap states parameter” (S) of the semiconductor [2, 8]. Here, if S = 0 state is called a "Bardeen limit" if the S = 1 state is called the "Schottky limit" [54]. S parameter was determined as 0.0526 and close to the Bardeen limit, in our study. Therefore, surface states or interface states stabilize the Fermi level of the metal–semiconductor system and, depending on the characteristic parameters of the metal, thus Fermi level remains unchanged. In this case, the relationship between the density of the interface states and the S parameter known as a Cowley − Sze equation and given as follow [2],

where \({\varepsilon }_{i}\) and \(\delta\) are permittivity of the interfacial layer and thickness of the interfacial layer, respectively [2, 39, 54, 55]. Assuming the \({\varepsilon }_{i}\)=5 \({\varepsilon }_{0}\) and \(\delta\)= 5 Ǻ, we calculate Dit = 1.801 × 1011 eV−1 cm−2 from S according to the Eq. (5), which has a good agreement with the later results and literature [56].

The downward curvature in I–V curves at relatively high forward bias voltage region arises from the series resistance (Rs), of the semiconductor bulk between the depletion region and Ohmic contact. The Rs values of Au–Ag/n-GaAs SD were calculated using two different methods developed by Cheung’s [57] and Norde [58] obtained from the forward bias current equations (Eqs. 3–4).

It is well known that the forward bias I–V plots are linear in the semi-logarithmic scale but these plots deviates from ideality. This deviation arises from the RS, the interfacial layer and the interface states. Especially, at sufficiently high voltages, downward curvature region in the forward bias I–V plots arises from the series resistance of the neutral region of the semiconductor bulk between the depletion region, interfacial layer and Ohmic contact [59]. According to the Cheung and Cheung theory, the barrier height, as well as other diode parameters such as n and Rs was also could be determined using Cheung’s functions;

and

the y-axis intercept and slope of a plot of dV/d(lnI) versus I gives nkT/q. Also, a plot of H(I) versus I give a straight line with the y-axis intercept equal to nΦbCh (not plotted here) The slope of this plot also provides a second determination of Rs, which can be used to check the consistency of Cheung’s approach. The obtained RS, n and ΦbCh of the SDs were given in Table 2. These serial resistance values were consistent with the literature [49, 60, 61].

Another model for determining RS and barrier height values was proposed by Norde. This model modified by Bohle and it is based on determining the minimum point of the Norde function in case of n = 1 [58, 62]. Unlike the Cheung method, in this method the Norde function was applied to all forward bias region of I–V characteristics. According to the Norde’s method, Norde function (F(V)) were expressed as in Eq. (8) and where I(V) and γ was a bias dependent current value obtained from the I–V plots and dimensionless integer larger than ideality factor (γ > n), respectively,

and

and also barrier height (ΦbN) given by the

where F(Vmin) was a minimum point value of F(V), Vmin and Imin corresponding voltage and current values. The plots of F(V) versus V for the Au–Ag/n-GaAs SDs using [58, 62]. Mean values of ΦbN and Rs of twenty Au–Ag/n-GaAs SD were summarized in Table 2.

As can be seen from Table 2, mean Φb and Rs values of SD for each set were found to be consistent with the Cheung’s approach and Norde’s method. The difference between the some parameters (Φb and RS) may be attribute to nature of methods and difficulties in implementation. Such as, while the Cheung functions (Eqs. 6, 7) are applied only to the nonlinear region of the forward bias, the Norde function (Eqs. 8) is applied to the entire forward bias region. Furthermore, the deviation from thermionic emission theory or the failure to determine the exact value of F(Vmin) plots may cause such a inconsistency [63].

Rs values of intimate metal–semiconductor contacts without any desired interfacial layer must only arise from the bulk. The higher values of Rs may arise from the contribution of the native oxide layer on the semiconductor surface to the neutral region series resistance plus imperfect Ohmic contact. However, in the process of making Ohmic contacts and SD it has contributed to contact resistance in the alloys resulting from solid-state reactions [49].

If there are interface states that exist between metal and semiconductor and in equilibrium with semiconductor, the ideality factor of the SD will be greater than unity because of these conditions [17]. The density of these states (\({D}_{it}^{IV}\)) expressed as the following equation;

Here, d and εs are the interfacial layer width and permittivity of the semiconductor, respectively. The depletion layer width was determined from the C–V measurements at a high frequency. Also, n(V) is the ideality factor depending on the bias voltage and given by \(n(V) = (q/kT)[V/{\text{ ln}}\left( {I/I_{0} } \right)]\). In an n-type semiconductor, the energy of the interface states Ess concerning the top of the conduction band (Ec) at the surface of the semiconductor is given by

where \({q\phi }_{e}={\Phi }_{b}^{IV}+\left(1-1/n\right)qV\). The interface state density distribution profile of the s for Au–Ag/n-GaAs SDs was obtained from the experimental I-V plots and was shown in Fig. 4. For all Au–Ag/n-GaAs SDs there was a slight exponential increment seen in \({D}_{it}^{IV}\) from the nearly mid-gap towards the bottom of the conductance band. The existence of metallic-like phases causes a smooth transition between the metal and GaAs substrate and homogenous charge distribution at the interface [44, 52, 64, 65]. When the amount of Ag increased in the alloy, the diffusive nature of Au also deteriorates and Ag prevents the formation of gallide phases. Because, Ag tends to form less gallide phase than Au. Therefore, the Au content in the alloy creates a smaller amount of gallide phase (with GaAs substrate) and density of interface states increases. These increasing \({D}_{it}^{IV}\) values with the Ag content support our proposed approach for interface chemistry by a Ga out-diffusion.

3.3 Reverse bias I–V characteristics of the Au–Ag/n-GaAs SDs

Reverse bias I–V characteristics could also be used to determine some parameters of the fabricated Au–Ag/n-GaAs SDs. Figure 2 reveals that the reverse current (IR) of the Au–Ag/n-GaAs SDs increases with increasing bias, but is not saturated. Different mechanisms cause a leakage current and become effective. The reverse current conduction mechanism of Au–Ag/n-GaAs was investigated based on the Poole–Frenkel emission (PFE) and Schottky emission (SE) models [38, 66]. The reverse bias current as a function of the negative bias can be written as

here

where I0R, βSE and ΦbRB are reverse saturation current, SE field-lowering coefficient and reverse bias barrier height (ΦbRB), respectively. The theoretical values of field lowering coefficients given by

where βSE is the field-lowering coefficient of SE [67]. According to Eq. (15), the theoretical values of the field lowering coefficients (βPF*) for the Au–Ag/n-GaAs SDs were determined as 4.412 × 10−5 eVm1/2 V−1/2. Mean values of ΦbRB and βPF values of twenty Au–Ag/n-GaAs SD were summarized for each set in Table 3. As can be seen from Table 3, values of experimental slope for the Au–Ag/n-GaAs SDs are changes from 1.375 ± 0.068 to 1.560 ± 0.209 eVm1/2 V−1/2, which were closely matched with the theoretical slope of SE. Thus, the dominating charge conduction mechanism for the Au–Ag/n-GaAs SDs is assumed the SE.

3.4 C–V characteristics of the Au–Ag/n-GaAs SD

The bias-dependent C–V characteristics of the Au–Ag/n-GaAs SDs were measured at dark and room temperature. Figure 5 shows a plot of C−2 as a function of bias voltage for the Au–Ag alloy (at.% 0–100) on n-GaAs SDs at sufficiently high frequency (1 MHz or above). The main purpose of these C–V measurements was to reveal the properties of the space charge region of SDs. The relationship between the capacitance of the space charge region and the applied reverse voltage (Vr) in metal–semiconductor contacts given as follows [7, 12],

where Vbi was the built-in potential and Nd was the doping concentration of the GaAs substrate. According to Eq. (16) (1/C2) versus Vr plots give a straight line with the slope were equals to 2/qεsNd and intercepts the x-axis equals to V0 (Fig. 5). Here; V0 is related with the built-in potential Vbi by the equation Vbi = V0 + kT/q and barrier height were given by equation [7],

where Vn is the potential difference between the bottom of the conduction band and the Fermi level in the neutral region of n-GaAs and Vn = (kT/q) ln(Nc/Nd), where Nc is the effective density of states in the conduction band of GaAs and its value was calculated from the Nc = 2(2πm*/kT/h2)3/2, and m* = 0.063m0, and found 4.573 × 1017 cm−3 for GaAs at 300 K. The values of ΦbCV and Nd for the Au–Ag/n-GaAs SDs were given in Table 4. In Table 4, the barrier heights obtained by the C–V method of the SDs were changed between the 1.035 ± 0.022 and 0.912 ± 0.013 eV. These obtained barrier height values are higher than obtained from I–V measurements corresponding to each alloy composition. The difference between the ΦbCV and ΦbIV may be attributed to the lateral inhomogeneity at the interfaces [68]. This lateral inhomogeneity can cause potential fluctuations at the interface. Capacitance is not sensitive to this potential fluctuations but the dc current across the interface depends exponentially on. Any lateral variation in the barrier height causes the current to flow preferentially through the barrier minima. Therefore, the values of barrier height obtained from I–V measurements are lower than those obtained from C–V measurements [33, 34]. Arulkumaran et al. prepared Au/n-GaAs and Ag/n-GaAs SDs and barrier height values varied from 0.82–0.93 eV and from 0.75 to 1.05 eV, respectively [47]. Also, barrier heights found here were reasonable agreement with a value of 0.97 eV from C–V characteristics of Au/n-GaAs and Ag/n-GaAs of nearly the same doping concentration [15].

Although the same parameter was measured, the difference between the ΦbCV’s can be attributed to the existence of lateral inhomogeneity [69]. The source of this lateral inhomogeneity was potential fluctuations at the interface. These fluctuations generally attributed to the thickness of the contact metal, non-uniform distribution at the interface, dislocations, packing errors in the crystal and a thin native oxide layer at the interface, irregularities in the atomic scale on the semiconductor surface, and defects in bulk, and so on [69, 70]. These potential fluctuations affect the dc current and the capacitance measurements in different ways. Diode capacitance was caused by the displacement of the charge carriers in the space charge region due to the ac frequency signal. This displacement was observed near the boundaries of the space charge region. Therefore, the capacitance of the diodes depends on this space charge region and causes the barrier height to be measured only as an average value. The dc current flowing through the diode preferably tends to flow only where the ΦbCV was the lowest.

Besides the I-V measurements, using a single-frequency approximation method [71] on the conductance measurements results, allows the estimation of the Dit. This method was one of the reliable ways to determine the density of interface states. According to this method, DitCV can be found using the following formula,

where Gm ω are measured conductance and angular frequency of ac signal, Cm is measured capacitance. Cox is the capacitance of oxide layer in accumulation region of C–V curves, (Gm)max conforms to maximum G–V curve and Cm is the capacitance of the diodes corresponding to (Gm)max. Also, the series resistance of the equivalent circuit is [71, 72],

This method was applied on C–V and G–V measurement results in the frequency range from 200 Hz to 2 MHz Fig. 6 depicts the changes in DitCV with the frequency, both axes are log scale. DitCV values of Au–Ag/n-GaAs SDs strongly depend on frequencies and decrease at lower and higher frequency range. This “U” type behavior of the interface states has a minimum value that varies from diode to diode.

This minimum value and sufficiently constant DitCV values appear at relatively high frequencies attributed to the excess capacitance. This excess capacitance because of interface states which is in equilibrium with the semiconductor that can easily follow the ac signal [73]. DitCV values of Au–Ag/n-GaAs SDs are same order as those reported by some authors [56].

The frequency dependent series resistance values of Au–Ag/n-GaAs SDs estimated according to Eq. (15) using the measured capacitance and conductance values in the frequency range from 200 Hz to 2 MHz at room temperature and plotted in Fig. 7. This plot indicates that when the frequency decreased, interface states cannot follow the ac signal and each state produces an excess capacitance and conductance and becomes a resistive point for charge carriers and increases exponentially. Inset in Fig. 7 shows that series resistance gives a peak depending on the frequency in the wide negative bias range and the second peak appears after 0 V.

4 Conclusion

In this study, Au–Ag/n-GaAs SDs fabricated by thermal evaporation method and investigated the effect of the work function of metals on SD’s parameters. TLM results indicate that Ohmic contact resistance was very low and EDX results indicates that the alloy’s percentage (x) by weight values were 0.22, 0.37 and 0.71. Also, AFM images showed that smooth contacts were made. AuxAg1−x (x = 0, 0.22, 0.37, 0.71 and 1) alloys were used for fabricating SDs by following the same cleaning procedure with using the n-type GaAs substrate and then, characterized by various methods and techniques. Also, characteristic parameters of SDs have been determined and compared with each other.

The lowest mean barrier height of about 0.789 ± 0.022 eV in Au/n-GaAs SDs and the highest mean barrier height 0.847 ± 0.008 eV in Au0.71Ag0.29/n-GaAs SDs were observed (from I–V measurements). Φb values of Au/n-GaAs SDs were lower than the expected value and, explained by the presence of the gallide phases at the interface. It was observed that the Ag was prevented the Au diffusion into the GaAs substrate or out diffusion of Ga. Furthermore, it was found that an almost linear relationship between Schottky barrier height and metal work function (with \({\Phi }_{b}^{IV}=0.0526{\phi }_{m}+0.577\)). The gap states parameter (S) was found as a 0.0526 and, close to the Bardeen limit (S = 0). In summary, the Fermi level pinning model proposed by Cowley and Sze applies not only to metal-GaAs contacts but also to alloy-GaAs contacts, and indicates that Fermi level was strongly pinned 0.577 eV below the conduction band in our SD’s. In addition, from this dependency, the density of states was determined as 1.801 × 1011 eV−1 cm−2. This interface state density value was in the same order of magnitude with the DitIV values (calculated from I-V measurement result) and DitCV values (calculated from C-V measurement result).

References

J. Bardeen, Surface states and rectification at a metal semi-conductor contact. Phys. Rev. 71, 717 (1947)

A. Cowley, S. Sze, Surface states and barrier height of metal-semiconductor systems. J. Appl. Phys. 36, 3212–3220 (1965)

W. Schottky, On the semiconductor theory of blocking and point contact rectifiers (in German). Z. Angew. Phys. 113, 367–414 (1939)

W. Spitzer, C. Mead, Barrier height studies on metal-semiconductor systems. J. Appl. Phys. 34, 3061–3069 (1963)

W. Schottky, Semiconductor theory of the blocking layer (in German). Naturwissenschaften 26, 843 (1938)

N. Mott, Note on the contact between a metal and an insulator or semiconductor, in: Proceedings of the Cambridge Philosophical Society, (Cambridge Univ Press, 1938), pp. 568–572

E.H. Rhoderick, R.H. Williams, Metal-Semiconductor Contacts (Clarendon Press, Oxford, 1988)

R.T. Tung, The physics and chemistry of the Schottky barrier height. Appl. Phys. Rev. 1, 011304 (2014)

G. Myburg, F.D. Auret, W.E. Meyer, C.W. Louw, M.J. van Staden, Summary of Schottky barrier height data on epitaxially grown n- and p-GaAs. Thin Solid Films 325, 181–186 (1998)

S.G. Louie, J.R. Chelikowsky, M.L. Cohen, Ionicity and the theory of Schottky barriers. Phys. Rev. B 15, 2154–2162 (1977)

R.T. Tung, Formation of an electric dipole at metal-semiconductor interfaces. Phys. Rev. B 64, 205310 (2001)

S.M. Sze, K.K. Ng, Metal-Semiconductor Contacts (John Wiley & Sons Inc, New Jersey, 2006), p. 832

E. Bucher, S. Schulz, M.C. Lux-Steiner, P. Munz, U. Gubler, F. Greuter, Work function and barrier heights of transition metal silicides. Appl. Phys. A 40, 71–77 (1986)

J. Hu, K.C. Saraswat, H.S.P. Wong, Metal/III-V Schottky barrier height tuning for the design of nonalloyed III-V field-effect transistor source/drain contacts. J. Appl. Phys. 107, 063712 (2010)

N. Newman, M. Vanschilfgaarde, T. Kendelwicz, M.D. Williams, W.E. Spicer, Electrical study of Schottky barriers on atomically clean GaAs(110) surfaces. Phys. Rev. B 33, 1146–1159 (1986)

M.C. Özdemir, Ö. Sevgili, I. Orak, A. Türüt, Determining the potential barrier presented by the interfacial layer from the temperature induced I-V characteristics in Al/p-Si Structure with native oxide layer. Mater. Sci. Semicond. Proc. 125, 105629 (2021)

K. Maeda, H. Ikoma, K. Sato, T. Ishida, Current-voltage characteristics and interface state density of GaAs Schottky-barrier. Appl. Phys. Lett. 62, 2560–2562 (1993)

A. Türüt, On current-voltage and capacitance-voltage characteristics of metal-semiconductor contacts. Turk. J. Phys. 44, 302–347 (2020)

H. Hasegawa, H. Ohno, Unified disorder induced gap state model for insulator–semiconductor and metal–semiconductor interfaces. J. Vac. Sci. Technol. B 4, 1130–1138 (1986)

D. Tsukamoto, A. Shiro, Y. Shiraishi, Y. Sugano, S. Ichikawa, S. Tanaka, T. Hirai, Photocatalytic H2O2 production from ethanol/O2 system using TiO2 loaded with Au–Ag bimetallic alloy nanoparticles. ACS Catal. 2, 599–603 (2012)

S. Küp, A. Taşer, İ Kanmaz, B. Güzeldir, M. Sağlam, Effects of Au-Ag and Au-Cu alloy ratios on the temperature dependent current-voltage characteristics of Au-Ag/n-GaAs/In and Au-Cu/n-GaAs/In Schottky diodes. Mater. Today Proc. 18, 1936–1945 (2019)

J.R. Waldrop, Electrical-properties of ideal metal contacts to GaAs - Schottky-barrier height. J. Vac. Sci. Technol. B 2, 445–448 (1984)

Ö. Güllü, M. Biber, S. Duman, A. Türüt, Electrical characteristics of the hydrogen pre-annealed Au/n-GaAs Schottky barrier diodes as a function of temperature. Appl. Surf. Sci. 253, 7246–7253 (2007)

F. Yiğiterol, H.H. Güllü, Ö. Bayraklı, D.E. Yıldız, Temperature-dependent electrical characteristics of Au/Si3N4/4H n-SiC MIS diode. J. Electron. Mater. 47, 2979–2987 (2018)

D.E. Yıldız, Electrical properties of Au–Cu/ZnO/p-Si diode fabricated by atomic layer deposition. J. Mater. Sci. 29, 17802–17808 (2018)

G.K. Reeves, H.B. Harrison, Obtaining the specific contact resistance from transmission-line model measurements. Electron Device Lett. 3, 111–113 (1982)

A. Akkaya, E. Ayyıldız, Automation software for semiconductor research laboratories: electrical parameter calculation program (SeCLaS-PC). J. Circuits Syst. Comput. 29, 2050215 (2020)

A. Akkaya, E. Ayyıldız, Automation software for semiconductor research laboratories: Measurement System and Instrument Control Program (SeCLaS-IC). MAPAN 35, 343–350 (2020)

S. Fain Jr., J. McDavid, Work-function variation with alloy composition: Ag-Au. Phys. Rev. B 9, 5099 (1974)

R. Ishii, K. Matsumura, A. Sakai, T. Sakata, Work function of binary alloys. Appl. Surf. Sci. 169–170, 658–661 (2001)

C. Kittel, Introduction to Solid State Physics (Wiley, Hoboken, 1996)

H.I. Chen, C.K. Hsiung, Y.I. Chou, Characterization of Pd-GaAs Schottky diodes prepared by the electroless plating technique. Semicond. Sci. Technol. 18, 620–626 (2003)

A. Türüt, D.E. Yıldız, A. Karabulut, İ Orak, Electrical characteristics of atomic layer deposited Au/Ti/HfO2/n-GaAs MIS diodes in the wide temperature range. J. Mater. Sci. 31, 7839–7849 (2020)

A. Akkaya, L. Esmer, B.B. Kantar, H. Çetin, E. Ayyıldız, Effect of thermal annealing on electrical and structural properties of Ni/Au/n-GaN Schottky contacts. Microelectron. Eng. 130, 62–68 (2014)

J. Ahopelto, V.M. Airaksinen, E. Siren, H.M. Niemi, Fabrication of sub-100 nm GaAs columns by reactive ion etching using Au islands as etching mask. J. Vac. Sci. Technol. B 13, 161–162 (1995)

V.G. Weizer, N.S. Fatemi, The interaction of gold with gallium arsenide. J. Appl. Phys. 64, 4618–4623 (1988)

C. Messmer, J.C. Bilello, The surface energy of Si, GaAs, and GaP. J. Appl. Phys. 52, 4623–4629 (1981)

S. Sze, Physics of Semiconductor Devices (John Wiley & Sons, New York, 1981)

L. Huang, R. Geiod, D. Wang, Barrier inhomogeneities and interface states of metal/4H-SiC Schottky contacts. Jpn. J. Appl. Phys. 55, 124101 (2016)

A.K. Sinha, J.M. Poate, Effect of alloying behavior on the electrical characteristics of n-GaAs Schottky diodes metallized with W, Au, and Pt. Appl. Phys. Lett. 23, 666–668 (1973)

D. Eastman, Photoelectric work functions of transition, rare-earth, and noble metals. Phys. Rev. B 2, 1 (1970)

M. Soylu, F. Yakuphanoğlu, Analysis of barrier height inhomogeneity in Au/n-GaAs Schottky barrier diodes by Tung model. J. Alloys Compd. 506, 418–422 (2010)

H. Altuntaş, S. Altındal, S. Özçelik, H. Shtrikman, Electrical characteristics of Au/n-GaAs Schottky barrier diodes with and without SiO2 insulator layer at room temperature. Vacuum 83, 1060–1065 (2009)

S. Tunhuma, F. Auret, M. Legodi, M. Diale, The effect of high temperatures on the electrical characteristics of Au/n-GaAs Schottky diodes. Phys. B 480, 201–205 (2016)

A.F. Özdemir, A. Türüt, A. Kökce, The double Gaussian distribution of barrier heights in Au/n-GaAs Schottky diodes from I-V-T characteristics. Semicond. Sci. Technol. 21, 298–302 (2006)

D. Korucu, A. Türüt, H. Efeoğlu, Temperature dependent I-V characteristics of an Au/n-GaAs Schottky diode analyzed using Tung’s model. Phys. B 414, 35–41 (2013)

S. Arulkumaran, J. Arokiaraj, M. Udhayasankar, P. Santhanaraghavan, J. Kumar, P. Ramasamy, Investigations on Au, Ag, and Al Schottky diodes on liquid encapsulated Czochralski-Grown N-GaAs[100]. J. Electron. Mater. 24, 813–817 (1995)

J.R. Waldrop, Influence of S and Se on the Schottky-barrier height and interface chemistry of Au contacts to GaAs. J. Vac. Sci. Technol. B 3, 1197–1201 (1985)

O. Kahveci, A. Akkaya, E. Ayyıldız, A. Türüt, Comparison of yhe Ti/N-GaAs Schottky contacts’ parameters fabricated using DC magnetron sputtering and thermal evaporation. Surf. Rev. Lett. 24, 1750047 (2016)

S.W. Pang, G.A. Lincoln, R.W. McClelland, P.D. DeGraff, M.W. Geis, W.J. Piacentini, Effects of dry etching on GaAs. J. Vac. Sci. Technol. B 1, 1334–1337 (1983)

S. Guha, B.M. Arora, V.P. Salvi, High temperature annealing behaviour of Schottky barriers on GaAs with gold and gold-gallium contacts. Solid State Electron. 20, 431–432 (1977)

A.H. Kacha, M. Anani, B. Akkal, Z. Benamara, G. Monier, H. Mehdi, C. Varenne, A. Ndiaye, C. Robert-Goumet, Effect of metallic contacts diffusion on Au/GaAs and Au/GaN/GaAs SBDs electrical quality during their fabrication process. J. Alloys Compd. 876, 159596 (2021)

T. Nishimura, K. Kita, A. Toriumi, A significant shift of Schottky barrier heights at strongly pinned metal/germanium interface by inserting an ultra-thin insulating film. Appl. Phys. Express 1, 051406 (2008)

M.L. Cohen, Schottky and Bardeen limits for Schottky barriers. J. Vac. Sci. Technol. 16, 1135–1136 (1979)

R.T. Tung, Chemical bonding and Fermi level pinning at metal-semiconductor interfaces. Phys. Rev. Lett. 84, 6078–6081 (2000)

M. Ambrico, M. Losurdo, P. Capezzuto, G. Bruno, T. Ligonzo, L. Schiavulli, I. Farella, V. Augelli, A study of remote plasma nitrided nGaAs/Au Schottky barrier. Solid State Electron. 49, 413–419 (2005)

S.K. Cheung, N.W. Cheung, Extraction of Schottky diode parameters from forward current-voltage characteristics. Appl. Phys. Lett. 49, 85–87 (1986)

H. Norde, A modified forward I-V plot for Schottky diodes with high series resistance. J. Appl. Phys. 50, 5052–5053 (1979)

M. Sağlam, E. Ayyıldız, A. Gümüs, A. Türüt, H. Efeoğlu, S. Tüzemen, Series resistance calculation for the metal-insulator-semiconductor Schottky barrier diodes. Appl. Phys. A-Mater. 62, 269–273 (1996)

Ş Karataş, Temperature and voltage dependence C-V and G/ω–V characteristics in Au/n-type GaAs metal–semiconductor structures and the source of negative capacitance. J. Mater. Sci. 32, 707–716 (2021)

O. Çiçek, H. Durmuş, Ş Altındal, Identifying of series resistance and interface states on rhenium/n-GaAs structures using C-V–T and G/ω–V–T characteristics in frequency ranged 50 kHz to 5 MHz. J. Mater. Sci. 31, 704–713 (2020)

K.E. Bohlin, Generalized Norde plot including determination of the ideality factor. J. Appl. Phys. 60, 1223–1224 (1986)

O. Güllü, S. Aydoğan, A. Türüt, Fabrication and electrical properties of Al/Safranin T/n-Si/AuSb structure. Semicond. Sci. Technol. 23, 075005 (2008)

S. Leung, T. Yoshiie, C.L. Bauer, A.G. Milnes, Electrical properties, structure, and phase morphology of Au-Ga alloy films codeposited on GaAs substrates. J. Electrochem. Soc. 132, 898–903 (1985)

S. Demirezen, E. Özavci, S. Altındal, The effect of frequency and temperature on capacitance/conductance-voltage (C/G-V) characteristics of Au/n-GaAs Schottky barrier diodes (SBDs). Mater. Sci. Semicond. Process. 23, 1–6 (2014)

V.R. Reddy, Electrical properties of Au/polyvinylidene fluoride/n-InP Schottky diode with polymer interlayer. Thin Solid Films 556, 300–306 (2014)

D.E. Yıldız, M. Karakuş, L. Toppare, A. Cirpan, Leakage current by Frenkel-Poole emission on benzotriazole and benzothiadiazole based organic devices. Mater. Sci. Semicond. Process. 28, 84–88 (2014)

J.H. Werner, H.H. Güttler, Barrier inhomogeneities at Schottky contacts. J. Appl. Phys. 69, 1522–1533 (1991)

J.H. Werner, H.H. Güttler, Transport properties of inhomogeneous Schottky contacts. Phys. Scripta 1991, 258 (2007)

R.T. Tung, Recent advances in Schottky barrier concepts. Mater. Sci. Eng. R 35, 1–138 (2001)

W.A. Hill, C.C. Coleman, A single-frequency approximation for interface-state density determination. Solid State Electron. 23, 987–993 (1980)

E.H. Nicollian, J.R. Brews, Mos (Metal Oxide Semiconductor) Physics And Technology (Wiley-Interscience, New York, 1982)

D. Korucu, S. Altındal, T.S. Mammadov, S. Özçelik, The frequency dependent electrical characteristics of Sn/p-InP Schottky barrier diodes (SBDs). Optoelectron. Adv. Mater. 2, 525–529 (2008)

Funding

Not applicable.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

All the authors declared that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Akkaya, A. Au–Ag binary alloys on n-GaAs substrates and effect of work functions on Schottky barrier height. J Mater Sci: Mater Electron 32, 17448–17461 (2021). https://doi.org/10.1007/s10854-021-06276-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-021-06276-9