Abstract

In this study, we investigated the effects of applied voltage and frequencies on the electrical properties of Al/(Er2O3(150 nm)/SiO2(20 nm)/n-Si)/Al MOS capacitor. The e-beam deposited Er2O3/SiO2 films were annealed at 650 °C in N2 ambient and the crystal and phase identification of the films were confirmed by X-ray diffractometry. The capacitance–voltage (C–V) and the conductance–voltage (G/ω–V) measurements of the MOS capacitor were carried out for voltage frequencies from 50 kHz to 1 MHz at several steps. The parameters of doping concentration, diffusion potential, built-in potential, barrier height, Fermi energy level, the image force barrier lowering and the depletion layer width were calculated by C–V and G/ω–V data. While the depletion layer width decreased with increasing frequencies, the diffusion potential and the barrier height increased a little with small frequencies (200 kHz ≤ f) first, then decreased insignificantly. We also studied the frequency effects on the series resistance (Rs) and the interface state density (Dit) through the C–V and G/ω–V curves, and found noticeable decreases in Rs and Dit values with increasing frequency. The measured and calculated results reveal that both Rs and Dit frequency dependence have significant impacts on Er2O3/SiO2/n-Si MOS capacitor properties. These effects are basically because of the interfacial charge behavior of thin SiO2 layer contained in between n-Si and Er2O3.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

For new generation highly advanced complementary metal oxide semiconductor (CMOS) technology, the improved electronic devices with well-known features are required. The metal–oxide–semiconductor (MOS) capacitors are used in many different application areas of optoelectronics, microelectronics, thermophotovoltaic and biomedical applications since they have outstanding optical and electrical properties [1]. The early MOS capacitors had SiO2 as the oxide layer between metal and semiconductor. Because of the excessive gate leakage current associated with the SiO2 layer which leads an increase in static power consumption and error in logic devices, of late, research is on finding better high permittivity (high-k) alternatives to the SiO2 layer [2]. In the past decade, for the highly advanced complementary metal oxide semiconductor (CMOS) technology, many high-k materials such as Pr2O3, Al2O3, Er2O3, Sr2O3, HfO2, ZrO2, La2O3, Fe2O4, Dy2O3, and TiO2 have been proposed as possible alternatives to SiO2 [3,4,5,6]. However, Er2O3 is one of the promising high-k materials that has pluses over SiO2 because it owns a higher dielectric constant (10–14), a wider bandgap (~ 5.4 eV), a relatively large conduction band offset (\(\sim \) 3.5 eV), and lower gate leakage current [7]. Despite that, there are still some issues concerning the degradation of the metal–oxide–semiconductor (MOS) device reliability, this is because of the difficulty in finding a high-k material that has a perfect interface match with Si as compared to SiO2. For this reason, an extremely thin SiO2 layer is deposited onto the Si before the high-k layer reducing the lattice mismatch. Besides, the SiO2 interfacial layer could not only reduce the lattice match but it would also increase the thermodynamic stability between high-k materials and Si [2]. A high thermodynamic stability reduces the formation of silicides and rugged surfaces [8].

Among many other deposition techniques to fabricate Er2O3 thin films, we had used the electron beam (e-beam) vapor deposition technique. The e-beam evaporation is a physical vapor deposition (PVD) technique whereby an intense electron beam is generated from a filament and steered via electric and magnetic fields to strike the source material and vaporize it within a vacuum environment [9, 10]. This technique has some key advantages over the other techniques; it has high and controllable rate of deposition, high density, and homogeneity of the prepared thin films, etc. The e-beam PVD technique has attracted much more attention because such technique has control on porosity, film structure, stoichiometry film growth rate. All these parameters may be controlled by varying the deposition conditions. This method has also been used to deposit high-k films because of controllable interface growth and low contamination. While in many other techniques an oxidation interface layer occurs on Si substrate due to oxygen ambient at high annealing temperatures, it does not happen in the e-beam PVD technique [11].

In this work, we systematically investigated the Er2O3/SiO2/n-Si structure deposited by e-beam PVD technique and determined the electrical characteristics for MOS capacitor such as barrier height (ΦB), diffusion potential (VD), donor concentration (ND), Fermi energy level (EF), and depletion layer width (WD) by measured capacitance–voltage (C–V) and conductance–voltage (G/ω–V) data. We also studied the behavior of the interface states density (Dit) and the series resistance (Rs) through C–V and G/ω–V data for frequencies from 50 kHz to 1 MHz at room temperature.

2 Experimental details

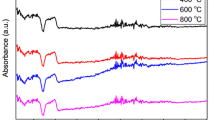

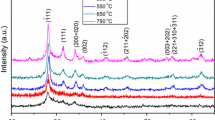

Four samples were annealed in N2 atmosphere at temperatures ranging from 450 to 750 °C to optimize crystallinity. All samples were analyzed by X-ray diffraction and found that the sample annealed at 650 °C illustrated a good cubic structure and may exhibit interesting electrical properties.

In order to fabricate the MOS capacitor, a 6-inch, 500 μm thick n-type Si wafer (100) with resistivity of 2–4 cm \(\Omega \) was dried using nitrogen gas. Following the standard RCA cleaning procedure, the SiO2 layer was grown on n-Si by dry oxidation at 1000 °C. The Er2O3 thin film was deposited on SiO2/n-Si structure by e-beam evaporation under the pressure of 3 × 10–4 Torr in the growth rate of 1.5 Å/s. The thickness of SiO2 and Er2O3 layers were measured using Angstrom Sun Spectroscopic reflectometer and found to be 20 nm and 150 nm, respectively. Then a portion of deposited Er2O3/SiO2 film was annealed at 650 °C for 30 min under N2 ambient with the flow rate of 1000 sccm. Metallization processes were performed to convert annealed thin films to MOS capacitors. A shadow mask with 1.5 mm circular dots was placed on the Er2O3/SiO2/Si structure, with aluminum (Al) deposition at 120 W by RF magnetron sputtering. The back contact was obtained by covering the entire back surface in the same conditions with front contacts. Al contacts were used to reduce possible signal loss and to eliminate a possible potential barrier that may form between the electrode and semiconductor interface. As schematically shown in Fig. 1, the Al/(Er2O3/SiO2/n-Si)/Al MOS capacitors were fabricated. The films’ structure was characterized by Rigaku 2500PC X-ray diffraction (XRD) with the CuKα characteristic X-ray wavelength of 1.5 Å. The 2\(\theta \) range was between 10° and 80°. The 2\(\theta \) step and the step acquisition time were 0.01 and 5 per second for all diffract grams.

The surface morphology of the 150 nm Er2O3 film was analyzed using AFM. Figure 2 shows the AFM image of the Er2O3 film in 3D with the size of 4 μm × 4 μm. The film is characterized by the roughness root-mean-square (Rq) which is obtained to be 1.77 nm as deposited. For the film annealed at 650 °C, the Rq is obtained to be 2.3 nm. The increase in roughness is related to the film thickness of Er2O3.

The electrical measurements; C–V and G/ω–V were performed with the Keithley 4200-SCS Parameter Analyzer for voltage raised from − 5 to 5 V at frequencies from 50 kHz to 1 MHz in a 50 step first, then at 100 kHz steps at room temperature. Finally, all of the fabrication processes and the experiments were performed in Class-100 cleanroom laboratories in Bolu Abant Izzet Baysal University Nuclear Radiation Detectors Application and Research Center, Turkey.

3 Measurements, calculations and discussions

The obtained XRD spectra of the Er2O3/SiO2/n-Si were given in Fig. 3. While the as-deposited Er2O3/SiO2 film shows polycrystalline structure weak spectrum peaks, the annealed sample at 650 °C for 30 min in a nitrogen environment exhibits stronger reflections peaks, in particular, the peaks at 2 = \(\theta \)21.0°, 29.5°, 35.0°, 48.9°, and 58.6° can be associated to reflections for the (211), (222), (400), (440), and (622) planes of the Er2O3 cubic lattice with the lattice parameter of 10.54 Å [9, 12, 13]. It is observed that the preferred orientation of the fabricated film is in the cubic phase structure with (222). The peaks were indexed by the International Centre for Diffraction Data (ICCD) card number 77–0463.

In general, the capacitance of a dielectric material (Cdie) inserted between metal electrodes is given as

where εo is the permittivity of free space (8.85 × 10–12 F/m), κdie is the dielectric constant of dielectric layer (SiO2 (3.9)) or (Er2O3 (14)) used for calculation, A is the metal gate electrode area (Al (1.77 × 10–2 cm2)) and tox is the thickness of the dielectric (SiO2 (20 nm) or Er2O3 (150 nm)). Calculated capacitance of \({\mathrm{C}}_{\mathrm{S}\mathrm{i}\mathrm{O}2}\) = 3.05 × 10–9 F and \({\mathrm{C}}_{{\mathrm{E}\mathrm{r}}_{2}{\text{O}}_{3}}\) = 1.46 × 10–9 F.

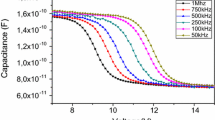

In Fig. 4a, the total oxide capacitance of the sample equivalent to the series of the capacitance of the SiO2 layer and the Er2O3 layer is represented and calculated by the following equation [14,15,16].

a Equivalent capacitance to the series of the capacitances SiO2 layer and Er2O3 layer. b Measured capacitance (Cm) of Al/(Er2O3/SiO2/n-Si)/Al MOS capacitor for various frequency ranges from 50 kHz to 1 MHz. c Measured conductance (Gm/ω) of Al/(Er2O3/SiO2/n-Si)/Al MOS capacitor for various frequencies ranges from 50 kHz to 1 MHz

where CSiO2 and CEr2O3 are the capacitances of the SiO2 and Er2O3 layers, respectively. By substituting calculated CSiO2 and CEr2O3 values into Eq. (2), the total oxide capacitance (Cox) was found to be 9.89 × 10–10 F.

Figure 4b, c show C–V and G/ω–V data accomplished over the frequency range of 50 kHz and 1 MHz. As shown in Fig. 4b, the capacitance tends to decrease with increasing frequency. However, as the frequency is raised, the capacitance reduces to a limit and stays there because the defect charges have no enough time to rearrange and response to the applied voltage.

As shown in Fig. 4c, the existence of Rs causes the measured conductance (Gm/ω) to increase with increasing frequency while the admittance peaks reduce relatively as the frequency increases, however, when Gm is corrected (GC/ω), it decreases with frequency (See Fig. 7). This indicates that at low frequencies, flow of charge through the interface is possible and the characteristics depend on the relaxation time and the AC signal frequency [17].

At a given frequency, most of the errors in the C–V and G/ω–V features are due to the series resistance (Rs) in the strong accumulation region and a portion of the depletion region.

Using Nicollian and Goetzberger calculation approach, the Rs of MOS devices may be deducted from the strong accumulation region measurements of the capacitance (Cma) and the conductance (Gma) at high frequencies (≥ 200 kHz) [18, 19]. For the capacitor biased into strong accumulation region, the frequency-dependent complex impedance of MOS device can be described as

where \(\upomega =2\uppi \mathrm{f}\) is the voltage angular frequency. Using the real part of Eq. (3), the Rs values can be found for the given frequencies [20].

The calculated Rs values versus voltage frequency are calculated and plotted in Fig. 5 for Al/(Er2O3/SiO2/n-Si)/Al MOS capacitor. The Rs values are varying in range of 850–32 Ω for frequencies of 50–600 kHz, and 29–25 Ω for frequencies of 700–1000 kHz as voltage increases from − 5 V to about − 2.25 V. The Rs get their peak values at around − 1.5 V as voltage increases from − 2.25 to − 0.375 V. Later, as shown in Fig. 5 (emplacement), when voltage increased from − 0.375 to 5 V the peaks disappear and Rs decrease, become stable and remained fixed in 84–27 Ω range for frequencies of 50–600 kHz, and 25–23 Ω range for frequencies of 700–1000 kHz [21]. The reason for this to happen is the displacement and rearrangement of the frequency-dependent charges such as fixed oxide charge, oxide trapped charge, mobile oxide charge, and interface trapped charge. The C–V and G/ω–V were corrected due to the fact that Rs is voltage dependent at the strong accumulation region as seen in Rs–V plot (Fig. 5). In addition, the interface trap charges may have enough energy to jump through traps placed between the metal (rear contact) and the semiconductor interface in the Si bandgap [17, 18].

The C–V and G/ω–V data were corrected by the use of strong accumulation region Rs values [21]. The corrected capacitance (CC) and corrected conductance (GC) are calculated from the equations [22].

where

Figures 6 and 7 show the Cc–V and Gc/ω–V curves of the MOS capacitor measured in the voltage raised from − 5 to 5 V. There is no significant change between the C–V and the Cc–V curves because the thin SiO2 layer deposited onto the Si to reduce the lattice mismatch keeps the capacitance almost the same. However, in G/ω–V and Gc/ω–V curves, there is an important variation. After the measured conductance is corrected, the admittance peaks fade away as the frequency increases. This fading is attributed to the decrease in Rs which is demonstrated by Fig. 5 and in Table 1.

The interface state density, Dit was calculated using the Hill-Coleman method by the equation [22, 23].

where q is the elementary charge (1.60 × 10–19 C), A is the gate electrode area of the MOS capacitor (1.77 × 10–2 cm2), Gc.max/ω are maximum values of Gc/ω collected from the Gc/ω–V curve, CC is corrected capacitance of the MOS capacitor corresponding to Gc.max, and Cox is the equivalent (total) capacitance of oxides.

As shown in Fig. 8 and Table 1, the Dit decreases as a reciprocal function (~ 1.5f−0.09 × 1011) with the increase of applied bias voltage frequency, f. Particularly, at low frequencies the interface density is strongly dependent on frequency which leads an increase in the capacitance of the MOS structure in strong accumulation region. On the other hand, it is expected that at high frequencies (> 1 MHz), the interface densities to be negligibly dependent on frequency because at low frequencies while the Dit can follow the applied voltage signal, at high frequencies the Dit cannot. This is because its transport mechanisms are too slow compared to the signal [21, 24].

Acceptor-like interface states and donor-like interface states are the two interface states affecting ΦB. The ΦB, ND, EF, and VD are obtained from the reciprocal squared of corrected Cc−2–V plot. At higher frequencies, it is observed that linearity of the obtained Cc−2–V curves increases indicating the uniform distribution of interface states in the device structure given Fig. 9.

The relation between Cc−2 and V is given as [22, 23]

where m is the slope and mVo is the intercept that determined from Cc−2–V plot given in Fig. 9.

where A is the gate electrode area (1.77 × 10–2 cm2), κs is the dielectric constant of silicon (11.9 for n-Si). From Eq. (10)

ND is the free electron concentration when all shallow donor levels are ionized, V is the applied bias voltage and Vo is the built-in potential. From the intercept of Cc−2–V plot with the V axis, Vo (= intercept/m) can be determined by Eq. (9) [17,18,19]

where VD is the diffusion potential, \({k}_{\mathrm{B}}\) is the Boltzmann’s constant (1.38 \(\times \) 10–23 JK−1), T is the room temperature in Kelvin (300 K). The barrier height (ΦB) may be calculated using the Cc−2–V measurements in the equation [25].

where c2 is the correction factor which is the relationship between the theoretical doping concentration (ND = 4.31 × 1015 cm−3) and the experimental values and can be extracted from the slope of C−2–V curves or may be given as c2 ≈ ND(exp.)/ND(th.) [4, 26,27,28], \({E}_{\text{F}}=\frac{{k}_{\text{B}}T}{q}\mathrm{l}\mathrm{n} (\frac{{N}_{\text{C}}}{{N}_{\text{D}}})\) is the Fermi energy level, NC (2.82 × 1019 cm−3) is the effective density of states [∼5.0 × 1015 T3/2 (m∗n/mo), T = 300 K, m∗n/mo = 1.08 for n-Si] in the conduction band for n-Si at room temperature, and ΔΦB is the image force barrier lowering which is calculated from

Em is the maximum electric field [29, 30].

The obtained electrical parameters are listed in Table 2. Diffusion potentials VD(s) are located at negative voltages indicating that positive charges are trapped in the MOS capacitor in the fabrication process. Furthermore, as seen in Table 2, the doping concentration ND, increases with increasing applied voltage frequency. The Fermi level EF is almost constant with varying applied voltage frequency. ΔΦB varies a little about 1.773 \(\times \) 10–3 eV depending on the frequency. VD and Vo are related through temperature (Vo = VD − kBT/q, T = 300 K) and values are very close. They increase for 50 kHz and 100 kHz frequencies then decrease with the increase of frequency accordingly. The Cc−2–V data also reveals that ΦB stays almost constant. This is because of the dependence of the built-in potential Vo, EF, and ΔΦB. Finally, the depletion layer width (WD) is given by the equation,

where VD is the diffusion potential and ND is the free electron concentration. Depending on VD/ND ratio WD decreases from 1.117 × 10–4 to 1.029 × 10–4 cm with increasing frequency (see Table 2) [18, 29].

4 Conclusion

In summary, the electrical parameters of Al/(Er2O3/SiO2/n-Si)/Al MOS capacitor such as Rs, Dit, ΦB, ΔΦB, Vo, VD, ND, WD, and EF were determined from frequency-dependent C–V, G/ω–V and Cc−2–V data. The experimental results show that the ΦB and VD increases for 50–100 kHz frequencies and then decrease with increasing frequency. We also investigated the effects on the series resistance (Rs) and the interface state density (Dit) through the C–V and G/ω–V plots. From the obtained results, we noticed that the effect of voltage and frequency on Rs reduction is significant. The introduction of SiO2 layer between the high-k Er2O3 and n-Si appears to be the main reason for Rs reduction. Rs–V (Fig. 5) and G/ω–V (Fig. 7) curves demonstrate a strong and high response at − 1.5 V for all frequencies. However, at voltages greater than − 0.375 V Rs decreases, becomes stable and remains fixed. Similarly, the admittance peaks reduced and disappeared at high frequencies. The disappearance of these peaks from Figs. 5 and 7 is because the interface charges can hardly follow the AC signal at high frequencies. Calculations also show that Dit is affected by frequencies greatly. Figure 8 shows the decrease in Dit as a reciprocal function (~ 1.5f−0.09 × 1011) of the applied voltage frequency. Especially, at low frequencies, Dit is strongly dependent on frequency which leads an increase in the capacitance of the MOS structure in the strong accumulation region. However, at high frequencies, Dit cannot follow the AC signal since its transport mechanisms are too slow compared to the signal.

References

R. Lok, S. Kaya, H. Karacali, E. Yilmaz, A detailed study on the frequency-dependent electrical characteristics of Al/HfSiO4/p-Si MOS capacitors. J. Mater. Sci. Mater. Electron. 27(12), 13154–13160 (2016)

C.S. Pang, J.G. Hwu, Improvement in the breakdown endurance of high-κ dielectric by utilizing stacking technology and adding sufficient interfacial layer. Nanoscale Res. Lett. 9(1), 1–7 (2014)

J. Robertson, R.M. Wallace, High-k materials and metal gates for CMOS applications. Mater. Sci. Eng. R Rep. 88, 1–41 (2015)

Ç.G. Türk, S.O. Tan, S. Altındal, B. Inem, Frequency and voltage dependence of barrier height, surface states, and series resistance in Al/Al2O3/p-Si structures in wide range frequency and voltage. Phys. B 582, 411979–411985 (2020)

Seçkin Altındal Yerişkin, The investigation of effects of (Fe2O4-PVP) organic-layer, surface states, and series resistance on the electrical characteristics and the sources of them. J. Mater. Sci. 30, 17032–17039 (2019)

Y. Badali, A. Nikravan, Ş. Altindal, I. Uslu, Effects of a thin Ru-doped PVP Interface layer on electrical behavior of Ag/n-Si structures. J. Electron. Mater. 47, 3510–3520 (2018)

C.H. Kao, H. Chen, Y.T. Pan, J.S. Chiu, T.C. Lu, The characteristics of the high-k Er2O3 (erbium oxide) dielectrics deposited on polycrystalline silicon. Solid State Commun. 152(6), 504–508 (2012)

V. Mikhelashvili, G. Eisenstein, F. Edelmann, Structural properties and electrical characteristics of electron-beam gun evaporated erbium oxide films. Appl. Phys. Lett. 80(12), 2156–2158 (2002)

S. Abubakar, E. Yilmaz, Optical and electrical properties of E-Beam deposited TiO2/Si thin films. J. Mater. Sci. 29(12), 9879–9885 (2018)

H.S. Kamineni et al., Optical and structural characterization of thermal oxidation effects of erbium thin films deposited by electron beam on silicon. J. Appl. Phys. 111(1), 013104 (2012)

R. Messier, Thin film deposition processes. MRS Bull. 13(11), 18–21 (1988)

X. Queralt, C. Ferrater, F. Sánchez, R. Aguiar, J. Palau, M. Varela, Erbium oxide thin films on Si(100) obtained by laser ablation and electron beam evaporation. Appl. Surf. Sci. 86(1–4), 95–98 (1995)

A. Kahraman, E. Yilmaz, A. Aktag, S. Kaya, Evaluation of radiation sensor aspects of Er2O3 MOS capacitors under zero gate bias. IEEE Trans. Nucl. Sci. 63(2), 1284–1293 (2016)

M. Miritello et al., Optical and structural properties of Er2O3 films grown by magnetron sputtering. J. Appl. Phys. 100, 13502–13507 (2006)

Y. Wang, R. Jia, C. Li, Y. Zhang, Electric properties of La2O3/SiO2/4H-SiC MOS capacitors with different annealing temperatures. AIP Adv. 5(8), 3–8 (2015)

F. Ze-Bo, Z. Yan-Yan, W. Jia-Le, J. Zui-Min, Annealing effects on the structure and electrical characteristics of amorphous Er2O3 films. Chinese Phys. B 18(8), 3542–3546 (2009)

A. Tataroğlu, G.G. Güven, S. Yilmaz, A. Büyükbas, Analysis of barrier height and carrier concentration of MOS capacitor using C-f and G/ω-f measurements. Gazi Univ. J. Sci. 27(3), 909–915 (2014)

A.R. Wazzan, MOS (Metal oxide semiconductor) physics and technology. Nucl. Technol. 74(2), 235–237 (1986)

S. Kaya, R. Lok, A. Aktag, J. Seidel, E. Yilmaz, Frequency dependent electrical characteristics of BiFeO3 MOS capacitors. J. Alloys Compd. 583, 476–480 (2014)

I. Dökme, Ş. Altindal, “On the profile of frequency and voltage dependent interface states and series resistance in MIS structures. Phys. B 393(1–2), 328–335 (2007)

I. Yücedağ, Ş. Altindal, A. Tataroğlu, On the profile of frequency dependent series resistance and dielectric constant in MIS structure. Microelectron. Eng. 84(1), 180–186 (2007)

S. Kaya, E. Yilmaz, A comprehensive study on the frequency-dependent electrical characteristics of Sm2O3 MOS capacitors. IEEE Trans. Electron. Dev. 62(3), 980–987 (2015)

S. Kaya, E. Yilmaz, Use of BiFeO3 layer as a dielectric in MOS based radiation sensors fabricated on a Si substrate. Instru. Methods Phys. Res. Sect. B 319, 168–170 (2014)

S. Zeyrek, E. Acaroğlu, Ş. Altindal, S. Birdoǧan, M.M. Bülbül, The effect of series resistance and interface states on the frequency dependent C-V and G/w-V characteristics of Al/perylene/p-Si MPS type Schottky barrier diodes. Curr. Appl. Phys. 13(7), 1225–1230 (2013)

A.M. Goodman, Metal—semiconductor barrier height measurement by the differential capacitance method—one carrier system. J. Appl. Phys. 34(2), 329–338 (1963)

A. Tataroğlu, Ş. Altindal, M.M. Bülbül, Temperature and frequency dependent electrical and dielectric properties of Al/SiO2/p-Si (MOS) structure. Microelectron. Eng. 81(1), 140–149 (2005)

S. Kaya, E. Yilmaz, A detailed study on frequency dependent electrical characteristics of MOS capacitors with dysprosium oxide gate dielectrics. Semicond. Sci. Technol. 35, 25002–25010 (2020)

S. Alptekin, Ş. Altındal, A comparative study on current/capacitance: voltage characteristics of Au/n-Si (MS) structures with and without PVP interlayer. J. Mater Sci. 30, 6491–6499 (2019)

D.A. Neamen, Semiconductor Physics and Devices: Basic Principles, 4th edn. (The McGraw-Hill Companies Inc, New York, 2012)

A. Kahraman, U. Gurer, R. Lok, S. Kaya, E. Yilmaz, “Impact of interfacial layer using ultra-thin SiO2 on electrical and structural characteristics of Gd2O3 MOS capacitor. J. Mater. Sci. 29, 17473–917482 (2018)

Acknowledgment

This work is supported by the Presidency of Turkey, Presidency of Strategy and Budget under Contract Number: 2016K121110.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Aktağ, A., Mutale, A. & Yılmaz, E. Determination of frequency and voltage dependence of electrical properties of Al/(Er2O3/SiO2/n-Si)/Al MOS capacitor. J Mater Sci: Mater Electron 31, 9044–9051 (2020). https://doi.org/10.1007/s10854-020-03438-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-020-03438-z