Abstract

The detailed electrical characterizations of Al/HfSiO4/p-Si (MOS) capacitors were investigated. HfSiO4 thin films were fabricated by RF sputtering system with the power of 300 W onto p-type (100) Si substrate and then annealed at 750 °C in Nitrogen environment for 40 min. After fabrication of ohmic contacts, the electrical characteristics of the capacitors were determined by C–V and G/ω–V measurements for several frequencies from 50 kHz to 1 MHz. It is observed that the measured capacitance and conductance curves are quite sensitive to applied voltage frequency due to time dependent interface states (Dit), border traps (Nbt), and series resistance (Rs). We have observed that the series resistance may significantly deviate from the MOS capacitor characteristics and the relevant correction must be performed. In addition, the calculated interface state density was found to be in the order of 1010 eV−1 cm−2 which is in good agreement with reported convenient dielectric layers for MOS based technology. Moreover flat band voltage variation also observed under applied voltage frequencies and this behavior were attributed the basically border states. On the other hand, barrier potentials varied from 0.615 to 0.559 eV with increasing in frequencies depending on the charge accumulations due to time dependent trap sites. Consequently, Dit, Nbt, Rs are important factors that can affect electrical characteristics of the MOS capacitors. Although the reported values vary under different applied frequencies, the fabricated HfSiO4 dielectric layer exhibits demanding electrical characteristics to be used in MOS-based technologies.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Metal–oxide–semiconductor (MOS) capacitors have been widely used for various applications because of their excellent optical and electrical properties [1]. The usability and suitability of a MOS capacitor in nanotechnology and semiconductor device industry depend on devices characteristic which are directly related to the gate dielectrics and their interfaces with the underlying semiconductors, especially for their electrical characteristics [2–5].

Hafnium silicates (HfSi04) may be a good alternative gate material with high dielectric constant. Hafnium silicate dielectric constant changed between 15 and 25 [6] depending on halfnium (Hf) content. It has excellent thermal stability, adequate band gaps, and compatibility for future MOS-based devices [7–10]. These characteristics of Hafnium silicate are related to the electrical stability of interface between gate oxide and underlying semiconductors [10]. In MOS capacitors, low interface quality causes some defects which can be examined under two headings. One of which is the surface state such as border traps, mobile ionic charges and oxide trapped charges. The other is series resistance. Due to the surface states and the series resistance defects, the electrical characteristics of MOS capacitor deviate from ideal behaviours [11, 12].

In this study, our aim is to investigate the frequency dependent electrical characteristics of Al/HfSiO4/p-Si (MOS) capacitors, especially focussing on oxide–semiconductor interface effect, i.e., interface states, border states and series resistance effects. In addition, the possible uses of HfSiO4 as a dielectric layer in MOS based technology were discussed from the obtained results. To do this, the electrical characterizations were investigated in the frequency range of 50 kHz to 1 MHz by the capacitance–voltage (C–V) and conductance–voltage (G/ω–V) measurements at room temperature. The measured capacitance and conductance were corrected in order to eliminate series resistance effects and find the real MOS capacitance. Using the corrected Gc/ω–V and Cc–V characteristics, the real interface state density (Dit) for each frequency was calculated. In addition, the capacitance hysteresis were measured and also corrected to examine borders state (Nbt) effects under applied voltage frequencies. Moreover, the doping concentration (NA), Fermi energy level (EF), diffusion potential (Vd), and barrier height (ΦB) as a function of frequency were obtained by corrected C −2c –V plots.

2 Experimental details

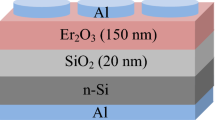

In order to fabricate the HfSiO4 thin film, silicon wafer which is 500 μm thick, p-type < 100 > Si substrate with a resistivity of 1–4 Ω was cleaned by the standard Radio Corporation of America (RCA) cleaning process firstly. In RCA cleanning process, silicon wafers were cleaned in 6:1:1 deionized (DI) water–H2O2–HNO3 for 5 min to get rid of organic residue and then to remove ionic residue silicon wafers were cleaned in a mix of 5:1:1 DI water–H2O2–HCL solution for 5 min. In order to eliminate naturel oxides in Si surface, the wafers were cleaned in 100:1 DI water–HF solution for 30 s and the cleaning wafers were dried by pure N2 gas lastly. Immediately after surface cleaning, a wafer was loaded in the chamber of the sputter system for HfSiO4 deposition onto Si layer. HfSiO4 target with dimensions of 4-inch and purity of 99.99 %, was used for the deposition of the oxide layers. The base pressure of the sputter chamber was adjusted below 4.0 × 10−4 Pa. Then, Ar flow rate was adjusted to be 16 sccm and sputtering pressure was adjusted to be at 1.0 Pa, then the pre-sputtering were performed for 3 h in order to get rid of any impurities on the target surface at 300 W and commercial sputtering was performed following the pre-sputtering in same parameters for 30 min. After deposition of HfSiO4, the HfSiO4/p-Si films were annealed at 750 °C for 40 min in the Nitrogen ambient and the thickness of the film was measured by spectroscopic reflectometer found as 300 nm. After annealing of the films, high-purity aluminum (Al) metal (99.999 %) was deposited by sputtering onto the whole back surface of the wafer and then Schottky contact was also formed by sputtering of Al dots with diameter of about 1.5 mm. The capacitance–voltage (C–V) and conductance–voltage (G/ω–V) measurements for fabricated Al/HfSiO4/p-Si (MOS) capacitor were performed at different frequencies of 50, 100, 250, 500 750 kHz and 1 MHz at room temperature using an Impedance Analyzer (MODEL HIOKI 3532-50 LCR meter) to study electrical characteristics of fabricated MOS capacitors.

3 Results and discussion

The capacitance voltage (C–V) and conductance voltage (G/ω–V) measurements were performed for each frequency between 50 kHz and 1 MHz at room temperature to study electrical instability and possible usage of HfSiO4 in MOS based technology. The measured C–V characteristics curves of Al/HfSiO4/p-Si (MOS) capacitors at different frequencies are shown in Fig. 1. Each C–V curves shows three regimes of accumulation–depletion–inversion region. It is observed that each C–V curves is a function of frequency and bias voltage. Especially, the flat band voltages (Vfb) are sensitive to the applied voltage frequency and it shifted to higher values than ideal one (−0.55 V) constantly by decreasing the frequency. This behaviour can be attributed to the frequency dependent interface states and border traps localized close to the interface between HfSiO4/Si that exchange mobile carriers with Si [13]. The contribution of these two trap state effects on flat band contribution will be discussed in details further. In addition, as seen in Fig. 1, the capacitance decreases with increasing frequency. This behaviour may be caused by time depended surface states and interface state. The variation in measured capacitance could be explained by the equivalent capacitance circuit [14, 15] observed in Fig. 2.

At the lower frequencies (<500 kHz) the effective capacitance CLF is expressed as

where Cox, Csc, are the oxide capacitance, space charge capacitance, respectively, while Cit is capacitance associated with the interface traps, ω (ω = 2πf) is angular frequency. Interface trap lifetime (τ), which is on the order of 10−6–10−7 s in the literature, is defined as product of Cit and Rit where Rit is resistance associated with the interface traps. The ωτ is very small at lower frequency, i.e., (ωτ)2 can be ignored in the Eq. 1 [16, 17]. This means that if interface trapped charges and defects are easily follow the applied voltage, it leads to yield an excess capacitance at lower frequencies. On the other hand, interface states do not contributed to the total capacitance at the high frequencies (500 kHz>) [15, 18] since interface states are not fast enough to rearrange in response to the applied voltage excitation provided that ωτ > 1. The effective capacitance represented by CHF is expressed by the following expression.

Considering the interface states contribution to the MOS capacitor characteristic, the C–V curves at all frequencies show three separated regimes, which are called inversion, depletion and accumulation as ideal MOS capacitors. In addition to these, C–V curves do not show kinks measured capacitance at all frequencies. The meaning of this is to highlight that there is a low defect and a good interface between HfSiO4 and p-Si [17, 19, 20]. Moreover, it can be seen in Fig. 1 that each C–V curves shifted to right side with increasing voltage frequency. The variation in C–V curves may be caused by the frequency dependent surface state. The interface states and series resistance are examples of the frequency dependent surface states.

The conductance is a significant parameter to investigate interface quality of the fabricated MOS capacitor [21]. When a small AC signal is applied to MOS capacitor, the conductance caused by interaction between interface states and majority carrier densities in the silicon losses [17]. Hence, it is direct measure of interface states and mobile carriers of Si. Interface traps somewhere near the band edge may be easily intercept and release carriers under different gate voltage influencing the charge and field distribution caused by different curves ideal behaviour of MOS capacitor. Frequency dependent measured conductance is shown in Fig. 3. The measured conductance curves increase with increasing applied voltage frequencies, except at 50 kHz. In addition, measured G/ω–V curves peaks move toward higher voltages with decreasing frequency. This behaviour may be related to relaxation time of trap states, series resistance and interfacial dielectric layer [21].

The series resistance corrections were performed to MOS capacitor characteristics in order to eliminate possible noise effects on the MOS capacitor characteristics. The measured admittance Yma at strong accumulation of the MOS structure using the parallel RC circuit, is equal to the total circuit admittance [22, 23].

where ω is angular frequency, Cma is measured capacitance and Gma measured conductance in strong accumulation region. Comparing the real and imaginary part of the impedance, the series resistance is given by the following equation [24].

The Rs values of the Al/HfSiO4/p-Si (MOS) capacitor were calculated and are tabulated in Table 1. It is observed that the series resistance values decrease with increasing applied frequency. These behaviours may be explained by re-contraction and re-ordering of defect sites under frequency dispersion [14, 20, 25]. In order to remove series resistance effect from the G–V, G/ω–V curves, the correction of capacitance and conductance characteristic can be calculated by the following equations;

and

where ω is angular frequency, Cm is measured capacitance and Gm measured conductance measured voltage range, a = (G m ) − [(G m )2 + (ωC m )2]R s . The comparison of the measured and corrected MOS capacitor characteristics, corrected capacitance and conductance curves are shown in Fig. 4a–d. As seen in Figs. 4a, c, the series resistance deviates from the MOS capacitor characteristics, especially, for high frequency measurements. On the other hand, the corrected capacitance did significantly not deviated from the originals. The corrected conductance deviated from originals ones. The measured conductance curves almost increase with increasing frequency while they decrease constantly after correction was performed. This behaviour is expected as indicated in the literature [20, 26, 27]. The observed results indicate that series resistance is an important parameter that is the masking real MOS capacitor characteristics and elimination should be performed before detailed electrical analysis.

Density state of interface state (Dit), which is the most important parameter affecting C–V characteristics, can be found using following equation [28].

where q is elementary charge, A is front area of MOS capacitor, Cox (Aε0εi/d) is the oxide capacitance whose value is 1.04 × 10−9 F, ε0 (=8.85 × 10−14 F/cm) is the permittivity of free space [29], Gc,max/ω is peak value of corrected Gc,max/ω–V curve, Cc is corrected capacitance of the MOS corresponding to Gc,max/ω. Some required values and calculated density of state values are given in Table 1. Frequency dependent interface state density under frequency dispersion is also depicted in Fig. 5. The Dit values decrease with increasing applied voltage frequency as expected [30, 31] and the order of Dit approximately was calculated as 1010 eV−1 cm−2. The calculated values are in the same order as other promising dielectrics reported in [20, 32–34].

Since the Dit values are in the expected order, the abnormal changes of the Vfb under frequency dispersions probably were caused by border states. In order to calculate border state density, the capacitance hysteresis were measured and then corrected. The corrected capacitance hysteresis curve is shown in Fig. 6 for 1 MHz and 50 kHz. Using the hysteresis curve obtained from flat band voltage shift (ΔVfb), the border state density (Nbt) in oxide layers were calculated by Eq. 8, assuming the total contribution interface states are almost zero for flat band shift in hysteresis [35, 36], and border state densitises Nbt, is given by

where Cacc is accumulation capacitance. The calculated Nbt are given in Table 1. The usual Nbt values are in the order of 1010 eV−1 cm−2 for real MOS capacitor. However, calculated Nbt is in the order of 1011 eV−1 cm−2 for fabricated Al/HfSiO4/p-Si (MOS) capacitor. Hence, the abnormal frequency variations on the flat band voltages of the MOS capacitors can be attributed to the frequency dependent border states. In addition, the observed hysteresis is in the counter clockwise direction which clearly reveals a larger reduction of the acceptor-like border traps. Thus, the donor-like border traps play the dominant role [37, 38].

The intercept of \({\text{C}}_{\text{c}}^{ - 2 }\) versus \({\text{V}}\) is plotted in Fig. 7. It has been observed that linearity of the obtained \({\text{C}}_{\text{c}}^{ - 2 } - {\text{V}}\) curves indicates the uniform distribution of interface states in the MOS capacitor structure. The relation between \({\text{C}}_{\text{c}}^{ - 2 }\) and \({\text{V}}\) can be expressed as in the following equation [39, 40].

where \({\text{V}}_{0}^{ }\) is the applied voltage and \({\text{V}}_{0}^{ }\) (=VD − kT/q) is the intercept of the \({\text{C}}_{\text{c}}^{ - 2 }\) versus \({\text{V}}\) plot with the voltage axis at various frequencies from 50 kHz to 1 MHz, ɛ s is relative permittivity of Si, ɛ 0 is the permittivity of free space and \({\text{N}}_{a}^{ }\) is the doping concentration obtained from the slope of \({\text{C}}_{\text{c}}^{ - 2 }\) versus \({\text{V}}\) characteristics. The values of barrier potentials (ΦB) can be obtained by means of the following equation [41].

where Ef (kT/q) ln(Nv/Na) is the energy difference between the bulk Fermi level and valance band edge, Nv is the effective density of state in valance band, C2 is the rate of Na (experimental)/Na (Theoretical) [42]. Theoretical value of Na is 1.67 × 1016 cm−3. Barrier potential, Δϕ B , can be calculated from the following equation.

where \({\text{E}}_{\text{m}}^{ }\) is the maximum electric field. These calculated electrical characteristic are tabulated in Table 2. Diffusion potentials are located at the positive voltage since the negative charges are trapped in the MOS capacitor by virtue of the fabrication process. Moreover, doping concentration increase with the increasing applied voltage frequency because of decline in the slope of \({\text{C}}_{\text{c}}^{ - 2 }\) versus \({\text{V}}\) plot. As data in Table 2 show, the Ef is almost constant as excepted under frequency dispersion. Moreover, variations on \({\text{V}}_{\text{D}}^{ }\) and Δϕ B were also observed under applied voltage frequency dispersion. This may be related to existence of the interfacial layer HfSiO4, especially, time dependent interface state at the HfSiO4/Si interface. On the other hand, the ΦB values varied from 0.615 to 0.559 eV depending on the charge accumulations due to time dependent trap sites.

4 Conclusion

In summary, the detailed electrical characteristics of Al/HfSiO4/p-Si MOS capacitor have been investigated for different voltage frequency at the room temperature. According to the results of the study, the capacitance and conductance are sensitive to applied voltage frequency due to frequency dependent charges, e.g., interface states, border traps, and series resistance. Seri resistance decreases with increasing applied voltage frequency and the seri resistance corrections must have been performed before detailed electrical analysis to obtain accurate results. The calculated Dit values were found to be in the order of 1010 eV−1 cm−2, which is in good agreement with other reported dielectric layer for MOS based technology. In addition, high sensitivity of the Vfb voltage variations was attributed to the interface states, especially, time dependent border states. On the other hand, it is observed that barrier potential values are also sensitive to the applied voltage frequencies. However, its values are expectable for elimination of leak charge injection from the substrate into the dielectric and thus the tunnelling effect does not significantly occur. In conclusion, fabricated HfSiO4 dielectric layer exhibits demanding electrical characteristics to be used in MOS-based technologies.

References

M. Vishwas, K.N. Rao, K.V.A. Gowda, R.P.S. Chakradhar, Spectrochim. Acta A 95, 423–426 (2012)

S. Kaya, A. Aktag, E. Yilmaz, Nucl. Instrum. Methods B 319, 44–47 (2014)

A. Kaya, S. Alialy, S. Demirezen, M. Balbasi, S.A. Yeriskin, A. Aytimur, Ceram. Int. 42, 3322–3329 (2016)

A. Haran, M. Murat, J. Barak, IEEE Trans. Nucl. Sci. 55, 2098–2105 (2008)

F. Parlakturk, S. Altindal, A. Tataroglu, M. Parlak, A. Agasiev, Microelectron. Eng. 85, 81–88 (2008)

J.A. Felix, D.M. Fleetwood, R.D. Schrimpf, J.G. Hong, G. Lucovsky, J.R. Schwank, M.R. Shaneyfelt, IEEE Trans. Nucl. Sci. 49, 3191–3196 (2002)

H.N. Raval, D.S. Sutar, V.R. Rao, Org. Electron. 14, 1281–1290 (2013)

J. Mekki, M. Brugger, S. Danzeca, L. Dusseau, K. Roed, G. Spiezia, IEEE Trans. Nucl. Sci. 60, 2435–2443 (2013)

M. Meguellati, F. Djeffal, Nucl. Instrum. Methods A 683, 24–28 (2012)

H. Tang, Y. Wang, J.Y. Wang, Y.J. Zheng, Y.F. Jin, ECS Trans. 27, 1159–1163 (2010)

V.A. Rozhkov, A.Y. Trusova, I.G. Berezhnoy, Thin Solid Films 325, 151–155 (1998)

S. Demirezen, A. Kaya, S.A. Yerişkin, M. Balbaşı, İ. Uslu, Results Phys. 6, 180–185 (2016)

D.M. Fleetwood, IEEE Trans. Nucl. Sci. 43, 779–786 (1996)

S. Kaya, R. Lok, A. Aktag, J. Seidel, E. Yilmaz, J. Alloy. Compd. 583, 476–480 (2014)

Y. Kimoto, Y. Satoh, H. Tachihara, Acta Astronaut. 65, 1446–1449 (2009)

H. Gong, J. Li, G.H. Gong, Y.X. Li, L. Hou, B.B. Shao, Chin. Phys. C 33, 774–776 (2009)

A. Kahraman, E. Yilmaz, S. Kaya, A. Aktag, J. Mater. Sci Mater. Electron. 26, 8277–8284 (2015)

L. de Carlan, R. Price, J.L. Chartier, I. Kodeli, B. Siebert, J. Henninger, J. Posselt, G. Gualdrini, S. Agosteo, R. Bedogni, J.M. Bordy, P. Cassette, P. Ferrari, J.M. Gomez Ros, B. Grosswendt, V. Lacoste, A. Pola, S. Rollet, F. Schultz, S.P. Simakov, R. Tanner, M. Terrissol, M. Zankl, Radiat. Prot. Dosim. 131, 15–23 (2008)

I. Mandic, V. Cindro, A. Gorisek, G. Kramberger, M. Mikuz, IEEE Trans. Nucl. Sci. 54, 1143–1150 (2007)

S. Kaya, E. Yilmaz, IEEE Trans. Electron. Dev. 62, 980–987 (2015)

F. Ravotti, M. Glaser, A.B. Rosenfeld, M.L.E. Lerch, A.G. Holmes-Siedle, G. Sarrabayrouse, IEEE Trans. Nucl. Sci. 54, 1170–1177 (2007)

H. Gong, J. Li, S.M. Yang, B.B. Shao, G.H. Gong, Y.X. Li, X.X. Xie, High Energ. Phys. Nucl. 31, 283–287 (2007)

E.H. Nicollian, J.R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology, 1st edn. (Wiley, New York, 1982)

S. Kaya, E. Yilmaz, H. Karacali, A.O. Cetinkaya, A. Aktag, Mater. Sci. Semicond. Process. 33, 42–48 (2015)

J. Lipovetzky, E. Redin, M. Maestri, M.G. Inza, A. Faigon, in Radecs 2007: Proceedings of the 9th European Conference on Radiation and Its Effects on Components and Systems, (2007), pp. 342–349

A. Tataroglu, S. Altindal, Microelectron. Eng. 85, 1866–1871 (2008)

H. Xiao, S.H. Huang, Mater. Sci. Semicond. Process. 13, 395–399 (2010)

A.M. Mahajan, A.G. Khairnar, B.J. Thibeault, Semiconductors 48, 497–500 (2014)

S.A. Yeriskin, M. Balbasi, A. Tataroglu, J. Appl. Polym. Sci. 133, 43827 (2016)

A. Jaksic, Y. Kimoto, A. Mohammadzadeh, W. Hajdas, IEEE Trans. Nucl. Sci. 53, 2004–2007 (2006)

A. Haran, M. Murat, J. Barak, D. David, in Radecs 2007: Proceedings of the 9th European Conference on Radiation and Its Effects on Components and Systems, (2007), pp. 274–279

P.M. Tirmali, A.G. Khairnar, B.N. Joshi, A.M. Mahajan, Solid State Electron. 62, 44–47 (2011)

D. Panda, T.Y. Tseng, Thin Solid Films 531, 1–20 (2013)

M. Shahjahan, N. Takahashi, K. Sawada, M. Ishida, Jpn. J. Appl. Phys. 41, L1474–L1477 (2002)

N. Nedev, E. Manolov, D. Nesheva, K. Krezhov, R. Nedev, M. Curiel, B. Valdez, A. Mladenov, Z. Levi, Sens. Lett. 10, 833–837 (2012)

E. Verrelli, G. Galanopoulos, I. Zouboulis, D. Tsoukalas, Thin Solid Films 518, 5579–5584 (2010)

D. Makowski, M. Grecki, B. Mukherjee, S. Simrock, A. Napieralski, P. Soc. Photo Opt. Ins. 6347, E3470 (2006)

T.M. Briere, A.S. Beddar, M.T. Gillin, Med. Phys. 32, 3346–3349 (2005)

S. Zeyrek, A. Turan, M.M. Bulbul, Chin. Phys. Lett. 30, 077306 (2013)

A. Jaksic, K. Rodgers, C. Gallagher, P.J. Hughes, Int. Conf. Microelectron. 1, 577–579 (2006)

S. Altindal, F. Parlakturk, A. Tataroglu, M. Parlak, S.N. Sarmasov, A.A. Agasiev, Vacuum 82, 1246–1250 (2008)

S. Demirezen, Z. Sonmez, U. Aydemir, S. Altindal, Curr. Appl. Phys. 12, 266–272 (2012)

Acknowledgments

This work is supported by Ministry of Development of Turkey under Contract Numbers: 2012K120360, 2016K121110 and Abant Izzet Baysal University under Contract Numbers: AIBU, BAP. 2014.03.02.722 and 2014.03.02.764.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lok, R., Kaya, S., Karacali, H. et al. A detailed study on the frequency-dependent electrical characteristics of Al/HfSiO4/p-Si MOS capacitors. J Mater Sci: Mater Electron 27, 13154–13160 (2016). https://doi.org/10.1007/s10854-016-5461-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-016-5461-x