Abstract

In this paper, a new capacitance-to-frequency converter using a charge-based capacitance measurement (CBCM) circuit is proposed for on-chip capacitance measurement and calibration. As compared to conventional capacitor measurement circuits, the proposed technique is able to represent the capacitance in term of the frequency so that the variations can be easily handled in measurement or calibration circuits. Due to its simplicity, the proposed technique is able to achieve high accuracy and flexibility with small silicon area. Designed using standard 180 nm CMOS technology, the core circuit occupies less than 50 μm × 50 μm while consuming less than 60 μW at an input frequency of 10 MHz. Post-layout simulation shows that the circuit exhibits less than 3 % measurement errors for fF to pF capacitances while the functionality has been significantly improved.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The process variations have always been one of the key issues in the robustness of CMOS integrated circuits especially in the mixed signal and RF circuits. For example, the variations of CMOS capacitances can be as large as 20 %. In the applications which heavily depend on capacitances accuracy, such as LC tank based voltage-controlled oscillator, the errors may introduce variations of operating frequency larger than 10 %, which is almost the tuning range of the oscillator in practice. Similar scenarios exist in the analogue-to-digital converters with high resolution, where well-matched capacitances are highly desired. Processing monitoring and calibration is hence of great interest to both microelectronics manufacturing and circuit designing [1–4]. The ring oscillator is a popular solution to track process variations, e.g., capacitance, in terms of frequency changes [4]. However, itself is very sensitive to many other variations, such as device sizes, supply voltage and temperature, etc.

It is not easy to extract the exact capacitance variations using a single kind of topology. To solve this issue, a new simple capacitance-to-frequency converter is proposed in this letter. It is able to transform the variations of capacitances in term of frequency changes with a considerably high accuracy, while maintaining a small silicon area and high flexibility in CMOS technology.

2 Design Considerations

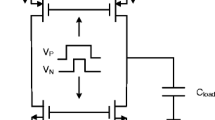

The measurement of capacitance is an essential task in process characterisation. The CBCM technique has been a promising solution to measure on-chip capacitance for its high accuracy up to fF level. Figure 1 shows the topology of CBCM technique. Two non-overlap signals, Vp and Vn are applied to two inverters with and without load capacitors.

By comparing the current difference between the two inverters (with or without capacitor under measure), the load capacitance can be determined as:

where f clk is the frequency of the square wave Vp and Vn.

However, this technique requires current meter in the measurement. Hence it is not suitable for on-chip calibration. Actually, the requirement for the on-chip capacitance variations measurement is quite different from conventional capacitance measurement. In such applications, no external current meter is available. However, only the variation of capacitance is required. For example, the percentage of variations over a reference capacitor is enough for the calibration of circuit performance. The simplest way to achieve this functionality is to use a ring oscillator to track the process variations. However, the oscillating frequency is highly dependent on other parameters, such as supply voltage, process corners of the transistors. Also, the operating frequency of the oscillator is never linear to the load capacitances due to non-linear effects of the circuits. These make the solution less attractive in the application of on-chip capacitance calibration.

It is observed that if the current difference in Eq. (1) can be replaced with some parameter that is easier to handle on-chip, such as frequency or period, the calibration of variations is possible. By combining the two above-mentioned solutions, a simple way for the capacitance variation monitoring can be performed in the following steps. By using the CBCM technique, the capacitance is calculated from the difference between the current of the two inverters. Then the current difference can be transformed into charge difference in reference capacitances, which subsequently results in the periodic difference in charging and discharging. Eventually, the capacitance is represented by differences in frequencies.

3 Proposed Design

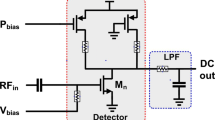

A circuit can then be designed based on this idea. Figure 2 shows the topology of the proposed capacitor-to-frequency converter. In the capacitance measurement or calibration, each converter is loaded with different capacitances, and the differences in capacitance can be represented with different output period at Vout.

Compared with CBCM circuit in Fig. 1, by adding a tail MOS transistor MN3, the current of the inverter is transformed into voltage. Then switches MP3 and MN4 are added to control the charge over capacitor Ccharge. A comparator is used to compare the voltage at this capacitor with a threshold voltage Vref. The operation of the circuit is described as follows. Initially, Vctrl is low, the capacitor is being charged until the voltage of the capacitor, Vc increase to Vref. The output of the comparator, Vout will consequently be logical high when Vc reaches Vref. Vout is delayed as Vctrl to control the switches which constitutes a feedback loop. In the delay time, Vctrl keeps low and the capacitor keeps charging. When Vctrl becomes high, the capacitor will be discharged immediately. Then the output of the comparator Vout and the output of the delay circuit Vctrl will be low again, the circuit will come to the next period. Finally, the capacitor Ccharge is charged and discharged to perform a periodical operation. Hence, the charging time, T is transformed to frequency, f out. The current of the charging branch can be determined as:

This relationship can be used to calculate or calibrate the capacitances. For example, two capacitors C1 and C2 are measured using two capacitance-to-frequency converters in Fig. 2. According to Eq. (2), we can get:

And the current difference ΔI is linear to ΔIc:

Here, the coefficient α represents a linear relationship between ΔI and ΔIc. It is a constant when the circuit parameters are all determined. Therefore

So by comparing the difference in period for the charging and discharging time among C1 and C2, the capacitance difference is now the time (or frequency) difference. The coefficient α in Eq. (4) varies with f clk, Ccharge, Vref and device sizes of MP2, MN2, MN3. It can be optimized to achieve high accuracy at desired range of measurement. Firstly, f clk and component MP2, MN2, MN3 determine the current consumption of the inverter. If the current consumption is too small, the Vc could not reach Vref, leading to the failure of the circuit. However, large current consumption leads to poor linearity. Secondly, Vref and Ccharge should be properly sized according to the range of capacitance under measure. Finally, the delay time is determined based on the discharged time of Ccharge. It is important to make sure Ccharge can be discharged to zero within the delay time.

4 Simulation Results

In the applications of mixed-signal and RF CMOS IC design, the typical capacitance is fF to pF. Hence the circuit in this work is optimized at such ranges. The circuit is implemented using a standard CMOS process. Only standard CMOS devices such as MOS transistors and capacitance are used in the circuit. It is optimized to measure fF to pF capacitance. For example, when Vdd = 1.8 V, f clk = 10 MHz, C1 = 302.5fF, C2 = 1058.5fF, Vref = 0.7 V, the delay time is 2us, the simulated Vout of the circuits with the two load capacitors are shown in Fig. 3. In this scenario, the circuit except the capacitance is less than 50 μm × 50 μm and consumes less than 60 μW.

In Fig. 3, Vout1 and Vout2 exhibit obvious differences in phase and frequency. Based on this difference, the calibration can be performed on-chip using digital technique. Also, if the capacitance is measured, the proposed circuit can be used to calculate the capacitance like a conventional CBCM technique. In CBCM technique, the capacitance is calculated using current difference, while the frequency difference is used in the proposed circuit. According to the frequency of Vout1 and Vout2, f out1 and f out2, we can get different charging time T1 and T2. Using Eq. (3), the current difference ΔIc can be calculated. Here we can get the linear relationship of ΔIc and ΔI:

We can compare with the conventional CBCM technique, here the measurement error of this circuit is 0.53 %. According to the range of capacitance under measure, we can modify f clk, Ccharge, Vref and device sizes of MP2, MN2, MN3 to obtain good linearity.

Several design considerations can be concluded as follows. The frequency of the clock signal and Ccharge should be determined based on the considerations of operating speed and linearity of measurement results and the suitable range of the capacitance of CDUT. As mentioned above, the increase of f clk results in the increase of charging current I and consequently the decrease of the charging period of Ccharge, which is preferred to the circuit speed. However, with high input frequency, f clk and large capacitance, the measurement results of CDUT exhibits a poor linearity. Therefore, f clk and Ccharge should be determined according to the range of capacitance under measure. For example, when the capacitance is around 10fF, we can increase f clk to 100 MHz, which can be decreased to 5 MHz if the capacitance under measure is around 1 pF. The minimum reference frequency can be as low as 1 MHz if a lower speed operation is acceptable. Besides, the capacitance of Ccharge can be set to 20 pF to keep a proper charging time difference. As for the design of comparator, the voltage reference and voltage offset should be considered based on the requirement of accuracy. In this design, Vref is set to be 0.7 V considering the charging time of Ccharge as well as the topology of the comparator. Since the accuracy of CDUT is directly limited by the offsets of the comparator. In this work, simulations are carried out to ensure the robustness of this design. For example, we can manually add 5 mV offset voltage in the comparator, which is a typical value of offset in this kind of topology. The accuracy degrades by 0.7 %, which is quite acceptable in the proposed system. However, if the offset is increased to 15 mV, the accuracy can be degraded by more than 3 %, which is not acceptable. This ensures the proper operation of proposed system. As long as desired measurement range is determined, the circuit can be further optimized for smaller silicon area and higher accuracy. Post-layout simulations with process corners are performed to verify the functionality of the proposed circuit at a wide working range. The percentage of error in the circuits is summarized in Fig. 4. It is observed that the proposed circuit is able to provide a high accuracy (less than 2 % error) from fF to pF ranges.

Besides, according Eqs. (1)(3)(4), we can get:

where T1 and T2 can be directly calculated from f out1 and f out2. Define the time reciprocal difference as delayed frequency difference (DFD). The linear relationship between this delayed frequency difference and capacitance under measure is also shown in Fig. 4. It is observed that the unified DFD exhibit a linear relationship with the capacitance under measure from fF to pF ranges. It suggests that the measurement or calibration can be performed on-chip precisely.

5 Conclusion

A capacitance-to-frequency converter is proposed. It can be used to measure the on-chip capacitance up to 1fF accuracy in term of output frequency measurement. More importantly, it is able to perform on-chip digital calibration regarding capacitance variations. The circuit is designed and simulated using a standard 180 nm CMOS technology, the core circuit occupies less than 50 μm × 50 μm and the building blocks of the circuits are standard CMOS circuits which can be easily configured for use at different operating frequencies, capacitance under measurement, and accuracy as well as for different CMOS technology nodes.

References

Chang YW, Chang HW, Lu CY, King YC, Ting W, Ku YH (2006) Interconnect capacitance characterization using charge-injection-induced error-free (CIEF) charge-based capacitance measurement (CBCM). IEEE Trans Semicond Manuf 19(1):50–56

Peng YX, Qian TR, Lin XW, Zheng S (2015) A New On-chip Signal Generator for Charge-Based Capacitance Measurement Circuit. J Electron Test 31(31):329–333

Sylvester D, Chen JC, Hu C (1998) Investigation of interconnect capacitance characterization using charge-based capacitance measurement (CBCM) technique and three-dimensional simulation. IEEE J Solid State Circuits 33(3):449–453

Welter L, Dreux P, Aziza H, Portal J-M (2015) Embedded high-precision capacitor measurement system based on ring-oscillator. Electron Lett 6(51):521–523

Acknowledgments

This work was supported by the National Natural Science Foundation of China under Grant 61401395, and the Scientific Research Fund of Zhejiang Provincial Education Department under Grant Y201533913.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: V. D. Agrawal

Rights and permissions

About this article

Cite this article

Zhu, D., Mo, J., Xu, S. et al. A New Capacitance-to-Frequency Converter for On-Chip Capacitance Measurement and Calibration in CMOS Technology. J Electron Test 32, 393–397 (2016). https://doi.org/10.1007/s10836-016-5584-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-016-5584-2