Abstract

A strained Ge1−x−ySixSny/Ge1−a−bSiaSnb direct type II staggered heterojunction n-channel tunneling field-effect transistor (FET) with a dual-material double gate is proposed herein. A high-K gate dielectric is used to improve the overall device performance. The energy bandgap for strained Ge1−x−ySixSny grown on a relaxed Ge1−a−bSiaSnb layer is determined using the generalized approach of Menendez and Kouvetakis (MK). Poisson’s equation is solved by using a parabolic approximation to determine the surface potential and electric field. The drain current is calculated using the tunneling generation rate obtained from Kane’s model. A significant improvement of the drain current is observed as compared with that of previously reported Si-based TFETs.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Aggressive downscaling of metal–oxide–semiconductor field-effect transistors (MOSFETs) to achieve higher packing densities and increased values of the ON-current ION leads to severe degradation of the device performance due to short-channel effects (SCEs) such as drain-induced barrier lowering (DIBL), leakage current, etc. [1]. The subthreshold swing of such devices is also restricted to 60 mV/decade at room temperature [2], which results in power dissipation problems when used in nanoscale circuits. To overcome such limitations, alternative devices with a reduced subthreshold swing must be explored to achieve higher ON-currents and reduced leakage currents for use in low-power applications [3,4,5].

The TFET uses band-to-band tunneling for carrier transport across the junctions instead of the conventional drift–diffusion current mechanism in MOSFETs. This makes it suitable for use in low-power applications. The TFET device has a built-in tunnel barrier that prevents SCEs and helps to achieve subthreshold swing values below the 60 mv/decade threshold [5,6,7]. Also, there is scope to improve the overall device characteristics of TFETs by simultaneously optimizing the ION, IOFF, VT, subthreshold slope, nature of the output characteristic, and immunity against SCEs, especially DIBL effects [8].

However, TFETs also suffer from certain drawbacks such as low ION as compared with conventional MOSFETs and ambipolar issues when used in switching applications. Also, device reliability can be a major concern, as TFET devices suffer from degradation of the device performance in terms of the drain current and threshold voltage due to the presence of interface traps and oxide charges at the gate dielectric–channel interface near the source–channel region [9]. The performance of TFETs can be improved by improving their ION and overcoming the ambipolar issues, which can be achieved by structural or material engineering of the device architecture. Recently, several structural modifications have been observed to address the shortcomings of the conventional TFET. A gate–source overlap with the addition of an Esaki tunneling diode in the source region of a TFET device is seen to improve the ION/IOFF ratio and reduce the ambipolarity and leakage current [10]. The performance of conventional TFETs is seen to be greatly improved by modifying the channel shape (e.g., by using a T-shaped channel) and the positioning of the drain [11]. The scaling limitations of TFET devices (due to the emergence of SCEs) can be overcome by introducing a ground plane into the buried oxide of silicon-on-insulator (SOI) TFETs [12]. The addition of a source pocket at the source–channel interface greatly improves the ON current [13]. The use of heterojunctions in junctionless TFETs can improve the overall device performance and allow their use in digital applications [14]. The strained double-gate TFET (DGTFET) using dual-material and high-K dielectric has also shown encouraging results [15,16,17]. The use of a narrower-bandgap material also greatly improves the ION [19].

Dramatic improvements have been achieved in this field over the last 10–15 years, including the successful growth of GeSn [20] and the discovery of practical chemical vapor deposition (CVD) routes to high-quality Ge1−xSnx films and alloys of GeSiSn directly on Si substrates [21,22,23,24,25].

An interesting feature of this alloy is the crossover observed from an indirect to direct bandgap when the Sn concentration in the alloy exceeds 8% [26,27,28]. A material with a direct nature can also be obtained by applying strain. All the layers and virtual substrates (VS) can be grown on a Si substrate, highlighting the possibility of integrating the electronics and photonics onto a Si platform. It has also been proved that a type II direct bandgap configuration can be realized by using a strained GeSiSn layer with Sn content below 25% [29]. This type II direct bandgap can lead to significant band-to-band tunneling (BTBT) even at low voltages. Also, heterojunctions with such type II staggered band alignment have been shown to boost the performance [30, 31] of TFETs based on GeSiSn alloy.

Material engineering using new and novel materials must be combined with structural engineering to obtain devices with optimum performance. A heterojunction n-channel TFET built with a direct bandgap type II staggered strained Ge1−x−ySixSny/Ge1−abSiaSnb junction is proposed herein. The Ge1−x−ySixSny layer is strained, whereas the Ge1−a−bSiaSnb layer is relaxed. The method used to calculate the energy bands is a generalization of Van de Walle’s approach along with the inclusion of the strain-dependent spin–orbit Hamiltonian [25]. An analytical model for the above-mentioned device is derived by solving the two-dimensional (2-D) Poisson equation using the parabolic approximation technique. The surface potential and electric field are thus obtained using appropriate boundary conditions. The drain current is also obtained using the generation rate derived from Kane’s band-to-band tunneling generation rate model [32,33,34].

2 Theory

2.1 Device structure

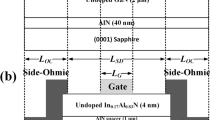

A schematic of the structure of the proposed device is shown in Fig. 1. The p-type source and n-type drain are considered to have doping concentrations of 1020/cm3 and 5 × 1018/cm3, respectively. The use of a lower doping concentration on the drain side ensures a lower OFF-current, while the higher source doping provides a higher ON-current due to the increased bandgap narrowing at the tunneling junction [18]. On the other hand, the channel doping concentration is chosen as 1017/cm3 to enhance the carrier mobility. Being an n-channel device, tunneling occurs at the source side of the source–channel interface. A high-K gate dielectric HfO2 (K = 25) is used to reduce the gate leakage. Two gate metals M1 and M2 have different work functions of 4 eV and 4.4 eV, respectively. Initially there is no band overlap on the source side, but with an increase of the gate voltage, carriers tunnel from the valence band of the heavily doped p-type source to the conduction band of the nearly intrinsic channel and then move towards the n-doped drain by the drift–diffusion mechanism.

2.2 Bandgap calculation

The energy band structure at the Γ and L points of the conduction band in the Ge1−x−ySixSny layer grown on Ge1−a−bSiaSnb is calculated using a generalization of the Menendez and Kouvetakis (MK) [25] approach. It is assumed that there is a reference level within each semiconductor and that this level lines up when a heterostructure is formed. This alignment process of the reference levels gives the offset ΔEV,av for the average of the three top valence bands in the actual materials. In the strain-dependent spin–orbit Hamiltonian introduced by Chandrasekhar and Pollak [37], the Menendez and Kouvetakis (MK) [25] and Van de Walle [38] approaches are also included. The expressions for the band edges of a (001)-oriented Ge1−x−ySixSny layer lattice-matched to a relaxed Ge1−a−bSiaSnb layer are given by

where Δ0 is the spin–orbit splitting. Here, EVΓ(x,y) is the highest valence band in the strained Ge1−x−ySixSny layer, and ECΓ(x,y) and ECL(x,y) are the conduction-band edge at the Γ and L point, respectively.

The shear components of the strain have a significant effect on the degenerate bands; they lead to splitting of the valence bands. The splitting of the energy subbands averages out to obtain EV,av. Even when no shear strain is present, valence-band splitting occurs due to the spin–orbit effect and the topmost valence band is given by \(E_{V} = E_{{{\text{V,av}}}} + \frac{{\Delta_{0} }}{3}.\).

When strained layers are grown on a substrate, the shear components of the strain lead to additional splitting of the bands, which interacts further with the spin–orbit splitting to produce the final valence-band position. This effect is reflected in the difference of the spin–orbit splitting of the layer \(\frac{{\Delta_{0} \left( {x,y} \right)}}{3}\) and the substrate \(\frac{{\Delta_{0} \left( {a,b} \right)}}{3}\) [29].

E0(x,y) is the direct bandgap of Ge1−x−ySixSnyat the Γ point and Eind(x,y) is the indirect Γ–L bandgap, given as

The indirect bandgap energy is calculated according to Vegard’s law by using the values of the bowing parameters presented in Table 1. The strain shifts \(\partial E_{001} ,\partial E_{001}^{\prime } ,\partial E_{\rm h}^{\rm V} ,\partial E_{\rm c}^{C\varGamma } \;{\text{and}}\;\partial E_{\rm C}^{\rm CL}\) are calculated from Menendez and Kouvetakis (MK) [25] and Chuang et al. [35]. The lattice constants of the ternary alloys are calculated using the following equation:

The lattice constant is used to calculate the strain as \(e_{\parallel } = \frac{{\left[ {a\left( {a,b} \right) - a\left( {x,y} \right)} \right]}}{{a\left( {x,y} \right)}}\) [25].

The lattice constants of Ge, Si, and Sn, the lattice bowing parameters, and the deformation potentials used to calculate the strain and strain shifts are presented in Table 1.

Using Eqs. (1)–(3), the various concentrations of Ge, Si, and Sn in the ternary alloy giving type II, direct, and staggered band alignment are obtained and presented in Table 2. We choose the composition which gives rise to type II band alignment [29]. This improves the band-to-band tunneling rate in the proposed device, as the tunneling barrier width is reduced, thereby improving the ON current as seen below. The mole fractions providing the optimum device performance are selected to obtain the desired results.

2.3 Calculation of the drain current

For the calculation of the drain current, the following assumptions are made:

-

The surface potential at the source end is equal to the difference between the Fermi level of the p-type source and the intrinsic Fermi level.

-

The potential drop in the depletion region of the source is negligible, and the potential in the source region is uniform.

-

The source–channel and drain–channel depletion regions are free from mobile charge.

-

Trap charges are taken as zero.

The analytical model for the proposed device structure is derived by solving the 2-D Poisson’s equation

The potential profile in the vertical direction is assumed to be a second-order polynomial [36]

The boundary conditions in the channel region are:

-

(a)

The electric flux at the front-oxide gate interface is continuous for the dual-material gate TFET, so

where \(\varphi_{\rm g1} = V_{\rm gs} - \phi_{\rm M1} + \chi + {\raise0.7ex\hbox{${E_{\rm g} }$} \!\mathord{\left/ {\vphantom {{E_{\rm g} } 2}}\right.\kern-0pt} \!\lower0.7ex\hbox{$2$}},\)

-

(b)

The electric flux at the back gate oxide and the back channel interface is continuous for both materials:

-

(c)

The potential at the source and drain end is given as

where Vbi is the built-in potential, ϕM1 and ϕM2 are the work functions of the gate metals, Eg is the bandgap energy, q is the elementary charge, VGS is the gate–source voltage, VDS is the drain–source voltage, εSi is the relative permittivity of GeSiSn, and εox is the relative permittivity of HfO2.

The 2-D potential under M1 and M2 can be obtained as

The values of the above constants are given as follows:

Thus, we get

Solving the Poisson’s equation, we obtain the surface potential under M1 and M2 as

Solving the above second-order differential equation yields

where \(p^{2} = \frac{{2\varepsilon_{\text{ox}} }}{{t_{\text{Si}} \varepsilon_{\text{Si}} t_{\text{ox}} }},\)

where χ is the electron affinity and p is the characteristic length.

The coefficients B1, C1, B2, and C2 are

Differentiating the surface potential along the channel length gives the electric field distribution.

The lateral electric field is

The vertical electric field is

The tunneling generation rate G(\(\Xi\)) is calculated from Kane’s model [32, 33] as

where \(\left|\Xi \right| = \sqrt {\Xi _{x}^{2} + \varXi_{y}^{2} }\) is the magnitude of the electric field and AKane and BKane are Kane’s parameters.

The value of Kane’s parameters, which are dependent on the reduced tunneling mass and bandgap, are taken as

In a DG-TFET, electrons undergo BTBT from the valence band of the source to the conduction band of the channel region. The total drain current ID per unit length can be obtained by integrating the band-to-band generation rate over the volume of the device [34]:

where q is the electronic charge.

3 Results and discussion

The proposed analytical model is implemented for a device with a channel length of 20 nm. The device has a body thickness of 10 nm and an equivalent oxide thickness (EOT) of ~ 1 nm.

Figure 2 shows the band alignment at the strained Ge1−x−ySixSny/Ge1−a−bSiaSnb interface.

The analytical model derived herein is first applied to an Si-based DG-TFET, and the results are compared with data previously reported by Garg et al. [39] by using the same parameter values as those of the Si-based DG-TFET studied by Garg et al. [39]. Figure 3 illustrates the transfer characteristic of the Si-based TFET. Good agreement is seen between the results obtained using the theoretical model described herein and the simulation results of Garg et al. [39]. The model is thus validated and is now implemented on the proposed device structure.

Figure 4 illustrates the variation of the surface potential along the channel length at different gate voltages with a constant drain–source voltage. The surface potential varies significantly with the gate–source voltage. There is a reduction in the surface potential in the channel region with increasing gate voltage. For a higher gate–source voltage, the slope of the surface potential is sharper, indicating a greater tunneling current on the source side.

Figure 5 illustrates the variation of the surface potential along the channel length for different drain voltages at a constant gate–source voltage. The surface potential at the source side remains unaffected by the drain voltage. Also, the slope of the potential profile is unaffected when increasing the drain bias. Therefore, the drain-induced barrier lowering (DIBL) effect will be significantly reduced and the tunneling current will remain shielded from the drain bias.

The variation of the lateral electric field \(\Xi\)x along the channel length at a constant drain voltage and constant gate voltage is shown in Fig. 6. The gradient of the field is high at the source and drain ends, but low in the middle of the channel. This gradient aids the diffusion of the carriers injected due to BTBT at the source junction to move to the drain end. The lateral electric field is crucial in calculating the tunneling generation rate.

Figure 7 plots the vertical electric field \(\Xi\)y along the channel length at a constant drain voltage and constant gate voltage. The vertical electric field is maximum at the source end, which is the tunneling junction, but low at the drain end. Therefore, the chance of vertical tunneling from the gate is higher near the source than the drain. Therefore, bandgap or material engineering at the source side can reduce the leakage current. Also, the total electric field is maximum at the source–channel interface, i.e., the tunneling junction. This depicts the local band bending of the energy band leading to the BTBT.

Figure 8 illustrates the output characteristics of the device at constant gate–source voltage. The drain current ID increases with the drain voltage, as desired.

Figure 9 shows the transfer characteristics of the device at constant drain–source voltage for different bandgaps taken from Table 2. An ON-current ION of ~ 25 mA/µm is achieved with an OFF-current of ~ 10−10 A/µm for a bandgap Eg of 0.4648 eV. The EOT of the proposed device is taken as ~ 1 nm. The OFF-current of the device varies when changing the bandgap of the heterostructure, while the ON-current shows very little change. It can thus be concluded that the device performance is dependent on the mole fraction values in the alloy and the tunneling barrier width is indirectly a function of the mole fraction values of the alloy. The application of the gate voltage reduces the tunneling gap, and a very high local electric field is created, which leads to tunneling. As the gate bias is increased, the tunneling current flows from the source to drain end in the lateral direction. The sharp potential profile strongly influences the tunneling current near the source–channel interface.

The variation of the transfer characteristics when changing the oxide thickness is illustrated in Fig. 10, which presents a comparative view of the ID versus VGS characteristics of an Si-based DG-TFET (EOT = 2 nm) and the proposed device for various values of tox. The ON-current increases with a decrease in the EOT. As tox decreases, the electric field increases, which in turn increases the tunneling probability. This increase in the band-to-band tunneling results in an increase of the ON-current of the device. It is observed that the proposed device offers a higher ON-current (~ 25 mA/µm) as compared with the Si-based DG-TFET (~ 2 µA/µm). The OFF-current of the proposed device is little affected when changing the EOT, showing a lower leakage current. A lower OFF-current is obtained for the Si-based DG-TFET. To overcome the disadvantage of the higher OFF-current, certain types of structural engineering can be incorporated, such as the addition of a drain pocket at the channel–drain interface. This not only reduces the OFF-current but also helps to eliminate the ambipolarity [39, 40]. The structure proposed herein overcomes the major disadvantage of the low ON-current of almost all types of TFET. The use of the SiGeSn heterostructure offers a great advance in this regard, and the proposed structure is clearly seen to provide a much higher ON-current than the Si-based DG-TFET when using comparable device parameters.

Figure 11 illustrates the variation of the ION/IOFF ratio over a range of EOT values for the proposed device structure. A smaller EOT values gives a higher ON-current, leading to a better ION/IOFF ratio and complements the device scaling. As the EOT of the device is increased, a degradation is seen in the ION/IOFF ratio. The incorporation of a high-K dielectric (HfO2) helps to obtain a lower EOT, thereby improving the overall performance of the device.

Figure 12 shows the variation of the ION/IOFF ratio when changing the channel length. At shorter channel lengths, the SCEs emerge, thereby reducing the ION/IOFF ratio. Around a channel length of 20 nm, there is a large increase in the ION/IOFF ratio, thus proving that this channel length can provide the optimum device characteristics while allowing device scaling. A ION/IOFF -ratio on the order ~ 107 is observed at the channel length of 20 nm.

Figure 13 depicts the SSavg of the proposed device structure versus the channel length. As the device dimensions are increased, a lower SSavg is obtained. For a shorter channel length, i.e., 10 nm, an SSavg value of 90 mV/dec is obtained. Meanwhile, at a channel length of 20 nm, an SSavg value of 36.5 mV/dec is obtained, being much lower than that obtained from conventional MOSFET and TFET devices.

Figure 14 illustrates the transfer characteristics of the proposed device at VDS = 0.1 V and 1 V. The DIBL is calculated as the ratio of the difference of the gate voltages at which the drain current is equal to the DIBL current of 10−9A/μm at different VDS values to the difference of the drain voltages [12]. The DIBL of the proposed device extracted from the graph is 44.4 mV/V, being much lower than for conventional TFETs (~ 121 mV/V) [12]. Thus, the DIBL is reduced by almost 63%.

Figure 15 illustrates the gate-induced drain leakage (GIDL) current of the device [41,42,43] obtained for different VGS values at fixed drain voltages. The GIDL current can be reduced by increasing the EOT and introducing structural engineering into the device, which eventually improves the overall device performance.

Table 3 presents a comparison of the various performance characteristics of the Si-based TFET and the proposed device structure. The advantages of the current structure are clearly observed in the context of the low ION/IOFF ratio of the proposed device, and it can be concluded that the source of this problem is the higher IOFF of the proposed device compared with the Si-based TFET. Further studies are necessary to address this problem, along with that of the ambipolarity. It can be conjectured that optimization of the device structure, and hence the nature of the strain in the material, could be employed for such work. Another important unresolved issue is related to the presence of interface trap states that may play a role, typically via the generation of hot electrons. However, at this point, there is little experimental data available on SiGeSn to reach any conclusion on this matter.

4 Conclusions

A strained Ge1−x−ySixSny/Ge1−a−bSiaSnb direct type II staggered heterojunction n-channel tunneling FET with a dual-material double gate is designed and an analytical model proposed for the same. Analytical expressions for the electric field and surface potential are derived. Using the electric field components, the tunneling generation rate is calculated and thus the drain current is obtained using Kane’s model. The two major disadvantages of the TFET include a low ON-current and ambipolarity, restricting use in low-power applications. The device proposed herein improves the ON-current drastically. It is thus concluded that the proposed GeSiSn-based TFET achieves better ON-current ID as compared with the Si-based DG-TFET.

References

Arun Samuel, T.S., Balamurugan, N.B.: An analytical modeling and simulation of dual material double gate tunnel field effect transistor for low power applications. J. Electr. Eng. Technol. 8, 742–748 (2013)

Taur, Y., Ning, T.H.: Fundamentals of modern VLSI devices. Cambridge University Press, Cambridge (1998)

Anvarifard, M.K., Ramezani, Z., Amiri, I.S., Nejad, A.M.: A nanoscale-modified band energy junctionless transistor with considerable progress on the electrical and frequency issue. Mater. Sci. Semicond Process 107, 104849 (2020)

Shoormasti, A.S., Orouji, A.A., Anvarifard, M.K.: Performance improvement of SiGe based silicon-on-insulator transistor using vertically graded channel approach. Silicon 11, 3021–3030 (2019)

Choi, W.Y., Park, B.-G., Lee, J.D., Liu, T.-J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007). https://doi.org/10.1109/LED.2007.901273

Gandhi, R., Chen, Z., Singh, N., Banerjee, K.: Vertical Si-Nanowire n-type tunneling FETs with low subthreshold swing (~ 50 mV/decade) at room temperature. IEEE Electron Device Lett. 32(4), 437–439 (2011). https://doi.org/10.1109/led.2011.2106757

Zhang, Qin, Zhao, Wei, Seabaugh, Alan: Low subthreshold-swing tunnel transistors. IEEE Electron Device Lett. 27(4), 297–300 (2006). https://doi.org/10.1109/LED.2006.871855

Pal, A., Sachid, A.B., Gossner, H., Rao, V.R.: Insights into the design and optimization of tunnel-FET devices and circuits. IEEE Trans. Electron Devices 58(4), 1045–1053 (2011)

Upasana, Narang, R., Saxena, M., Gupta, M.: “Modeling and TCAD assessment for gate material and gate dielectric engineered TFET architectures: circuit-level investigation for digital applications. IEEE Trans. Electron Devices 62(10), 3348–3356 (2015)

Anvarifard, M.K., Orouji, A.A.: Enhancement of a nanoscale novel Esaki tunneling diode source TFET (ETDS-TFET) for low-voltage operations. Silicon 11, 2547–2556 (2019)

Uddin Shaikh, M.R., Loan, S.A.: Drain-engineered TFET with fully suppressed ambipolarity for high-frequency application. IEEE Trans. Electron Devices 66(4), 1628–1634 (2019)

Garg, S., Saurabh, S.: Improving the scalability of SOI-based tunnel FETs using ground plane in buried oxide. J. Electron Devices Soc. IEEE 7, 435–443 (2019)

Lu, H., Lu, B., Zhang, Y., Zhang, Y., Lv, Z.: Drain current model for double gate tunnel-FETs with in As/Si heterojunction and source-pocket architecture. Nanomaterials 9, 181 (2019)

Ferhati, H., Djeffal, F., Bentrcia, T.: The role of the Ge mole fraction in improving the performance of a nanoscale junctionless tunneling FET: concept and scaling capability. Beilstein J Nanotechnol. 9, 1856–1862 (2018)

Boucart, K., Ionescu, A.M.: Double-gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

Saurabh, S., Jagadesh Kumar, M.: Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans. Electron Devices 58(2), 404–410 (2011)

Nayfeh, O.M., Chleirigh, C.N., Hennessy, J., Gomez, L., Hoyt, J.L., Antoniadis, D.A.: Design of tunneling field-effect transistors using strained-silicon/strained-germanium type-II staggered heterojunctions. IEEE Electron Device Lett. 29(9), 1074–1077 (2008)

Vimala, P., Arun Samuel, T.S., Nirmal, D., Panda, A.K.: Performance enhancement of triple material double gate TFET with heterojunction and heterodielectric. Solid State Electron. Lett. 1(2), 64–72 (2019)

Bhuwalka, K.K., Schulze, J., Eisele, I.: Scaling the vertical tunnel FET with tunnel band gap modulation and gate work function engineering. IEEE Trans. Electron Devices 52(5), 909–917 (2005)

He, G., Atwater, H.A.: Interband transitions in SnxGe1−x alloys. Phys. Rev. Lett. 79, 1937–1940 (1997)

Bauer, M., Taraci, J., Tolle, J., Chizmeshya, A.V.G., Zollner, S., Smith, D.J., Menendez, J., Hu, C., Kouvetakis, J.: Ge–Sn semiconductors for band-gap and lattice engineering. Appl. Phys. Lett. 81(1–3), 2992 (2002)

D’Costa, V.R., Cook, C.S., Birdwell, A.G., Littler, C.L., Canonico, M., Zollner, S., Kouvetakis, J., Menendez, J.: Optical critical points of thin-film Ge1−ySny alloys: a comparative Ge1−ySny/Ge1−xSix study. Phys. Rev. B. 73(1–16), 125207 (2006)

Roucka, R., Xie, J., Kouvetakis, J., Mathews, J., D’Costa, V., Menendez, J., Tolle, J., Yu, S.Q.: Ge1−ySny photoconductor structures at 1.55 μm: from advanced materials to prototype devices. J. Vac. Sci. Technol. B 26, 1952–1959 (2008)

Chizmeshy, A.V.G., Ritter, C., Tolle, J., Cook, C., Menendez, J., Kouvetakis, J.: Fundamental studies of P(GeH3)3, As(GeH3)3, and Sb(GeH3)3: practical n-dopants for new group IV semiconductors. Chem. Mater. 18, 6266–6277 (2006)

Menendez, J., Kouvetakis, J.: Type-I Ge/GeSiSn strained layer heterostructures with a direct Ge band gap. Appl. Phys. Lett. 85, 175–1178 (2004)

Basu, P.K., Mukhopadhyay, B., Basu, R.: Semiconductor laser theory. CRC Press, Boca Raton (2015)

Jiang, L., Gallagher, J.D., Senaratne, C.L., Aoki, T., Mathews, J., Kouvetakis, J., Menendez, J.: Compositional dependence of the direct and indirect band gaps in Ge1_ySny alloys from room temperature photoluminescence: implications for the indirect to direct gap crossover in intrinsic and n-type materials. Semicond. Sci. Technol. 29, 115028 (2014)

Dutt, B., Lin, H., Sukhdeo, D.S., Vulovic, B.M., Gupta, S., Nam, D., Saraswat, K.C., Harris Jr., J.S.: Theoretical analysis of GeSn alloys as a gain medium for a Si-compatible laser. IEEE J. Sel. Top. Quant. Electron. 19, 1502706 (2013)

Dey, S., Mukhopadhyay, B., Sen, G., Basu, P.K.: Type II band alignment in Ge1−x−ySixSny/Ge1−α−βSiαSnβ heterojunctions. Solid State Commun. 270, 155–159 (2018)

Wang, L., Yu, E., Taur, Y., Asbeck, P.: Design of tunneling field effect transistors based on staggered heterojunctions for ultra-low power applications. IEEE Electron Device Lett. 31(5), 431–433 (2010)

Wang, H., Han, G., Liu, Y., Hu, S., Zhang, C., Zhang, J., Hao, Y.: Theoretical investigation of performance enhancement in GeSn/SiGeSn type-II staggered heterojunction tunneling FET. IEEE Trans. Electron Devices 63(1), 303–310 (2016)

Kane, E.O.: Zener tunneling in semiconductors. J. Phys. Chem. Solids 12(2), 181–188 (1960)

Kane, E.O.: Theory of tunneling. J. Appl. Phys. 32(1), 83–91 (1961)

Bardon, M.G., Neves, H.P., Puers, R., Hoof, C.V.: Pseudo-two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans. Electron Devices 57(4), 827–834 (2010)

Chuang, S.L.: Physics of photonic devices. Wiley, Hoboken (2009)

Chang, G.-E., Chang, S.-W., Chuang, S.L.: Strain-balanced GezSn1−z−xSix/GeySn1−x−y multiple-quantum-well lasers. IEEE J Quantum Electron 46(12), 1813–1820 (2010)

Chandrasekhar, M., Pollak, F.H.: Phys. Rev. B 15, 2127 (1977)

Van de Walle, C.G.: Band lineups and deformation potentials in the model-solid theory. Phys. Rev. B 39, 1871 (1989)

Garg, Shelly, Saurabh, Sneh: Suppression of ambipolar current in tunnel FETs using drain pocket: proposal and analysis, superlattices and microstructures. Elsevier, Amsterdam (2017)

Shaw, N., Sen, G., Mukhopadhyay, B.: An analytical approach of elimination of ambipolarity of DPDG- TFET using strained type II staggered SiGeSn heterostructure. Superlattices Microstruct. 141, 106488 (2020). https://doi.org/10.1016/j.spmi.2020.106488

Wan, J., Le Royer, C., Zaslavsky, A., Cristoloveanu, S.: Gate-induced drain leakage in FD-SOI devices: what the TFET teaches us about the MOSFET. Microelectron. Eng. 88(7), 1301–1304 (2011)

Liu, X., Hu, H., Wang, M., Miao, Y., Han, G., Wang, B.: Design and theoretical calculation of novel GeSn fully-depleted n-tunneling FET with quantum confinement model for suppression on GIDL effect. Superlattices Microstruct. 118, 266–274 (2018)

Bouhdada, A., Bakkalli, S., Touhami, A.: Modeling of gate induced drain leakage in relation to technological parameters and temperature. Microelectron. Reliabil. 37, 649–652 (1997)

Acknowledgements

The authors thank Prof. Sudakshina Kundu, Ex- Professor, Maulana Abul Kalam Azad University of Technology, West Bengal and Dr. Anirban Bhattacharyya, Assistant Professor, Institute of Radio Physics and Electronics, University of Calcutta for providing insight and expertise that greatly helped in the research.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflicts of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Shaw, N., Mukhopadhyay, B. & Sen, G. Study of the electrical parameters of a dual-material double-gate TFET using a strained type II staggered Ge1−x−ySixSny/Ge1−a−bSiaSnb heterojunction. J Comput Electron 19, 1433–1443 (2020). https://doi.org/10.1007/s10825-020-01540-3

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01540-3