Abstract

A new two-dimensional analytical model is proposed for the electrical attributes of a gate-all-around heterojunction tunnel field-effect transistor, including the potential distribution, lateral and vertical electric fields, drain current, subthreshold swing, and threshold voltage. The potential distribution in the device is obtained by using the two-dimensional (2-D) Poisson equation, including the depletion regions across the source–channel, channel, and drain–channel regions. The drain current of the proposed device is derived by combining parameters such as the band-to-band generation rate, lateral electric field, and channel thickness as well as the shortest tunneling path in Kane’s model. The threshold voltage is obtained from the second derivative of the drain current. The effects of the depletion regions are also included in the model to obtain accurate results. The results are validated against ATLAS technology computer-aided design (TCAD) simulations with the SILVACO tool, revealing excellent agreement.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In complementary metal–oxide–semiconductor (CMOS) technology, the tunneling field-effect transistor has attracted enormous attention from researchers due to its excellent electrical characteristics such as low subthreshold swing (i.e., less than 60 mV/dec) and high ON/OFF current ratio with low OFF leakage current [1,2,3,4,5,6,7]. Due to their low OFF leakage current, tunnel FETs are excellent devices for use in low-power very large-scale integration (VLSI) applications [8]. However, two-dimensional tunnel FETs provide a low ON current due to the poor efficiency of the band-to-band tunneling (BTBT) mechanism, because of the wide bandgap in the device. In current semiconductor technology, gate-all-around nanowire (GAANW) tunnel FETs are considered as alternate devices to improve the ON current and reduce the subthreshold swing (SS). The greatest advantage of nanowire tunnel FETs is their excellent gate control over the channel, due to which short-channel effects are greatly reduced. Recently, many studies related to fabrication methods and process technology for nanowire tunnel FETs have been published [9,10,11,12,13,14].

An analytical model to obtain the drain current of a gate-all-around nanowire tunnel FET was proposed by Lu and Seabaugh [14]. However, that model did not include the differences caused in the drain current when the drain-to-source voltage applied to the device is varied. Various analytical models for homojunction tunnel FETs with different structures have also been proposed by researchers with the aim of enhancing the drain current characteristics. Vishnoi and Kumar proposed an analytical model for a gate-all-around nanowire tunnel FET by segregating two regions across the source and channel. However, the variations of the drain region are not account for in their model [15]. Reza et al. suggested an analytical model for a homojunction cylindrical gate-all-around tunnel FET using the superposition principle, but their work did not include the threshold voltage of the device [16]. Bagga and Dasgupta introduced an analytical model to study the surface potential and drain current of a gate-all-around (GAA) triple-metal tunnel FET by solving the Poisson equation using a parabolic approximation and applying Kane’s model for the drain current. Again in this model, only the surface potential, electric field, and drain current are obtained, whereas other important factors that determine the performance of a tunnel FET such as the subthreshold swing and threshold voltage are not explored [17, 18].

Very few studies discussing the schematic cross section of and simulation methods for heterojunction tunnel FETs are available in literature. Kumar et al. proposed a model for schematic double-gate heterojunction TFETs with germanium in the source and silicon in the drain in both the accumulation/inversion and depletion modes [19]. The forward gain is high while the reverse gain is low for heterojunction devices in comparison with homojunction transistors, which enables them to offer high-frequency performance. Moreover, the bandgap in a heterojunction device can be adjusted depending on the application, indicating that SiGe junctions enable more bandgap tuning than silicon-only technology.

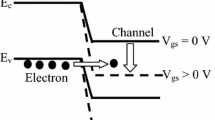

A heterojunction (HJ) is formed in a GAA-HJTFET when two semiconductors (germanium and silicon) with dissimilar bandgaps are placed in conjunction or layered together. The conduction-band energy and valence-band energy change abruptly at the heterojunction. The magnitude of these changes determines the band alignment and the effective bandgap in the semiconductor heterojunction. Due to this, the ON-state current performance improves, short-channel effects are reduced, and a subthreshold swing below 45 mV/dec can be obtained.

In the Si–Ge heterojunction, the energy band of the device moves downwards to the intrinsic region, which improves the ION current and also suppresses the ambipolar behavior, thereby reducing the subthreshold swing. Researchers have demonstrated that increasing the Ge concentration in such devices from 7% to 25% can increase the drain current by 15-fold at a constant subthreshold slope and also decrease the IOFF current.

An analytical model for a heterojunction gate-all-around tunnel FET is presented herein. The surface potential is modeled across the three regions of the proposed device, viz. the source–channel depletion region, channel depletion region and channel–drain depletion region. Differentiation of the surface potential results in the electric field. The drain current is modeled using Kane’s model. The results of the model are validated against ATLAS-based TCAD simulations.

2 Device structure

Figure 1a shows a three-dimensional (3-D) structural view of the GAA-HJTFET. The assumptions of the model include a source length of 20 nm with germanium material having a doping concentration of \(N_{1} = 1 \times 10^{20} \,{\text{cm}}^{ - 3}\), a channel length of 50 nm with a doping concentration of \(N_{2} = 1 \times 10^{16} \,{\text{cm}}^{ - 3}\), and a drain length of 20 nm with silicon material having a doping concentration of \(N_{3} = 5 \times 10^{18} \,{\text{cm}}^{ - 3}\). Figure 1b shows a cross-sectional schematic view of the GAA-HJTFET device. The potential distribution along the radius is similar to that in the y-direction for a double-gate (DG)-TFET. Thus, this cross-sectional schematic view is considered in the analytical model, considering the source–channel (R1), channel (R2), and drain–channel (R3) depletion regions with lengths of \(L_{1}\), \(L_{2}\), and \(L_{3}\), respectively.

3 Model formulation

The cross-sectional schematic view of the GAA-HJTFET shown in Fig. 1b is considered for the analytical modeling. The z- and r-axes represent the coordinates of the device, with the following parameters: silicon thickness (tSi) and channel oxide thickness (tox). \(\psi_{0}\), \(\psi_{1}\), \(\psi_{2}\), and \(\psi_{3}\) are the junction potentials at \(z = 0\,,\,\)\(z_{1} = L_{1} ,\,\)\(z_{2} = L_{1} + L_{2}\), and \(z_{3} = L_{1} + L_{2} + L_{3}\), respectively.

3.1 The analytical modeling of the surface potential

Let \(\psi_{i} (r,z)\) be the surface potential distribution function along channel region Ri, where i = 1, 2, or 3. The two-dimensional (2-D) Poisson’s equation is given as

where q is the electron charge and \(N_{i}\) is the doping concentration of each region. The doping concentration of the source region is assumed to be \(N_{1} = 1 \times 10^{20} \,{\text{cm}}^{ - 3}\), that of the channel region to be \(N_{2} = 1 \times 10^{16} \,{\text{cm}}^{ - 3}\), and that of the drain region to be \(N_{3} = 5 \times 10^{18} \,{\text{cm}}^{ - 3}\). Using a parabolic approximation, the 2-D channel potential \(\psi_{i} (r,z)\) in region Ri can be expressed as

where \(a_{0i} (z),\,\,a_{1i} (z)\) and \(a_{3i} (z)\) are arbitrary functions of z, defined by the boundary conditions [15]

The potential for regions R1, R2, and R3 at r = R equals the surface potential. The electric field at the center of the channel region is zero:

The electric field distribution at r = R is equal across the boundary between the silicon substrate and SiO2 oxide, being given by

where \(\psi_{\rm G} = V_{\text{GS}} - \varphi_{\rm m} + \chi + \frac{{E_{\rm g} }}{2}\) and i = 1, 2, 3 for the three different depletion regions, the gate work function \(\varphi_{\rm m}\) is 4 eV, the electron affinity of silicon is given by \(\chi\) = 4.05 eV, the oxide capacitance is \(C_{\text{ox}}^{'} = \varepsilon_{\text{ox}} /t\), \(V_{\text{GS}}\) is the gate-to-source voltage, \(t = t_{\text{ox}}\) is for region R2, and \(t = \left( {{\raise0.7ex\hbox{$\pi $} \!\mathord{\left/ {\vphantom {\pi 2}}\right.\kern-0pt} \!\lower0.7ex\hbox{$2$}}} \right)t_{\text{ox}}\) for regions R1 and R3. The radius of the channel is R = \(t_{\text{Si}}\).

Using Eqs. (3)–(5) to solve Eq. (2) yields

The relationship between the surface potential and channel potential \(\psi_{i} (r,z)\) is defined by \(\psi_{{\rm s},i} (z) = \psi_{i} \left( {{{ \pm t_{\text{Si}} } \mathord{\left/ {\vphantom {{ \pm t_{\text{Si}} } 2}} \right. \kern-0pt} 2},z} \right).\)

From Eqs. (6)–(8), it can be deduced that

where

At \(r = 0\), the 2-D Poisson Eq. (1) can be written as

Substituting Eq. (2) into Eq. (11) yields the following differential equation in terms of the center potential:

where \(P_{i} = \frac{{qN_{i} }}{{\eta_{i}^{2} \varepsilon_{\rm Si} }} + \psi_{\rm G}\) and \(\eta_{i}^{2} = \frac{4}{{\lambda^{2} R^{2} }}.\).

The general solution of Eq. (12) is

where

The length of region \(R_{i}\) is \(L_{i} = z_{i} - z_{i - 1}\) (i = 1, 2, 3) and the surface potential at \(z_{{}} = z_{i}\) is \(\psi_{i} = \psi_{{\rm s},i} (z_{i} )\) as shown in Fig. 1b. The surface potential across the regions can be obtained by using the following boundary conditions [18, 20]:

where

is the built-in potential. The electron charge is q, \(V_{\rm T}\) is the thermal voltage, and \(n_{i}\) is the electron concentration.

\(\psi_{1}\) and \(\psi_{2}\) are intermediate surface potentials obtained by using the continuity property of the lateral electric field thus [18]:

Using Eqs. (20)–(21) in (10) along with Eqs. (13)–(15) yields the intermediate potentials as

where

3.2 The modeling of the electric field

The vertical and lateral electric fields \(E_{ri} (r,z)\) and \(E_{zi} (r,z)\) are obtained by differentiation of the potential in Eqs. (2) and (13) thus:

3.3 The lengths of the depletion regions

\(L_{1}\) and \(L_{3}\) are determined as the lengths of the regions R1 and R3 that occur due to the source and drain charge depletion regions. A TFET can be considered to be a gate diode whose potential can be regulated by its gate voltage [4]. To consider the impact of the two terminals on each other, \(L_{1}\) and \(L_{3}\) should be calculated by applying \(E_{r} = 0\) at \(r = r_{0}\) and \(r = r_{2}\) before deriving the potentials \(\psi_{2}\) and \(\psi_{3}\). To avoid the complexity of this calculation, a simple approximation is made by considering the source–channel and drain–channel regions separately using Refs. [18, 21] as follows:

Since \(P_{2}\) is dependent on \(V_{\rm GS}\), the \(L_{1}\) and \(L_{3}\) values are smaller than for the DG-TFET. Because of these smaller depletion lengths, the conduction of the device improves while the drain current is simultaneously increased.

3.4 The modeling of the drain current

Based on Kane’s model [21], the drain current of the device is determined from the band-to-band generation rate in the device volume [18] as

where \(A_{\text{Kane}} = 4 \times 10^{14} \,{\text{cm}}^{1/2} \,{\text{V}}^{ - 5/2} \,{\text{s}}^{ - 1}\) and \(B_{\text{Kane}} = 1.9 \times 10^{7} \,{\text{V/cm}}\) are Kane’s constant parameters. \(E_{\text{avg}} = {{E_{\rm g} } \mathord{\left/ {\vphantom {{E_{\rm g} } {ql_{\text{path}} }}} \right. \kern-0pt} {ql_{\text{path}} }}\) is the average electric field [18]. \(l_{\text{path}}\) is the tunneling path distance, from the shortest tunneling path distance \(L_{\hbox{min} }\) to the largest tunneling path distance \(L_{\hbox{max} }\), \(E_{z2} (r,z)\) is the lateral electric field in channel region R2. For indirect-bandgap materials, the material constant \(\alpha\) is 2.5, while for direct-bandgap materials the value tends to be 2. The surface potential changes by \({{E_{\rm g} } \mathord{\left/ {\vphantom {{E_{\rm g} } q}} \right. \kern-0pt} q}\) (unit bandgap potential) [22] when the charges tunnel over the tunneling distance from z = 0 to z = \(L_{\hbox{min} }\) in the channel region, which is denoted as the shortest tunneling path distance \(L_{\hbox{min} }\). This equation can thus [18] be written as

Equation (10) then yields

where

Substituting Eq. (23) with i = 2 into Eq. (30), the drain current after integration is given by

where

is the direct-current (DC) component

The variation of \({1 \mathord{\left/ {\vphantom {1 {z^{\alpha - 1} }}} \right. \kern-0pt} {z^{\alpha - 1} }}\) within the interval \(L_{\hbox{min} } \le z \le L_{\hbox{max} }\) is negligible compared with the exponential term [22]. Since the drain current cannot be expressed in closed form, Eq. (32) can be approximated as [18, 22]

where \(M_{z}\) and \(N_{z}\) are expressed as

Note that \(M_{{L_{\hbox{max} } }}\) ≪ \(M_{{L_{\hbox{min} } }}\) and \(N_{{L_{\hbox{max} } }}\) ≪ \(N_{{L_{\hbox{min} } }}\), since \(L_{\hbox{max} }\) > \(L_{\hbox{min} }\). Thus, the drain current can be further approximated as [18]

3.5 The threshold voltage using the SD method

Among the various methods available for extracting the threshold voltage, the transconductance extrapolation method (GMLE) and second-derivative (SD) method have been proved to provide accurate and more practical results [23]. The gate voltage applied to the device at which its transconductance \(g_{\rm m}^{'}\) reaches the maximum value is defined as the threshold voltage (Vth) [22, 23]:

where \(g_{\rm m}\) is the transconductance, obtained as

3.6 The threshold voltage using the minimum channel potential method

The minimum surface potential distribution along the channel region can be obtained as

For the threshold condition [24], this gives

and

Using Eqs. (40) and (41), a quadratic approximation for the threshold voltage can be obtained as [21]

4 Results and discussion

In this section, the results obtained using the proposed analytical model for the GAA-HJTFET are validated against ATLAS TCAD-based simulation data. Germanium (Ge) is employed at the source. Aluminum with a work function of \(\varphi_{\rm m}\) = 4.05 eV is used as the gate metal, and the results are compared with a homojunction GAA TFET. The variation of the surface potential across the three regions, viz. the source–channel, channel, and drain–channel regions, for different ramping gate voltages is shown in Fig. 2. The sharp changes at the source–channel are due to the high band-tuning property of the heterojunction Si–Ge material, which remains constant across the entire channel region. As the gate-to-source voltage is increased, the potential across the entire channel region (including the source and drain junctions) also shoots up. For a considerable increase in the gate-to-source voltage, the source depletion region R1 extends out towards the source, whereas the drain depletion region R3 is shortened due to the variations on the higher and lower sides of the reverse-bias voltages at the source–channel and drain–channel junctions.

Figure 3 shows the variation of the surface potential for diverse drain-to-source voltages VDS, in which the channel potential is the same and the device is found to vary little, barring the drain depletion region R3. This variation across the drain implies a reduced drain-induced barrier lowering (DIBL) effect, as it is nearly independent of VDS. The variation of the lateral (Ez) and vertical (Er) electric field in the channel region compared with that of the homojunction GAA TFET is shown in Fig. 4.

Due to the smaller values of \(L_{1}\) and \(L_{3}\), a higher lateral electric field is obtained in the tunneling region. It is observed that the homojunction GAA TFET shows a peak magnitude variation at both the source–channel and drain–channel junctions, while the GAA-HJTFET shows a magnitude variation at only the source–channel junction and is nearly zero in the entire channel region. The variation of the drain current compared with the homojunction GAA TFET is shown in Fig. 5, clearly indicating that the threshold voltage is lower while the ON current increases along with the OFF current in the GAA-HJTFET. Figure 6 shows the resulting drain current variation as a function of the gate voltage for different tSi values, revealing an increase in the drain current Id with a decrease in tSi due to the significant band-to-band tunneling of electrons from the valance to conduction band of the channel; the decrease in the drain current with an increase in tSi reduces the shortest tunneling path length Lmin.

The variation of the drain current Id as a function of the drain-to-source voltage VDS is shown in Fig. 7 for different VGS values, clearly indicating that an increase in the gate voltage will increase the drain current Id as a result of the decreasing barrier height, which further increases the movement of added electrons from the source to channel.

Figure 8 shows the resulting variation of the drain current as a function of the drain-to-source voltage VDS for different channel thicknesses. An increase in tSi decreases the drain current Id due to the reduced tunneling volume. Figure 9 shows the transconductance plot for different channel thicknesses with VGS = 1 V and L = 50 nm. The peak value at the drain junction can be attributed to the increase in the shortest tunneling path Lmin. Figure 10 shows a comparison of the drain current, the transconductance, and the first derivative of the transconductance with L = 50 nm, VDS = 1 V, and tSi = 15 nm. The dependence of the current on the gate bias changes from quasiexponential to linear with an increase in the gate bias. It is observed that the peak is high for the first derivative of the transconductance due to the decrease in the tunneling volume, which indicates the threshold voltage. Figure 11 demonstrates the extraction of the threshold voltage, where the peak transition at the drain–channel junction is due to the quasiexponential and linear dependence of the drain current Id with the gate voltage VGS. When using the second derivative method for extraction of the threshold voltage, the device in the linear region is sensitive to measurement error and noise. Figure 12 shows the threshold voltage plot along the channel length using the minimum channel potential method, revealing that the threshold voltage increases linearly from the source to channel region until it saturates due to the maximum electric field at the junction. The threshold voltage remains constant along the channel region due to the independence from the gate length for positive voltage. The threshold voltage shift is high for high doping concentration. Figures 11 and 12 show that the threshold voltage obtained by the second derivative method is low compared with that extracted using the minimum channel potential method.

Figure 13 shows the subthreshold swing for different oxide thicknesses; for the proposed device, it is limited to 48 mV/dec, which is less than for a MOSFET device. This plot reveals that the subthreshold swing is constant across the channel length, thus decreasing the DIBT in this device.

5 Conclusions

A 2-D analytical model for the surface potential, electric field, drain current, transconductance, and threshold voltage of a GAA-HJTFET is developed, including the source–channel, channel, and drain–channel depletion regions. The lateral electric field corresponding to the channel depletion is used to calculate the BTBT generation rate analytically and thus extract the drain current. Based on the drain current, the transconductance and threshold voltage are derived, then the threshold voltage is obtained using the quasiexponential and linear dependence of the drain current Id on the gate voltage VGS. The proposed model predicts the characteristics of the GAA-HJTFET for different parameter values to provide insight into the device physics. Validation of the results against simulations reveals good agreement.

References

Kumar, M., Jit, S.: A novel four-terminal ferroelectric tunnel FET for quasi-ideal switch. IEEE Trans. Nanotechnol. 14, 600–602 (2015)

Kumar, M., Jit, S.: Effects of electrostatically doped source/drain and ferroelectric gate oxide on subthreshold swing and impact ionization rate of strained-Si-on-insulator tunnel field-effect transistors. IEEE Trans. Nanotechnol. 14, 597–599 (2015)

Nagavarapu, R., Jhaveri, R., Woo, J.C.S.: The tunnel source (PNPN) n-MOSFET: a novel high-performance transistor. IEEE Trans. Electron Devices 55, 1013–1019 (2008)

Gholizadeh, M., Hosseini, S.E.: A 2-D analytical model for doublegate tunnel FETs. IEEE Trans. Electron Devices 61, 1494–1500 (2014)

Kumar, M.J., Janardhanan, S.: Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60, 3285–3290 (2013)

Saurabh, S., Kumar, M.J.: Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans. Electron Devices 58, 404–410 (2011)

Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28, 743–745 (2007)

Bhuwalka, K.K., Schulze, J., Eisele, I.: Scaling the vertical tunnel FET with tunnel bandgap modulation and gate work function engineering. IEEE Trans. Electron Devices 52, 909–917 (2005)

Lee, M., Jeon, Y., Jung, J.C., Koo, S.M., Kim, S.: Feedback and tunneling operations of a p +-i-n+ silicon nanowire field-effect transistor. Nanotechnology 29, 43 (2018)

Moselund, K.E., Bjork, M.T., Schmid, H., Ghoneim, H., Karg, S., Lortscher, E., Riess, W., Riel, H.: Silicon nanowire tunnel FETs: low-temperature operation and influence of high-gate dielectric. IEEE Trans. Electron Devices 58, 2911–2916 (2011)

Usha, C., Vimala, P.: A tunneling FET exploiting in various structure and different models: a review. Int. Conf. Innov. Inf. Embedded Commun. Syst. 6, 72–76 (2015)

Usha, C., Vimala, P.: Analytical drain current model for fully depleted surrounding gate TFET. J. Nano Res. 55, 75–81 (2018)

Lu, H., Seabaugh, A.: Tunnel field-effect transistors: state-of-the-art. IEEE J. Electron Device Soc. 2, 44–49 (2014)

Vishnoi, R., Kumar, M.J.: Compact analytical drain current model of gate-all-around nanowire tunneling FET. IEEE Trans. Electron Devices 61, 2599–2603 (2014)

Khaveh, H.R.T., Mohammadi, S.: Potential and drain current modeling of gate-all-around tunnel FETs considering the junctions depletion regions and the channel mobile charge carriers. IEEE Trans. Electron Devices 63, 5021–5029 (2016)

Bagga, N., Dasgupta, S.: Surface potential and drain current analytical model of gate all around triple metal TFET. IEEE Trans. Electron Devices 64, 606–613 (2017)

Kumar, S., Singh, K., Goel, E., Singh, B., Kumar, M., Jit, S.: A compact 2-D analytical model for electrical characteristics of double-gate TFETs with SiO2/high-k2 stacked gate-oxide structure. IEEE Trans. Electron Devices 63, 960–968 (2016)

Kumar, S., Singh, K., Chander, S., Goel, E., Singh, P.K., Baral, K.: 2-D analytical drain current model of double-gate heterojunction TFETs with SiO2/HfO2 stacked gate-oxide structure. IEEE Trans. Electron Devices 65, 331–338 (2018)

Zhang, L., Lin, X., He, J., Chan, M.: An analytical charge model for double gate tunnel FETs. IEEE Trans. Electron Devices 59, 3217–3223 (2012)

Bardon, M.G., Neves, H.P., Puers, R., Van Hoof, C.: Pseudo-two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans. Electron Devices 57, 827–834 (2010)

Sze, S.: Physics of Semiconductor Devices. Wiley, New York (1981)

Dash, S., Mishra, G.P.: A new analytical threshold voltage model of cylindrical gate tunnel FET(CG-TFET). Superlattices Microstruct. 86, 211–220 (2015)

Ortiz-Conde, A., Garcia Sanchez, F.J., Liou, J., Cerdeira, A., Estrada, M., Yue, Y.: A review of recent MOSFET threshold voltage extraction methods. Microelectron. Reliab. 42, 583–596 (2002)

Arafat Mahmud, M., Subrina, S.: Two-dimensional analytical model of threshold voltage and drain current of a double-halo gate-stacked triple material double-gate MOSFET. J. Comput. Electron. 15, 525–536 (2016)

Acknowledgement

This work was supported by Women Scientist Scheme-A, Department of Science and Technology, New Delhi, Government of India under grant SR/WOS-A/ET-5/2017.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Usha, C., Vimala, P., Samuel, T.S.A. et al. A novel 2-D analytical model for the electrical characteristics of a gate-all-around heterojunction tunnel field-effect transistor including depletion regions. J Comput Electron 19, 1144–1153 (2020). https://doi.org/10.1007/s10825-020-01503-8

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01503-8